Abstract

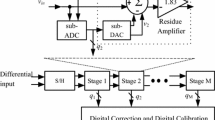

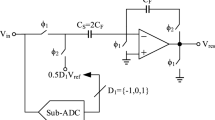

This paper proposes a high-speed deterministic digital technique to calibrate the errors due to capacitance mismatch and finite op-amp gain. Unlike other calibration techniques, this technique requires neither forcing the inputs of the intermediate stages being calibrated to exact voltages, nor reducing the gains of each stage to avoid saturation of output digital codes. A 1.5 bits/stage, 10 stages, 9 bits pipeline ADC with the three most significant stages calibrated is demonstrated in this paper. For a 10% mismatch in capacitances in the 3 MSB stages of the pipelined ADC, the calibration technique improved SNDR by more than 20 dB and SFDR by around 27 dB. The technique can also be slightly modified to calibrate algorithmic ADCs. For a 7% mismatch in capacitances of the algorithmic ADC, the proposed calibration technique improved SNDR by 18 dB and SFDR by around 28 dB.

Similar content being viewed by others

References

A.M. Abo, Design for Reliability of Low-Voltage, Switched-Capacitor Circuits (University of California, Berkley, Electronics Research Laboratory, Berkley, 1999), pp. 81–84

E. Alpman, H. Lakdawala, L.C. Richard, K. Soumyanath, A 1.1V 50mW 2.5GS, s 7b Time-Interleaved C-2C SAR ADC in 45nm LP digital CMOS. , IEEE International Solid-State Circuits Conference—Digest of Technical Papers (CA, USA, San Francisco, 2009)

N. Bako, K. Frick, R. Sobot, A. Baric, An 11-\(\mu \)W, 9-bit fully differential, cyclic/algorithmic ADC in 0.13 \(\mu \)m CMOS. Int. J. Circuit Theory Appl. 45, 1095–1114 (2017)

S.Y. Chuang, T.L. Sculley, A digitally self-calibrating 14-bit 10-MHz CMOS pipelined ADC. IEEE J. Solid-State Circuits 37, 674–683 (2002)

O.E. Erdogan, P.J. Hurst, S.H. Lewis, A 12 b digital-background-calibrated algorithmic ADC with -90 dB THD. IEEE J. Solid-State Circuits 34, 1812–1820 (1999)

M.K. Hati, T.K. Bhattacharyya, An 8-b 250-Msample, s Power Optimized Pipelined AID Converter in O.18-J-Lm CMOS, in 2015 International Conference on VLSI Systems (Architecture, Technology and Applications (VLSI-SATA), Bengaluru, India, 2009)

A.N. Karanicolas, H.S. Lee, K.L. Bacrania, A 15-b 1-Msample/s digitally self-calibrated pipelined ADC. IEEE J. Solid-State Circuits 28, 1207–1215 (1993)

H.-S. Lee, A 12-b 600 ks/s digitally self-calibrated pipelined algorithmic ADC. IEEE J. Solid-State Circuits 29, 839–845 (1994)

F.Y. Li, D. Li, 1.5 bit-per-stage 8-bit Pipelined CMOS A/D Converter for Neuromophic Vision Processor, arXivLabs, Feb (2017)

J. Li, U.-K. Moon, Background calibration techniques for multistage pipelined ADC with digital redundancy. IEEE Trans. Circuits Syst. II: Analog Digit. Signal Process. 50, 531–538 (2003)

P.W. Li, M.J. Chin, R. Castello, A ratio-independent algorithmic analog-to-digital conversion technique. IEEE J. Solid-State Circuits 19, 828–836 (1984)

M.A. Murshed, K.L. Krishna, M.A. Saif, K. Anuradha, A 10-bit high speed pipelined ADC, in 2018 2nd International Conference on Inventive Systems and Control (ICISC) (Coimbatore, India, 2018)

H. Omran, H. Alahmadi, K.N. Salama, Matching properties of femtofarad and sub-femtofarad MOM capacitors. IEEE Trans. Circuits Syst. I 63, 763–772 (2016)

S. Padma, S. Das, S. Sen, C. Parikh, High Performance Operational Amplifier with 90dB Gain in SCL 180nm Technology, in 24th International Symposium on VLSI Design and Test, Bhubaneswar, Argul, India (2020)

C. Ravi, S. Vineeth, B. Sahoo, At Speed Digital Gain Error Calibration of Pipelined ADCs, in Proceedings of the 13th International New Circuits and Systems Conference (NEWCAS), Grenoble, France (2015)

B. Razavi, The StrongARM Latch [A Circuit for All Seasons], 12–17. IEEE Solid-State Circuits Magazine (2015)

P. Rebentrost, M. Schuld, L. Wossnig, F. Petruccione, S. Lloyd, Quantum gradient descent and Newton’s method for constrained polynomial optimization. New J. Phys. 21, 073023 (2019)

B. Sahoo, B. Razavi, A 10-bit 1-GHz 33-mW CMOS ADC. IEEE J. Solid-State Circuits 48, 1442–1452 (2013)

D.S. Shylu, D.J. Moni, A 1.8V 22mW 10 bit 165 MSPS pipelined ADC for video applications. WSEAS Trans. Circuits and Syst. 13, 344–352 (2014)

A.-K. Sylvester, An 8 Bit, 100Ms/s Pipeline ADC with Partial Positive Feedback Amplifier for Cognitive Radio Applications (Texas A and M University, Texas, Electrical Engineering, 2016)

T.-Y. Wang, S.-Y. Peng, J. Hassler, A compact low-power algorithmic A/D converter implemented on a large scale FPAA chip. Analog integrated circuits and signal processing, Springer 94, 65–74 (2018)

X. Wang, P.J. Hurst, S.H. Lewis, A 12-Bit 20-Msample/s pipelined analog-to-digital converter with nested digital background calibration. IEEE J. Solid-State Circuits 39, 1799–1808 (2004)

Acknowledgements

This work was funded by the Indian Space Research Organization (ISRO) under RESPOND program. The authors would like to thank Dr. Hari Shankar Gupta and Ms. Rinku Agarwal from ISRO and Mr. Surya Padma from IIITB for supporting this work. The authors would also like to thank the editors and the reviewers for their constructive feedback that has helped us in improving the quality of the paper. ‘All data generated or analyzed during this study are included in this published article.’

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ramamurthy, C., Parikh, C.D. & Sen, S. Deterministic Digital Calibration Technique for 1.5 bits/stage Pipelined and Algorithmic ADCs with Finite op-amp Gain and Large Capacitance Mismatches. Circuits Syst Signal Process 40, 3684–3702 (2021). https://doi.org/10.1007/s00034-021-01652-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01652-6