Abstract

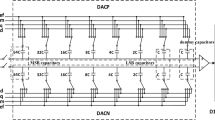

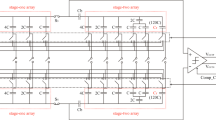

In this paper, a low-energy switching scheme based on the asymmetric binary search algorithm for successive approximation register (SAR) analog-to-digital converters (ADCs) is proposed. To reduce switching energy and area, the proposed scheme uses the single-side switching method and the least significant bit (LSB) capacitor is split into two one-half unit capacitors. Using the series capacitance scheme, the capacitance mismatch caused by process deviation is effectively improved. Compared with the conventional switching method, the switching energy of this scheme is decreased by 99.43% and the area is saved by 87.2%. MATLAB simulation results show that this scheme also has a low nonlinearity that the maximum differential nonlinearity is only 0.37 LSB and the maximum integral nonlinearity is only 0.43 LSB.

Similar content being viewed by others

References

T. Anand, V. Chaturvedi, B. Amrutur, Energy efficient asymmetric binary search switching technique for SAR ADC. Electron. Lett. 46, 1487–1488 (2010)

Y.S. Chen, Y.Q. Zhuang, H.L. Tang, A 99.8% energy-reduced two-stage mixed switching scheme for SAR ADC without reset energy. Circuits Syst. Signal Process. 38, 5426–5447 (2019)

B.P. Ginsburg, A.P. Chandrakasan, An energy-efficient charge recycling approach for a SAR converter with capacitive DAC, in IEEE International Symposium on Circuits and Systems (2005), pp. 184–187

P.Q. Han, N.S. Mei, Z.F. Zhang, Resistorless frequency locked on-chip oscillator with proportional-to-absolute temperature. J. Circuits Syst. Comput. 28, 1950162 (2019)

L. Jian, R.X. Ding, S.B. Liu, Z.M. Zhu, A highly energy-efficient, highly area-efficient capacitance multiplexing switching scheme for SAR ADC. Analog Integr. Circuits Signal Process. 96, 207–215 (2018)

W.Y. Qu, J.Q. Zhao, Z.F. Zhang, N.S. Mei, Low-energy switching method based on asymmetric binary search algorithm for SAR ADCs. J. Circuits Syst. Comput. 29, 2010087 (2019)

X.Y. Tong, Y.W. Chen, Low-power high-linearity switching procedure for charge-redistribution SAR ADC. Circuits Syst. Signal Process. 36, 3825–3834 (2017)

Q.P. Wan, Y.K. Teh, G. Yuan, P.K.T. Mok, Analysis and design of a thermoelectric energy harvesting system with reconfigurable array of thermoelectric generators for IoT applications. IEEE Trans. Circuits Syst. I Regul. Pap. 64, 2346–2358 (2017)

L.B. Xie, S. Jian, J.X. Liu, G.J. Wen, Energy-efficient capacitor-splitting DAC scheme with high accuracy for SAR ADCs. Electron. Lett. 51, 460–462 (2015)

Z. Yan, C.H. Chan, U.F. Chio, S.W. Sin, U. Seng-Pan, R.P. Martins, M. Franco, A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid State Circuits 45, 1111–1121 (2010)

Q.S. Yang, P.Q. Han, N.S. Mei, Z.F. Zhang, A 16.4nW, Sub-1V, resistor-less voltage reference with BJT voltage divider. J. Circuits Syst. Comput. 27, 1850206 (2018)

B. Yazdani, A. Khorami, M. Sharifkhani, Low-power bottom-plate sampling capacitor-splitting DAC for SAR ADCs. Electron. Lett. 52, 913–915 (2016)

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48, 482–483 (2012)

Z.M. Zhu, X. Yu, X.L. Song, VCM-based monotonic capacitor switching scheme for SAR ADC. Electron. Lett. 49, 327–329 (2013)

H.Y. Zhuang, W.J. Guo, J.X. Liu, H. Tang, Z.M. Zhu, L. Chen, N. Sun, A second-order noise-shaping SAR ADC with passive integrator and tri-level voting. IEEE J. Solid State Circuits 54, 1636–1647 (2019)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Qu, W., Zhang, Z. & Mei, N. A 99.43% Energy Saving Switching Scheme with Asymmetric Binary Search Algorithm for SAR ADCs. Circuits Syst Signal Process 39, 4695–4704 (2020). https://doi.org/10.1007/s00034-020-01383-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01383-0