Abstract

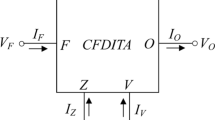

Two grounded capacitance multipliers employing the current differencing transconductance amplifier (CDTA) are proposed. They can be easily modified to the floating versions by using an additional difference voltage amplifier. Each multiplier contains one CDTA, one capacitor, pseudo-grounded via a low-impedance CDTA input terminal, and one or two resistors. A careful error analysis is made and both circuits are compared in terms of their benefits and drawbacks. The results of the measurements on the specimens exploiting on-chip CDTAs correspond to the design objectives.

Similar content being viewed by others

References

M.T. Abuelma’atti, N.A. Tasadduq, Electronically tunable capacitance multiplier and frequency-dependent negative-resistance simulator using the current-controlled current conveyor. Microelectron. J. 30, 869–873 (1999)

C.K. Alexander, M.N.O. Sadiku, Fundamentals of Electric Circuits, 5th edn. (McGraw Hill, New York, 2013), pp. 437–439

H. Alpaslan, DVCC-based floating capacitance multiplier design. Turk. J. Electr. Eng. Comput. Sci. 25, 1334–1345 (2017)

D. Biolek, CDTA—building block for current-mode analog signal processing, in Proceedings of the European Conference on Circuit Theory and Design (ECCTD’03) (Cracow, Poland, 2003), pp. 397–400

D. Biolek, E. Hancioglu, A.Ü. Keskin, High-performance current differencing transconductance amplifier and its application in precision current-mode rectification. AEU Int. J. Electron. Commun. 62, 92–96 (2008)

D. Biolek, A.Ü. Keskin, V. Biolkova, Grounded capacitor current mode single resistance-controlled oscillator using single modified current differencing transconductance amplifier. IET Circ. Devices Syst. 4, 496–502 (2010)

P. Brinzoi, A. Cracan, N. Cojan, A new approach in designing electrically controlled capacitance multipliers, in Proceedings of the 10th International Symposium on Signals, Circuits and Systems (ISSCS 2011) (Iasi, Romania, 2011), pp. 1–4

J. Choi, J. Park, W. Kim, K. Lim, J. Laskar, High multiplication factor capacitor multiplier for an on-chip PLL loop filter. Electron. Lett. 45, 239–240 (2009)

H.Y. Darweesh, F.A. Farag, Y.A. Khalaf, New active capacitance multiplier for low cutoff frequency filter design, in Proceedings of the 19th International Conference on Microelectronics (ICM 2007) (Cairo, Egypt, 2007), pp. 381–384

W.G. Davis, Capacitance multiplier circuit. United States Patent 3, 911, 296 (1975)

A. De Marcellis, G. Ferri, N.C. Guerrini, G. Scotti, V. Stornelli, A. Trifiletti, A novel low-voltage low-power fully differential voltage and current gained CCII for floating impedance simulations. Microelectron. J. 40, 20–25 (2009)

A.A. El-Adawy, A.M. Soliman, H.O. Elwan, A novel fully differential current conveyor and applications for analog VLSI. IEEE Trans. Circuits Syst. II Express Briefs 47, 306–313 (2000)

G. Ferri, S. Pennisi, A 1.5-V current-mode capacitance multiplier, in Proceedings of the 10th International Conference on Microelectronics (ICM’98) (Monastir, Tunisia, 1998), pp. 9–12

I. Hwang, Area-efficient and self-biased capacitor multiplier for on-chip loop filter. Electron. Lett. 42, 1392–1393 (2006)

W. Jaikla, M. Siripruchyanun, An electronically controllable capacitance multiplier with temperature compensation, in Proceedings of International Symposium on Communications and Information Technologies (ISCIT’06) (Bangkok, Thailand, 2006), pp. 356–359

A. Jantakun, N. Pisutthipong, M. Siripruchyanun, Single element based novel temperature insensitive/electronically controllable floating capacitance multiplier and its application, in Proceedings of the International Conference on Electrical Engineering, Electronics, Computer, Telecommunications and Information Technology (ECTI-CON 2010) (Chiang Mai, Thailand, 2010), pp. 37–41

A.Ü. Keskin, D. Biolek, Current mode quadrature oscillator using current differencing transconductance amplifiers (CDTA). IEE Proc Circuits Devices Syst. 153, 214–218 (2006)

A.A. Khan, S. Bimal, K.K. Dey, S.S. Roy, Current conveyor based R- and C-multiplier circuits. AEU Int. J. Electron. Commun. 56, 312–316 (2002)

Z. Kolka, V. Biolkova, D. Biolek, New version of SNAP simulator, in Proceedings of the International Conference Communication and Information Technologies (KIT 2017) (T. Zruby, Slovakia, 2017), pp. 1–4

T. Kulej, Regulated capacitance multiplier in CMOS technology, in Proceedings of 16th International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES’09) (Lodz, Poland, 2009), pp. 316–319

A. Lahiri, DO-CCII based generalized impedance convertor simulates floating inductance, capacitance multiplier and FDNR. Aust. J. Electr. Electron. Eng. 7, 15–19 (2010)

Y. Li, A.K.Y. Wong, Y.T. Zhang, Fully-integrated transimpedance amplifier for photoplethysmographic signal processing with two-stage Miller capacitance multiplier. Electron. Lett. 46, 745–746 (2010)

I. Myderrizi, A. Zeki, Electronically tunable DXCCII-based grounded capacitance multiplier. AEU Int. J. Electron. Commun. 68, 899–906 (2014)

S. Pennisi, CMOS multiplier for grounded capacitors. Electron. Lett. 38, 765–766 (2002)

S. Pennisi, High accuracy CMOS capacitance multiplier, in Proceedings of the 9th International Conference on Electronics, Circuits and Systems (ECS2002) (Dubrovnik, Croatia, 2002), pp. 389–392

P. Prommee, M. Somdunyakanok, CMOS-based current-controlled DDCC and its applications to capacitance multiplier and universal filter. AEU Int. J. Electron. Commun. 65, 1–8 (2011)

G.A. Rincon-Mora, Active capacitor multiplier in Miller-compensated circuits. IEEE J. Solid State Circuits 35, 26–32 (2000)

N.A. Shah, S.Z. Iqbal, M. Quadri, Current-mode first-order all-pass filter using CDTA. Electron. World Wirel. World 111, 48 (2005)

K. Shu, E. Sanchez-Sinencio, J. Silva-Martinez, S.H.K. Embabi, A 2.4-GHz monolithic fractional-N frequency synthesizer with robust phase-switching prescaler and loop capacitance multiplier. IEEE J. Solid State Circuits 38, 866–873 (2003)

P. Silapan, C. Tanaphatsiri, M. Siripruchyanun, Current controlled CCTA based-novel grounded capacitance multiplier with temperature compensation, in Proceedings of the Asia Pacific Conference on Circuits and Systems (APCCAS 2008) (Macao, China, 2008), pp. 1490–1493

M. Siripryuchyanun, W. Jaikla, Floating capacitance multiplier using DVCC and CCCII, in Proceedings of the International Symposium on Communications and Information Technologies (ISCIT’07) (Sydney, Australia, 2007), pp. 218–221

Y. Tang, M. Ismail, S. Bibyk, Adaptive Miller capacitor multiplier for compact on-chip PLL filter. Electron. Lett. 39, 43–45 (2003)

W. Tangsrirat, W. Tanjaroen, Current-mode multiphase sinusoidal oscillator using current differencing transconductance amplifiers. Circuits Syst. Signal Process. 27, 81–93 (2008)

W. Tangsrirat, T. Dumawipata, W. Surakampontorn, Multiple-input single output current-mode multifunction filter using current differencing transconductance amplifiers. AEU Int. J. Electron. Commun. 61, 209–214 (2007)

W. Tangsrirat, T. Pukkalanun, P. Mongkolwai, W. Surakampontorn, Simple current-mode analog multiplier, divider, square-rooter and squarer based on CDTAs. AEU Int. J. Electron. Commun. 65, 198–203 (2011)

J. Vavra, A capacitance multiplier based on DBTA, in Proceedings of the 2017 IEEE Nordic Circuits and Systems Conference (NORCAS 2917) (Linkoping, Sweden, 2017), pp. 1–5

J. Vavra, A grounded capacitance multiplier based on CCII. J. Telecommun. Electron. Comput. Eng. (2018) (in press)

E. Yuce, S. Minaei, A modified CFOA and its applications to simulated inductors, capacitance multipliers, and analog filters. IEEE Trans. Circuits Syst. Regul. Pap. 55, 266–275 (2008)

E. Zadeh, CM circuits and the applications thereof to attenuate row-wise temporal noise in image sensors. United States Patent, 2,008,024,653,9 A1 (2008)

Acknowledgements

For research, the infrastructure of K217 UD Brno was used.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Biolek, D., Vavra, J. & Keskin, A.Ü. CDTA-Based Capacitance Multipliers. Circuits Syst Signal Process 38, 1466–1481 (2019). https://doi.org/10.1007/s00034-018-0929-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0929-y