Abstract

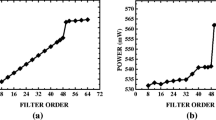

Finite impulse response (FIR) filter is a fundamental element in digital signal processing (DSP) systems. Traditional implementations have been using application specific integrated circuits (ASICs) or DSP processors. However, the increase in logic capacity and versatility of the field programmable gate array (FPGA) platforms has made it possible to realize numerically intense algorithms and thus provide a complete system-on-chip (SoC) solution in a single package. With modern FPGAs fast moving from prototype designing to low and medium volume productions, it becomes imperative to consider architectural optimizations that are specific to FPGAs only. In this paper, for the first time, we attempt to optimize filtering structures by considering the technology-dependent approaches. We present a general procedure that can be used to efficiently map the Boolean networks onto FPGA fabric. Based on this procedure, a technology optimal realization of the multiply-adder unit, which is a fundamental functional unit in FIR filters is presented. Since no such implementation has been reported, we have compared our implementations against the various technology-independent optimizations that have been detailed in prior literature. Further, to give an idea about the performance speed-up achieved with our implementations, we have compared our results against the FIR structures based on the multiply-adder IP v 2.0, inherent in Xilinx FPGAs. A distinctive feature of our implementation is that a simultaneous speed-up is achieved in all three parameters (area, speed and power). This is in contrast to the technology-independent implementations where there is always a performance trade-off between different parameters.

Similar content being viewed by others

References

A. Abedelgwad, High speed and area efficient multiply Accumulate (MAC) Unit for Digital Signal Processing Applications (IEEE International Symposium on Circuits and Systems, ISCAS, 2007)

L. Aksoy, P. Flores, J. Monteiro, A tutorial on multiplier-less design of FIR filters: algorithms and architectures. Circ. Syst. Signal Process. 33, 1689–1719 (2014)

J.H. Anderson, Q. Wang, Area-efficient FPGA logic elements: architecture and synthesis, 16th Asia and South Pacific Design Automation conference (ASP-DAC), (2011)

A. Antonion, Digital Filters: Analysis, Design and Application (McGraw Hill, New York, 1993)

J.E. Carletta, M.D. Rayman, Practical Considerations in the Synthesis of High Performance Digital Filters for Implementation on FPGAs. FPL 2002, LNCS 2438, pp. 886–896, Springer, (2002)

K. Chapman, Constant Coefficient Multipliers for the XC4000E. Xilinx Technical Report (1996)

C. Cheng, K.K. Parhi, Hardware efficient fast parallel FIR filter structures based on iterated short convolution. IEEE Trans. Circ. Syst. I Reg. Pap. 51(8), 1492–1500 (2004)

J. Chou, S. Mohanakrishnan, J.B. Evans, FPGA Implementation of Digital Filters, in Proceedings 4th International Conference on Signal Processing Applications and Technology, (1993)

L. Deng, K. Sobti, Y. Zhang, C. Chakarbarti, Accurate area, time and power models for FPGA based implementations. J. Signal Process. Syst. 63, 39–50 (2011)

A. Fayed, A merged Multiplier Accumulator for High Speed Signal Processing Applications. IEEE International Conference on Acoustics, Speech, and Signal Processing (ICASSP), (2002)

S. Gao, D. Al-Khalili, N. Chabini, Implementation of Large Size Multiplier using Ternary Adders and Higher Order Compressors. International Conference on Microelectronics, (2009)

G.R. Goslin, A Guide to using FPGAs for application-specific DSP performance, in Xilinx application note, (1998)

S. Haykin, Adaptive Filter Theory (Prentice Hall, Upper Saddle River, 1991)

M.K. Jaiswal, R.C.C. Cheung, Area-efficient architectures for double precision multiplier on FPGA, with run-time-reconfigurable dual single precision support. Microelectron. J. 44, 421–430 (2013)

H.M. Kamboh, S.A. Khan, An Algorithmic Transformation for FPGA Implementation of High Throughput Filters, in Proceedings of the 7th International Conference on Emerging Technologies, (2011)

S. Kestur, J.D. Davis, O. Williams, BLAS Comparison on FPGA, CPU and GPU, in IEEE Annual Symposium on VLSI, pp. 288–293, (2010)

P. Kolling, K. Abbot, FPGA Implementation of High Performance FIR filter, Proceedings IEEE International Symposium on Circuits and Systems, ISCAS, (1997)

M. Kumm, M. Hardieck, J. Wilkomm, P. Zipf, U.M. Baese, Multiple Constant Multiplication with Ternary Adders, \(23^{\text{ rd }}\) International conference on Field Programmable Logic and Applications, (2013)

A. Ling, D.P. Singh, S.D. Brown, FPGA Technology Mapping: A Study of Optimality, in IEEE Proceedings Design Automation Conference, pp. 427–432, (2005)

P.K. Meher, Low-Latency Hardware-Efficient Memory-Based Design for Large Order FIR Digital Filters, 6th International Conference on Information, Communication and Signal Processing, pp. 10–13 (2007)

P.K. Meher, S. Chanderasekaran, A. Amira, FPGA Realization of FIR Filters by Efficient and Flexible Systolization using Distributed Arithmetic. IEEE Transactions on Signal Processing, vol. 56, No. 7, (2008)

A. Mirshekari, M. Mosleh, Hardware Implementation of a Fast FIR Filter with Residue Number System, 2nd International conference on Industrial Mechatronics and Automation, pp 312–315, 30–31 (2010)

N. Mu, G. Liu, Study on the FPGA Implementation Algorithm of Effective FIR Filter Based on Remainder Theorem, 2nd International Conference on Consumer Electronics, Communication and Networks, pp. 21–23 (2012)

R. Naseer, M. Balakrishnan, A. Kumar, Direct Mapping of RTL Structures onto LUT-Based FPGAs, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 17, No. 7, (1998)

M. Nikolic, M. Lutovac, Sharpening of the multistage modified comb filters. Serbian J. Electric. Eng. 8(3), 281–291 (2011)

B. Parhami, Computer Arithmetic Algorithms and Hardware Designs (Oxford University Press, New York, 2000)

K.K. Parhi, Chapter 13, Bit-Level Arithmetic Architectures. VLSI Digital Signal Processing Systems Design and Implementation (Wiley, 1999)

V.D. Pavlovic, N. Doncov, D. Ciric, 1D and 2D Economical FIR filters generated by Chebyshev polynomials of the first kind. Int. J. Electronic. (2013)

A. Perwaiz, S.A. Khan, H.M. Kamboh, Optimization for quantization & embedded resources on FPGA. Proc. Int. Conf. Emerg. Technol. (2011)

J.G. Proakis, D.G. Manolakis, Digital Signal Processing: Principles, Algorithms and Applications (Prentice Hall, Upper Saddle River, 1996)

P. Shi, Y.J. Yu, Design of linear phase FIR filters with high probability of achieving minimum number of adders. IEEE Circ. Syst. Soc. 58(1), 126–136 (2011)

G. Stitt, F. Vahid, S. Nematbakhsh, Energy savings and speed-ups from partitioning critical software loops to hardware in embedded systems. ACM Trans. Embed. Comput. Syst. 3(1), 218–232 (2004)

R. Tessier, W. Burleson, Reconfigurable computing for DSP: a survey. J. VLSI Signal Process. 28, 7–27 (2001)

T.J. Todman, G.A. Constantinides, S.J.E. Wilton, O. Mencer, W. Luk, P.Y.K. Cheung, Reconfigurable Computing: Architecture and Design Methods. in IEEE Proceedings. Computer Digital Technology, vol. 152, No. 2, (2005)

Y.C. Tsao, K. Choi, Area efficient parallel FIR digital filter structures for symmetric convolutions based on fast FIR algorithm. IEEE Trans. VLSI Syst. 20(2), 366–371 (2010)

Y.C. Tsao, K. Choi, Area efficient VLSI implementation for parallel linear-phase FIR digital filters of odd length based on fast FIR algorithm. IEEE Trans. Circ. Syst.-II Express Briefs 59(6), 371–375 (2012)

Y.C. Tsao, K. Choi, Hardware-Efficient VLSI Implementation for 3-Parallel Linear-Phase FIR Digital Filters of Odd Length. IEEE International Symposium on Circuits and Systems, Seoul, (2012)

R. Uma, J. Ponnian, Systolic FIR Filter Design with Various Parallel Prefix Adders in FPGA: Performance Analysis. International Symposium on Electronic System Design, Kolkatta, 19–22 (2012)

G. Wei, W.F. Ying, The Implementation of FIR Low-Pass Filter Based on FPGA and DA. 4th International Conference on Intelligent Control and Information Processing, Beijing, China, (2013)

M.J. Wirthlin, Constant coefficient multiplication using look-up tables. J. VLSI Signal Process. 36, 7–15 (2004)

M.J. Wirthlin, B. McMurtrey, Efficient Constant Coefficient Multiplication Using Advanced FPGA Architectures. International Conference on Field Programmable Logic and Applications (FPL), (2001)

R. Woods, J. McAllister, G. Lightbody, Y. Yi, FPGA-based Implementation of Signal Processing Systems, (Wiley, New York, 2008)

R. Woods, S. Ludwig, J. Heron, D. Trainor, S. Gehring, FPGA Synthesis on the XC6200 using IRIS and Trianus/Hades. Proceedings 5th IEEE Symposium on FPGA based Custom Computing Machines, pp. 155–164, (1997)

Xilinx, Spartan-6 Family Overview. DS160 (v 2.0) (October 25, 2011). www.xilinx.com

Xilinx, “Virtex-5 Family Overview,” DS100 (v 5.0) (Feb. 6, 2009). www.xilinx.com

Xilinx, Virtex-6 Libraries Guide for HDL Designs, UG623 (v 12.3) (September 21, 2010). www.xilinx.com

X. Yuan, T. Ying, G. Chunpeng, Improved Design of Multiplier in the Digital Filter. International Conference on Computer and Communication Technologies in Agriculture Engineering, (2010)

L. Zhao, W.H. Bi, F. Liu, Design of digital FIR band pass filter using distributed algorithm based on FPGA. Electron. Meas. Technol. 30(7), 101–104 (2010)

Y. Zhon, P. Shi, Distributed Arithmetic for FIR Implementation on FPGA. International Conference on Multimedia Technology, Hangzhou, China, (2011)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Khurshid, B., Mir, R.N. An Efficient FIR Filter Structure Based on Technology-Optimized Multiply-Adder Unit Targeting LUT-Based FPGAs. Circuits Syst Signal Process 36, 600–639 (2017). https://doi.org/10.1007/s00034-016-0312-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-016-0312-9