Abstract

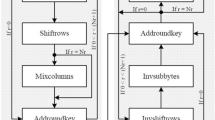

Reconfigurable computing has grown to become an important and large field of research, it offers advantages over traditional hardware and software implementations of computational algorithms. The Advanced Encryption Standard (AES) algorithm is widely applied in government department and commerce. This paper analyzed the AES algorithms with different cipher keys, adopted a novel key scheduler that generated the round key real—time, proposed a dynamically reconfigurable encryption system which supported the AES algorithm with different cipher keys, and designed the architecture of the reconfigurable system. The dynamically reconfigurable AES system had been realized on FPGA. The result proves that the reconfigurable AES system is flexible, lower cost and high security level.

Similar content being viewed by others

References

Xiao Guozhen, Bai Enjian, Liu Xiaojuan. Some New Developments on the Cryptanalysis of AES[J].Acta Electronica Sinica, 200331(10):1549–1554(Ch).

Su Chihpin Horng Chialung, Huang Chihtsun,et al. A Configurable AES Processor for Enhanced Security [C]//Asia and South Pacific Design Automation Conference. Shanghai, IEEE Press 2005:361–366.

Huang Xiaoyuan, Dai Zibin. Design of FPGA Implementation of AES Algorithm Chip [J].Microelectronics and Computer, 2005,28:62–68(Ch).

Zhang Xinmiao, Psrhhi K K. High-speed VLSI Architectures for the AES Algorithm[J].IEEE Transaction on very Large Scale Integration (VLSI) Systems. 200512:957–967.

Wang S S, Ni W S. An Efficient FPGA Implementation of Advanced Encryption Standard Algorithm[C]//Proceedings of the 2004 International Symposium on Circuits and Systems. Chengdu: IEEE Press, 2004:597–600.

Fu Yongzhi, Hao Lin, Zhang Xuejie,et al. Design of An Extremely High Performance Counter Mode AES Reconfigurable Processor [C]//Second International Conference on Embedded Software and Systems. Scottsdale, USA: IEEE Press, 2005:262–268.

Brokalakis A Kakarountas A P, Goutis C. A High-Throughput Area Efficient FPGA Implementation of AES-128 Encryption[C]//IEEE Workshop on Signal Processing System Design and Implementation. Athens, Greece: IEEE Press, 2005:116–121.

Wang Jingfa, Chang Sunwei, Lin Pochuan. A Novel Round Function Architecture, for AES Encryption/Decryption Utilizing Look-up Table[C]//IEEE 37th Annual 2003 International Carnahan Conference on Security Technology. Taipei: IEEE Press, 2003:132–136.

Hsiao S F, Chen, M C. Two Efficient Area Reduction Methods for Implementations of the Rijndael Advanced Encryption Standard[C]//The 2004 IEEE Asia-Pacific Conference on Circuits and System. Fukuoka, Japan, IEEE Press, 2004, 1:353–356.

Lai Y K, Chang L C, Chen L F,et al. A Novel Memoryless AES Cipher Architecture for Networking Applications[C]//Proceedings of the 2004 International Symposium on Circuit and System. Vancouver, Canada: IEEE Press 2004:23–26.

Kotturi D, Yoo S M, Blizzard J. AES Crypto Chip Utilizing High-Speed Parallel Pipelined Architecture[C]//IEEE 2005 International Symposium on Circuits and Systems. Tokyo, Japan: IEEE Press, 2005:4653–4656.

Author information

Authors and Affiliations

Corresponding author

Additional information

Foundation item: Supported by the National Natural Science Foundation of China (60374008)

Biography: WANG Youren (1963-), male, Professor, Ph. D., research direction: bio-inspired hardware, intelligent, testing and self-repairing of electronic equipments.

Rights and permissions

About this article

Cite this article

Youren, W., Li, W., Rui, Y. et al. Dynamically reconfigurable encryption system of the AES. Wuhan Univ. J. Nat. Sci. 11, 1569–1572 (2006). https://doi.org/10.1007/BF02831822

Received:

Issue Date:

DOI: https://doi.org/10.1007/BF02831822

Key words

- dynamically reconfigurable hardware

- field programmable gate array (FPGA)

- advanced encryption standard (AES) algorithm

- cipher key