Abstract

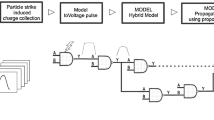

In this article, an automatic test pattern generation technique using neural network models for stuck-open faults in CMOS combinational circuits is presented. For a gate level fault model of stuck-open faults in CMOS circuits, SR(slow-rise) and SF(slow-fall) gate transition faults we develop a neural network representation. A neural network computation technique for generating robust test patterns for stuck-open faults is given. The main result is extending previous efforts in stuck-at test pattern generation to stuck-open test pattern generation using neural network models. A second result is an extension of the technique to robust test pattern generation.

Similar content being viewed by others

References

R.L. Wadsack, “Fault modeling and logic simulation of CMOS and MOS integrated circuits,”Bell System Technical Journal, vol. 57, pp. 1449–1474, May–June 1978.

O.H. Ibarra and S.K. Sahni, “Polynomially complete fault detection problems,”IEEE Trans. Computers vol. C-24, pp. 242–249, March 1975.

S.T. Chakradhar, M.L. Bushnell, and V.D. Agrawal, “Toward massively parallel automatic test generation,”IEEE Trans. CAD, vol. 9, 981–994, September 1990.

E.P. Hsieh, R.A. Rasmussen, L.J. Vidunas, and W.T. Davis, “Delay test generation,”Proc. 14th Design Automation Conf., pp. 486–491, 1977.

G. Smith, “Model for delay faults,”Proc. Int. Test Conf., pp. 342–349, 1985.

J.A. Waicukauski, E. Lindbloom, B.K. Rosen, and V.S. Iyengar, “Transition fault simulation,”IEEE Design & Test of Computers, vol. 4, pp. 32–37, April 1987.

M.H. Schulz and F. Brglez, “Accelerated transition fault simulation,”Proc. 24th Design Automation Conf., pp. 237–243, 1987.

H. Cox and J. Rajski, “Stuck-open and transition fault testing in CMOS complex gates,”Proc. Int. Test Conf., pp. 688–694, 1988.

S.M. Reddy, V.D. Agrawal, and S.K. Jain, “A gate level model for CMOS combinational logic circuits with application to fault detection,”Proc. 21st Design Automation Conf., pp. 504–509, June 1984.

W. Wu and C.L. Lee, “A probabilistic testability measure for delay faults,”Proc. 28th Design Automation Conf., pp. 440–445, 1991.

J.A. Freeman and D.M. Skapura,Neural Networks: Algorithms, Applications, and Programming Techniques, Addison-Wesley Publishing Company, Reading, MA, 1991.

J.J. Hopfield, “Neurons with graded response have collective computational properties like those of two state neurons,”Proc. of Nat'l Academy of Sciences, pp. 3088–3092, May 1984.

V.D. Agrawal and S.C. Seth,Test Generation for VLSI Chips, IEEE Computer Society Press, Washington, DC, 1988.

M. Abramovici, P.R. Menon, and D.T. Mill, “Critical path tracing: an alternative to fault simulation,”IEEE Design & Test of Computers, vol. 1, pp. 83–93 Feb. 1984.

P. Agrawal, V.D. Agrawal, and S.C. Seth, “DynaTAPP: dynamic timing analysis with partial path activation in sequential circuits,”Proc. European Design Automation Conf., pp. 138–141, 1992.

E. Arts and J. Korst,Simulated Annealing and Boltzmann Machine: A Stochastic Approach to Combinational Optimization and Neural Computing, John Wiley & Sons, New York, 1990.

F. Brglez, “On testability analysis of combinational networks,”Proc. of Int. Symp. on CAS, pp. 221–225, 1984.

C.J. Lin and S.M. Reddy, “On delay fault testing in logic circuits,”IEEE Trans. on CAD, vol. 6, pp. 694–703, September 1987.

M. Serra and J.C. Muzio, “Space compaction for multipleoutput circuits,”IEEE Trans. on CAD, vol. 7, pp. 1105–1113, October 1988.

D.A. Pucknell,Fundamentals of Digital Logic Design: with VLSI Circuit Applications, Prentice Hall, Eiglewood Cliffs, NJ, 1990.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Zhang, Z., Mcleod, R.D. & Pedrycz, W. A neural network algorithm for testing stuck-open faults in CMOS combinational circuits. J Electron Test 4, 225–235 (1993). https://doi.org/10.1007/BF00971972

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00971972