Abstract

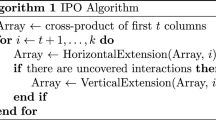

This article presents new approaches for testing VLSI array architectures used in the computation of the complexN-point Fast Fourier Transform. Initially, an unrestricted single cell-level fault model is considered. The first proposed approach is based on a process whose complexity is independent (or C- as constant) of the number of cells in the FFT architecture. This is accomplished by showing a topological equivalence between the FFT array and a linear (one-dimensional) array. The process of fault location is also analyzed. The second proposed method is based on a testing process whose complexity is linear with respect to the number of stages (columns) of the FFT array. A component-level fault model is also proposed and analyzed. The implications of this model on the C-testability process are fully described.

Similar content being viewed by others

References

H.T. Kung, “Why systolic architectures?,”Computer, vol 15, pp. 37–46, January 1982.

T. Leighton and C.E. Leiserson, “Wafer scale integration of systolic arrays,”IEEE Trans. on Computer, Vol C34, pp. 448–461, May 1985.

J.H. Cooley and J. Tukey, “An algorithm for the machine calculation of complex fourier series,”Math. of Comp., vol. 19, pp. 297–301, 1965.

K.H. Huang and J.A. Abraham, “Algorithm-based fault tolerance for matrix operations,”IEEE Trans. on Computers, vol. C33, pp. 518–528, June 1984.

M. Malek and Y.H. Choi, “A fault-tolerant FFT processor,”Proc. IEEE FTCS 15, pp. 266–271, 1985.

J.Y. Jou and J.A. Abraham, “Fault-tolerant FFT networks,”Proc. IEEE FTCS 15, pp. 338–343, 1985.

K. Yamashita, et al., “A wafer scale 170,000-gate FFT processor with built-in test circuits,”IEEE Journal of Solid State Circuits, vol. SC23, pp. 336–341, February 1988.

T. Sridhar and J.P. Hayes, “Design of easily testable bit-sliced systems,”IEEE Trans. on Computers, vol. C30, pp. 842–854, November 1981.

W-K Huang and F. Lombardi, “Fault-detection and design complexity in C-testable VLSI arrays,”IEEE Trans. on Computers, vol. C39, pp. 1477–1481, December 1990.

R. Parthasarathy and S.M. Reddy, “A testable design for iterative logic arrays,”IEEE Trans. on Computers, vol. C30, pp. 833–841, November 1981.

J.P. Shen and F.J. Ferguson, “The design of easily testable VLSI array multipliers,”IEEE Trans. on Computers, vol. C33, pp. 551–560, June 1984.

A. Chatterjee and J.A. Abraham, “Test generation for arithmetic units by graph labeling,”Proc. IEEE FTCS 17, pp. 284–289, 1987.

W.T. Cheng, and J. Patel, “A minimum test set for multiple fault detection in ripple carry adders,”IEEE Trans. on Computers, vol. C-39, pp. 891–895, July 1987.

C. Wu and T. Feng, “Fault diagnosis for a class of multistage interconnection networks,”IEEE Trans. on Computers, vol. C30, pp. 743–758, October 1981.

J.H. Patel and L.Y. Fung, “Concurrent error detection in ALUs by recomputing with shifted operands,”IEEE Trans. on Computers, vol. C31, 7, pp. 589–595, July 1982.

Author information

Authors and Affiliations

Additional information

This research is supported by grants from NSF and NSERC.

Rights and permissions

About this article

Cite this article

Feng, C., Muzio, J.C. & Lombardi, F. On the testability of array structures for FFT computation. J Electron Test 4, 215–224 (1993). https://doi.org/10.1007/BF00971971

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00971971