Abstract

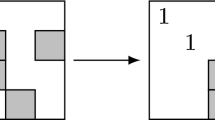

This paper presents various approaches for testing cellular tree structures with a constant number of test vectors, that is, independent of the number of cells (size of the tree). The necessary and sufficient conditions which must be satisfied in the state table of a basic combinational cell for achieving C-testability and one-step C-testability in a homogeneous tree, are proved. The design modifications required to accomplish this objective in arbitrary cells, are discussed. It is proved that three additional rows and three additional columns are needed in the state table of a cell; the characteristics of the additional states are also analyzed. The complexity of the proposed testing process is quadratic with respect to the number of entries in the state table of a cell. Illustrative examples are also given.

Similar content being viewed by others

References

K. Hwang, and F. Briggs, “Computer architecture and parallel processing,” New York: McGraw Hill, 1984.

C.A. Mead, and L.A. Conway, Introduction to VLSI Systems, Reading, MA: Addison-Wesley, 1980.

J.R. Goodman and C.H. Sequin, “Hypertree: A multiprocessor interconnection topology,” IEEE Trans. on Computers, vol. C-30, pp. 923–933, 1981.

J. Bentley, and H.T. Kung, “A tree machine for searching problems,” Proc. Int. Conf. Parallel Processing, pp. 257–266, 1979.

A.M. Despain, and D.A. Pattern, “X-Tree: A tree structured multiprocessor computer architecture,” Proc. 5th Comp. Arch. Symp., pp. 144–150, 1978.

A.K. Somani and V.K. Agarwal, “An efficient unsorted VLSI dictionary machine,” IEEE Trans. on Computers, vol. C-34, pp. 841–852, 1985.

M.J. AttaLan, and S.R. Kosaraju, “A generalize dictionary machine for VLSI,” IEEE Trans. on Comput., vol. C-34, pp. 151–155, 1985.

J.A. Abraham, and D.D. Gajski, “Design of testable structures defined by simple loops,” IEEE Transactions on Computers, vol. C-33, pp. 875–884, 1981.

F.G. Gray, and R.A. Thompson, “Fault detection in bilateral arrays of combinational cells,” IEEE Trans, on Comput., vol. C-27, pp. 1206–1213, 1978.

A.D. Friedman, “Easily testable iterative systems,” IEEE Trans, on Comput., vol. C-22, pp. 1061–1064, 1973.

S.C. Seth, and K.L. Kodandapani, “Diagnosis of faults in linear tree networks,” IEEE Transactions on Computers, vol. C-26, pp. 29–33, 1977.

A. Chatterjee and J.A. Abraham, “C-Testability for generalized tree structures with applications to Wallace trees and other circuits,” Proc. IEEE ICCAD, pp. 288–291, 1986.

H. Elhuni, A. Vergis, and L. Kinney, “C-Testability of two-dimensional iterative arrays,” IEEE Trans, on CAD, vol. CAD-5, pp. 573–581, 1986.

F. Lombardi and W.-K. Huang, “On an improved design approach for C-Testable orthogonal iterative arrays,” IEEE Trans, on CAD, vol. CAD-7, pp. 609–615, 1988.

M. Gondran and M. Minoux, “Graphs and algorithms,” New York: John Wiley, 1984.

M.R. Gaey and D.S. Johnson, “Computers and intractability,” San Francisco: Freeman, 1979.

R. Parthasarathy and S.M. Reddy, “A testable design for iterative logic arrays,” IEEE Trans, on Comput., vol. C-30, pp. 833–841, 1981.

Texas Instruments Inc.“,The TTL data book for design engineers,” Dallas, TX: Texas Instruments 1981.

D. Sciuto, “Testability of trees,” Internal Report, University of Brescia, 1991.

F. Lombardi and W.-K. Huang, “Fault detection and design complexity in C-testable VLSI arrays,” IEEE Trans, on Computers, vol. C39, pp. 1477–1481, 1990.

G. Buonanno, D. Sciuto, and F. Lombardi, “Testability conditions for linear sequential arrays,” Proc. IEEE Phoenix Conf on Comp. and Comm., pp. 63–70, 1991.

F. Lombardi, and D. Sciuto, “On functional testing of array processors,” IEEE Trans, on Computers, vol. C37, pp. 1480–1484, 1988.

Author information

Authors and Affiliations

Additional information

This research supported in part by grants from NATO and NSF.

Rights and permissions

About this article

Cite this article

Lombardi, F., Sciuto, D. Constant testability of combinational cellular tree structures. J Electron Test 3, 139–148 (1992). https://doi.org/10.1007/BF00137251

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00137251