Abstract

This article reviews the state of the art in inversion-type p-channel diamond MOSFETs. We successfully developed the world’s first inversion-channel homoepitaxial and heteroepitaxial diamond MOSFETs. We investigated the dependence of phosphorus concentration (NP) of the n-type body on field-effect mobility (μFE) and interface state density (Dit) for the inversion channel homoepitaxial diamond MOSFETs. With regard to the electrical properties of both the homoepitaxial and heteroepitaxial diamond MOSFETs, they suffer from low μFE and one main reason is high Dit. To improve the interface quality, we proposed a novel technique to form OH-termination by using H-diamond followed by wet annealing, instead of the previous OH-termination formed on O-diamond. We made precise interface characterization for diamond MOS capacitors by using the high-low C–V method and the conductance method, providing further insights into the trap properties at Al2O3/diamond interface, which would be beneficial for performance enhancement of the inversion-type p-channel diamond MOSFETs.

Graphic abstract

Similar content being viewed by others

Introduction

Diamond is considered as an ultimate material for power-electronics applications owing to its superior physical properties, such as a wide bandgap (5.5 eV), high breakdown electric field (> 10 MV/cm), high carrier mobility (7300 and 5300 cm2V−1s−1 for electron and hole, respectively), and high thermal conductivity (2200 Wm−1K−1) [1,2,3,4,5]. Therefore, diamond-based devices are promising for power applications and have been receiving more and more attention in recent years [6,7,8,9,10,11,12,13]. Among diamond power devices, the diamond metal–oxide–semiconductor field-effect transistor (MOSFET), a kind of popular power switching device, has been intensively investigated worldwide. Many studies have been devoted to the development of hydrogenated diamond (H-diamond) MOSFETs because the H-diamond surface can accumulate two-dimensional hole gases [14,15,16,17,18,19,20,21,22,23]. Recently, Kawarada’s group reported the first vertical H-diamond MOSFETs [24, 25]. In addition, Pernot’s group proposed the deep depletion concept and concentrated on the oxygen-terminated diamond (O-diamond) MOSFETs [26,27,28]. However, both H- and O-diamond MOSFETs basically demonstrate normally on characteristics. Recently, a few accumulation-channel H-diamond MOSFETs with normally off properties have been developed [29,30,31,32]; however, it is difficult for them to control the threshold voltage by selection of metal work function. In contrast, diamond MOSFETs with inversion channels are more competitive because they can modulate the threshold voltage by changing the impurity concentration in the body and thus control the electric power. Our group has been focusing on the development of inversion-type p-channel diamond MOSFETs with normally off operation in recent years. We concentrated on the hydroxyl (OH)-terminated diamond (111) surface formed by O-diamond followed by wet annealing, and successfully fabricated the world’s first inversion-type p-channel homoepitaxial diamond MOSFETs [33]. We characterized the corresponding electrical properties and evaluated the effect of the surface roughness on the field-effect mobility (μFE). Besides, we investigated the dependence of phosphorus concentration (NP) of the n-type body on μFE and interface state density (Dit) for the inversion channel homoepitaxial diamond MOSFETs [34]. Considering the commercialization, the application of the homoepitaxial diamond MOSFETs are limited due to the small size of High-pressure High-temperature (HPHT) diamond substrates and their high cost. Concerning this issue, we attempted to develop the inversion-type p-channel heteroepitaxial freestanding diamond MOSFETs where the diamond epitaxy was realized on Iridium (Ir)/intermediate layer/Si substrates [35]. With regard to the electrical properties of both the homoepitaxial and heteroepitaxial inversion-channel diamond MOSFETs, they suffer from low μFE and one of the main limiting factors is high Dit. Aiming at this problem, we focused on the interface evaluation of Al2O3/diamond from the perspective of diamond MOS capacitors by employing the high-low capacitance–voltage (C–V) method [36]. To reduce Dit and to improve the interface quality, we proposed a novel technique to form OH-termination by using H-diamond followed by wet annealing [37], instead of the previous OH-termination formed on O-diamond. And we made more precise interface characterization by using the high-low C–V method at various temperatures and with wide frequency ranges [38]. Furthermore, we employed the high-temperature conductance method by considering the surface potential fluctuation to gain further insights into the properties of interfaces states at Al2O3/diamond interface, including the capture cross section, time constant of interfaces states and the trap type, which would be beneficial to have a profound understanding of the Al2O3/diamond interface [39]. The purpose of this paper is to review the current progress of the studies of the inversion-type p-channel diamond MOSFETs and the corresponding interface characterization of diamond MOS capacitors. Specifically, in Sec. I.A and Sec. I.B, the work about inversion-channel homoepitaxial and heteroepitaxial diamond MOSFETs is introduced. In Sec. II.A and II.B, we exhibit the work about the interface characterization and comparison for two kinds of Al2O3/diamond MOS capacitors where OH-termination was formed on O-diamond or H-diamond. Finally, we give a brief conclusion.

Results and discussion

Inversion-type p-channel diamond MOSFETs

Inversion-type p-channel MOSFETs on homoepitaxial diamond substrates

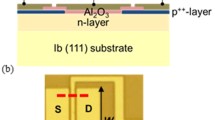

Figure 1a and b demonstrate the schematic cross-section and top-view optical microscope image of the inversion-type p-channel HPHT diamond MOSFETs. Figure 2a shows the drain current density–drain voltage (Ids–Vds) characteristics at various gate voltages (Vgs) for a typical diamond MOSFET with gate length (L) of 5 μm and gate width (W) of 150 μm. The MOSFET clearly shows the normally off feature and saturation characteristics. The maximum value of Ids is − 1.6 mA/mm and the peak drain conductance is 0.73 mS/mm, respectively. Figure 2b shows Ids in the linear scale and transfer conductance gm vs Vgs characteristics where Vds was set as − 0.1 V. The maximum gm is 30 μS/mm at Vgs = − 10.7 V. According to the Ids–Vgs characteristics, the threshold voltage (VT), determined from the fitting of the Ids–Vgs curve in the Vgs range from − 7 to − 9 V, was 6.3 V. The field effect mobility (μFE) was estimated using the following equation [40]:

where Cox is the gate oxide capacitance per unit area (dielectric constant of Al2O3: 7.3). The maximum μFE was estimated to be 8.0 cm2V−1s−1. Based on the log |Ids|–Vgs characteristics, the subthreshold swing (S) can be evaluated by [40]

where k is the Boltzmann constant, T the absolute temperature, q the electronic charge, Cd the depletion-layer capacitance, and Cit the capacitance contribution from the interface sates and it is equal to qDit, where Dit the density of interface states [40]. The subthreshold swing S, calculated from the fitting of the Ids–Vgs curve in the Vgs range from − 3.0 to − 3.5 V, was around 380 mV/dec. Note that we calculated the theoretical value of Cd and found that it was much lower than Cit; thus, we can deduce that the S value was dominated by Cit. According to the S value, the corresponding Dit was evaluated from the subthreshold region, with the value of about 6 × 1012 cm−2eV−1. Note that the Dit estimated from S value can only reflect a small fraction of the interface states that locate between flatband and weak inversion conditions. We can deduce that the high Dit would be one reason for the low channel mobility. Besides, we employed the transmission electron microscopy (TEM) and atomic force microscopy (AFM) measurements to further examine the MOS structure under the gate and the diamond surface of the phosphorus-doped n-type body. From Fig. 3a, we can observe the dark line existing at the interface between the Al2O3 layer and the n-type diamond body, which indicates the presence of bunching steps, consistent with the AFM result demonstrated in Fig. 3b. The existence of the bunching steps implies that the surface morphology was not that good, which would result in low μFE. In addition, it is significant to improve the quality of the phosphorus-doped n-type diamond body to achieve high μFE. In terms of the phosphorus doping, fortunately, we successfully realized the reproducible control of phosphorus doping (Np) from 2 × 1015 to 3 × 1017 cm–3 for diamond films in a previous study [41]. Therefore, we further investigated the Np dependence of μFE and Dit in the inversion channel homoepitaxial diamond MOSFET to understand its electrical and physical characteristics. We fabricated four inversion-type p-channel homoepitaxial diamond MOSFETs where the n-type bodies have different Np concentrations of 2 × 1015, 1 × 1016, 3 × 1016, and 6 × 1016 cm−3. The specific fabrication conditions were introduced in our previous paper [34]. Here, we mainly focused on the electrical characteristic comparison. Figure 4a shows the Ids and μFE vs Vgs − VT for the four homoepitaxial diamond MOSFETs with various doping concentrations. Note that the VT was subtracted from the applied gate voltage for accurate comparison. The absolute value of VT increases with increasing the phosphorus doping concentration (not shown), indicating the good VT modulation for the inversion-type diamond MOSFETs. μFE was estimated from the slope of each Ids–Vgs curve. It is obvious that Ids and μFE increase when Np decreases. And μFE reached 20 cm2V−1s−1 for the MOSFET with NP of 2 × 1015 cm−3. To further examine the dependence of Np on μFE, Dit was evaluated from the threshold slope of the Ids–Vgs characteristics using the subthreshold swing method. Figure 4b shows the dependence of the phosphorus doping concentration on interface state density. It is obvious that Dit increases with decreasing Np. Figure 4c demonstrates the correlation between the maximum μFE and Dit for the inversion channel diamond MOSFETs. Note that the reported Dit–μFE results of other diamond MOSFETs with different surface terminations are also inserted in Fig. 4c [21, 42, 43]. We can see that the μFE and Dit are inversely correlated. Thus, the high Dit is one main limiting factor for the channel mobility of diamond MOSFETs. From the changing tendency of Dit–μFE demonstrated by the arrow inserted in Fig. 4c, we can expect that μFE can exceed 1000 cm2V−1s−1 if Dit is reduced to lower than 1011 cm−2eV−1. This is consistent with the theoretical mobility calculation by considering four scattering mechanisms for the H-diamond MOSFET by Sasama et. al. [44]. Therefore, in our case, it is also very important to develop effective passivation processes to reduce Dit and improve the interface quality between Al2O3 and diamond and thus fabricate the diamond power MOSFETs with superior electrical properties.

Reprinted with permission from Ref. [33] (https://creativecommons.org/licenses/by/4.0/).

(a) Schematic cross-section and (b) top-view image of the inversion-type p-channel HPHT diamond MOSFETs by optical microscopy.

Reprinted with permission from Ref. [33] (https://creativecommons.org/licenses/by/4.0/).

(a) Drain current density–drain voltage (Ids–Vds) and (b) drain current density–gate voltage (Ids–Vgs) characteristics for the inversion-type p-channel HPHT diamond MOSFET.

Reprinted with permission from Ref. [33] (https://creativecommons.org/licenses/by/4.0/).

(a) TEM image of Al2O3/diamond interface. (b) AFM image of surface of n-type diamond body.

(a) and (b) reprinted with permission from Ref. [34] (https://creativecommons.org/licenses/by/4.0/).

(a) Ids and μFE vs Vgs − VT for the four homoepitaxial diamond MOSFETs with various doping concentrations, (b) the dependence of Np on Dit and (c) the correlation between Dit and maximum μFE of the inversion channel HPHT diamond MOSFETs. Note that the reported Dit vs μFE of other terminated MOSFETs were also summarized.

Inversion-type p-channel MOSFETs on heteroepitaxial diamond substrates

As we introduced in Sec. I.A, we developed the world’s first inversion type p-channel homoepitaxial diamond MOSFETs and made the corresponding electrical and physical analysis. Despite the significant breakthrough, given the commercialization and mass production, the substrate size and cost need to be considered. It is known that the size of HPHT diamond substrates is limited within several square millimeters, which is not beneficial to the commercialization of diamond power MOSFETs. Regarding this issue, using heteroepitaxial diamond substrates would be one solution. Diamond epitaxy has been studied for decades and different materials have been explored for heteroepitaxial diamond growth [45,46,47,48,49,50,51,52,53,54,55,56]. Among them, the silicon (Si)-based substrate is one promising candidate for fabrication of diamond power devices due to its large wafer size and low cost. Kawashima et al. and Murooka et al. have fabricated the heteroepitaxial diamond Schottky barrier diodes (SBDs) on Ir/intermediate layer/Si and 3C-SiC/Si substrates, respectively [47, 54]. However, the potential of the inversion-type heteroepitaxial diamond MOSFET has not been evaluated yet. Based on the fabrication technique of the inversion-channel HPHT diamond MOSFETs, we successfully fabricated the inversion-channel heteroepitaxially-grown freestanding diamond MOSFET where the diamond heteroepitaxy was realized on Ir/intermediate layer/Si (111) substrate [35]. We examined the electrical properties of the heteroepitaxial diamond MOSFET and the surface morphology by AFM.

Figure 5a shows the top-view optical microscope image of the inversion-type p-channel heteroepitaxial diamond MOSFETs. Figure 5b and c illustrate the Ids–Vds and Ids–Vgs characteristics for a typical heteroepitaxial diamond MOSFET with L of 15 mm and W of 150 mm. Ids–Vds properties clearly show the normally off feature and a saturation tendency. The maximum drain current density is about 0.35 mA/mm. From Ids–Vgs characteristics shown in Fig. 5c, the VT determined by linear extrapolation of the Ids–Vgs curve to zero [40], is about − 5.1 V. The μFE–Vgs characteristic is shown in Fig. 5d. The maximum of μFE was about 2.7 cm2V−1s−1. This value is slightly lower than the μFE reported in homoepitaxial diamond MOSFETs, as mentioned in Sec. I.A. For the heteroepitaxial diamond MOSFET, μFE first increases with the negative Vgs lower than − 7 V and then decreases with higher negative Vgs. The latter would be caused by acoustic phonon or surface roughness scattering [44, 57,58,59]. According to the log |Ids|–Vgs characteristics, S is estimated to be 355 mV/dec. And the corresponding Dit extracted from the subthreshold region is about 5.5 × 1012 cm−2eV−1. This value is not significantly different from the Dit of the homoepitaxial diamond MOSFETs. To discuss scattering by surface roughness, the surface properties of the n-type body of the heteroepitaxial diamond MOSFET has been characterized by AFM measurements, as illustrated in Fig. 5e. The root mean square roughness (RMS) of the n-type diamond surface is 30.6 nm with the scanning area of 15 μm × 15 μm. The AFM image demonstrates two local regions with distinct differences of surface morphologies. To investigate the detailed surface properties, AFM measurements were performed with typical scanning areas of 500 nm × 500 nm. The results are shown in Fig. 5e: see lower left and lower right insets. The RMS varies from 2.2 (left) to 13.8 nm (right). The RMS difference may be correlated with the different crystalline phases generated from the non-uniformity of the defect dislocation during the heteroepitaxial diamond growth. Nevertheless, the RMS of 2.2 nm is still larger than that of HPHT diamonds (below 1 nm within a comparable scanning area). The origin of this roughness after polishing the hetero-diamond layer is not clear up to now. It indicates that, however, this may be one limiting factor of the channel mobility. Besides, the relatively poor quality of the heteroepitaxial diamond, with the dislocation density of around 108 cm−2 [54], would also lead to the low μFE of the heteroepitaxial diamond MOSFET. It should be noted that the channel mobility of the inversion-type p-channel MOSFET on the heteroepitaxial diamond is lower than those of the H-terminated diamond MOSFETs or MISFETs fabricated on polycrystalline or heteroepitaxial diamonds [48, 60,61,62]. One possible reason is due to the uneven quality and resultant different surface roughnesses of the heteroepitaxial or polycrystalline diamond films formed by this work and others. Besides, the higher density of interface states in our inversion-type diamond MOSFETs, more than one order of magnitude higher than the H-terminated diamond surface (below 1011 cm−2eV−1), would be another main reason for the low channel mobility. In addition, the carrier density in our case is low, around 0.8 ~ 4.3 × 1012 cm−2. For the H-terminated diamond devices, their carrier density is on the order of 1013 cm−2 and the high density of channel carriers would bring about the screening effect and thus lead to the high channel mobility. Obviously, heteroepitaxial growth of diamond requires further improvements before high-quality MOSFETs can be realized. With the “lateral overgrowth technique” [63,64,65,66,67,68], a better surface can be grown to form atomically flat diamond surfaces, with the aim to reduce the RMS significantly. By these ways, the device performance of the inversion-type p-channel heteroepitaxial diamond MOSFETs can be improved, which would facilitate the commercialization of diamond electronic applications like power devices significantly.

Reprinted with permission from Ref. [35] (https://creativecommons.org/licenses/by/4.0/).

(a) Top-view image of the inversion-type p-channel heteroepitaxial diamond MOSFETs by optical microscopy, (b) Ids–Vds, and (c) Ids–Vgs characteristics for a typical MOSFET with L/W = 15/150 μm, (d) Vgs dependence of μFE for the inversion type p-channel heteroepitaxial diamond MOSFET and (e) three-dimensional AFM images of the n-type diamond body.

Al2O3/p-type diamond MOS interface

We have successfully developed the inversion-type p-channel MOSFETs on both homoepitaxial and heteroepitaxial diamond substrates. However, the low channel mobility is one big challenge for their practical application. From the electrical property characterization, the Dit is considered as one of the main reasons for the low channel mobility. As mentioned above, the Dit estimated from the log |Ids|–Vgs characteristics and the relevant S value of the MOSFETs can just reflect a small fraction of the interface states located in the energy interval between flatband and weak inversion conditions. The more precise evaluation of Dit is required by focusing on the Al2O3/diamond MOS capacitors. Our group have made some attempts to investigate the Al2O3/diamond interface by using MOS capacitors. We would like to introduce the relevant work in detail in the following sections.

Interface of Al2O3/p-type OH-diamond formed by wet annealing on O-diamond

Regarding the studies of diamond MOS capacitors, we just concentrated on the HPHT diamond substrates. The specific fabrication process was introduced in our previous report [36]. Figure 6a shows the capacitance–voltage (C–V) characteristics of the p-type diamond (111) MOS capacitor at frequencies of 10 Hz and 10 kHz. Note that the leakage current was low enough. Based on the high-low C–V method, Dit can be calculated as [40]

where Cox is the oxide capacitance, q the elementary charge, Clf the capacitance at a low frequency and Chf the capacitance at a high frequency. The energy distribution of Dit is shown in Fig. 6b. The estimated Dit was in the range of 4–9 × 1012 cm−2eV−1. Note that the frequency range is relatively narrow. The low frequency is not low enough and a fraction of slow interface states cannot follow the ac signal; therefore, the Clf is not able to contain all the capacitance contribution of interface states. Likewise, the high frequency is not high enough and the Chf cannot exclude the capacitance components of the fast interface states. Thus, we should say the true Dit would be higher than the estimated value. Therefore, the diamond MOS characterization also verifies that the high Dit would be one main limiting factor for the low μFE. However, the origin of the high Dit is still unclear. Here, we would like to discuss the possible reason. With regard to the O-terminated diamond surface, the possible candidates of surface states are considered as two types of surface oxygen sites; one is bridge site (C–O–C) and the other is on top site (C = O) [69, 70], which has been detected for O-terminated diamond surface by Fourier transform infrared (FTIR) spectroscopy in our previous work [37]. The presence of C–O–C and C = O makes it less effective to form C–OH termination by employing subsequent wet annealing process. For the subsequent ALD process, it would be difficult for C–O–C and C = O to react with Al(CH3)3 (TMA) and both would still remain at the interface, which may be responsible for high Dit of the OH-terminated diamond MOS formed on O-terminated one. Therefore, the reduction of C–O–C and C = O may be beneficial to improve the interface properties of Al2O3/diamond and further to enhance device performance of diamond MOSFETs.

Interface of Al2O3/p-type OH-diamond formed by wet annealing on H-diamond

Considering the possible origin of high Dit as analyzed above, we developed a novel technique to form OH-termination on H-diamond surface, instead of on O-diamond one, with the purpose of the reduction of C–O–C and C = O. We found that the two-dimensional hole gas layer disappeared when the wet annealing temperature exceeded 500 °C. From the measurements by FTIR spectroscopy, we observed the C–O–H peak. Moreover, the surface morphology was not degraded before and after wet annealing [37]. Therefore, we employed this OH-formation technique on H-diamond surface to fabricate the Al2O3/diamond MOS capacitors and carefully evaluated the interface properties by using high-low C–V method and conductance method. The frequency-dependent C–V characteristics at 300 K for the p-type diamond MOS capacitor was demonstrated in Fig. 7a. We can observe a hump at 1 Hz and its magnitude decreases with increase in the measurement frequency. We can deduce that the hump would be attributed to the response of the interface states at deep energy levels. Because the interface states at deep energy levels have long emission time constants, they can follow the ac signal at low frequencies and thus contribute to the capacitance, whereas they cannot immediately change occupancy in response to the ac gate voltages at high frequencies, resulting in the frequency dispersion. Considering the time constant property of interface states at deep energy levels, measurements at higher temperatures are indispensable to detect them because their thermal emission would become faster and even deeper interface states can be detected within the same given frequency range. Figure 7b and c illustrate the frequency-dependent C–V characteristics at 350 and 400 K. The frequency dispersion of C–V curves in the depletion region increases as the measurement temperature increases, indicating that interface states at deep energy levels can be detected at 400 K. Note that the frequency dispersion of the accumulation capacitance was also observed, which would be attributed to the border traps, often observed in InGaAs and SiC MOS structures [71,72,73,74]. The effect of series resistance on the accumulation capacitance was examined by a standard correction method [75], but the dispersion was unchanged after the correction. The frequency dispersion analysis of the accumulation capacitance requires a distributed circuit model which could quantify the impendence components of the border traps and is essential to investigate in the next step. Here, let us focus on the depletion region and the interface states at deep energy levels. According to the C–V dispersion from 1 Hz and 10 MHz at 400 K and high-low method, we evaluated Dit vs the energy position from Ev of diamond, as demonstrated in Fig. 7d. We should point out that the surface potential was determined by the Berglund integral, and the integral constant (ψs0) was determined from the flatband voltage in the C–V curve at 10 MHz [76]. With respect to the energy position dependence of Dit, Dit first increases dramatically from 0.23 to 0.6 eV and then gradually saturates at energy position deeper than 0.6 eV from Ev of diamond. Even though the detectable energy range is limited, the decrease in Dit in the energy levels deeper than 0.76 eV from Ev, corresponding to the gate voltage higher than 1.6 V, can be expected from the reduced frequency dispersion of the C–V characteristics. The estimated trap density was (0.4–1.5) × 1012 cm−2eV−1, lower than that of the Al2O3/diamond MOS with a value of (4–9) × 1012 cm−2eV−1 in which the OH-terminated diamond surface was formed on the O-terminated diamond, as we introduced in Sec. II.A. Even though the measurement temperature and frequency ranges are different, the Al2O3/diamond interface quality is improved. Here, we would like to discuss the possible reason. When the OH-termination is formed by H-plasma and subsequent wet annealing, the C–OH bonds were formed [37]. Then during the ALD growth of Al2O3, these C–OH bonds can react with TMA to form C–O–Al. However, it is difficult for C–O–C and C = O to react with TMA to form C–O–Al in the case of the Al2O3/OH-terminated diamond formed on O-terminated treatment. Thus, there would be more C–O–C and C = O for OH-terminated diamond formed by O-terminated treatment than that formed by H-terminated treatment. Given that C–O–C and C = O could be responsible for the high Dit, we can deduce that Dit is lower for the OH-terminated diamond formed on H-terminated diamond followed by wet annealing than that by O-termination and subsequent wet annealing. Note that the interface states at deep energy levels can act as Coulomb scattering centers when they are positively charged and thus degrade the channel mobility of diamond MOSFETs; therefore, more effective passivation techniques are required to reduce Dit.

Reprinted with permission from Ref. [38] (https://creativecommons.org/licenses/by/4.0/).

Frequency dispersion of C–V characteristics at (a) 300, (b) 350, and (c) 400 K for the p-type diamond (111) MOS capacitor where OH-termination was formed on H-diamond with wet annealing, and (d) the extracted Dit vs energy position from Ev of diamond at 400 K.

Prior to the further development of passivation techniques, it is important to make a deep understanding for the interface states at deep energy potions away from Ev of diamond. However, the limitation of the high-low method makes it difficult to precisely evaluate the interfaces states. Therefore, we applied the more powerful conductance method to analyze the Al2O3/diamond interface [77,78,79]. The conductance method can accurately determine Dit and time response by detecting the time delay of carrier exchange between interface states and the energy band edge via an ac conductance component. To be specific, a small ac voltage superimposed on a certain dc voltage is applied to the gate of a MOS capacitor and thus alternately moves the band edges towards or away from the Fermi level, resulting in the capture and emission of majority carrier between interface states and the energy band edge. The lag-behind of the interfaces state response would lead to the energy loss. The energy loss caused by interface states can be reflected by the measurement parameter of parallel conductance Gp. Therefore, the information of interface states can be obtained from Gp [80]. This approach has been extensively applied for Si, Ge, SiC, and GaN MOS structures [77, 81,82,83]. However, the interface of diamond MOS structures has been seldom investigated by this method. Pham et al. performed the conductance analysis for the Al2O3/O-terminated diamond capacitors with assuming the single-level interface states, and the surface potential fluctuation was neglected [84]. Likewise, Saha et al. employed the conductance method with assumption of single trap levels to characterize the Al2O3/H-terminated MOS structures [85]. They supposed two distinctive peaks to analyze the broadening of conductance peaks without consideration of surface potential fluctuation, where the two peaks correspond to interface traps and border traps. However, it should be noted that the assumption of the single energy level of interface states is the ideal case and cannot reflect the practical device-grade interfaces. A spatial distribution of interface state levels in energy over the semiconductor bandgap is the common case [80]. In fact, the broadening of the conductance peak indicates that the energy levels of interface states are spatially distributed in the semiconductor bandgap [80]. Moreover, surface potential fluctuation generated by the interface charge inhomogeneity should be taken into account, which is significant to elucidate the interface state properties, such as the interface state density, trap type (donor-like or acceptor-like), capture cross section and time constant. The neglect of surface potential fluctuation would lead to errors when extracting interface state density.

Based on the introduction of the conductance method, we employed it with considering the surface potential fluctuation to gain deep insights into the properties of interface states for Al2O3/diamond MOS where OH-termination was formed on H-terminated diamond via wet annealing. Thus, we would like to introduce the conductance analysis in detail. We can first extract the experimental Gp/ω by the equation as follows [80]:

where ω, Gexp, Cox, and Cexp respectively represent the angular frequency, the experimental conductance, the oxide capacitance, and the experimental capacitance at a certain voltage and frequency. Note that series resistance (Rs) has been extracted and Gexp and Cexp have been corrected. It was found that Rs has almost no effect on the Gp/ω characteristics in the depletion region. The symbols in Fig. 8 stand for the experimental parallel conductance vs frequency (Gp/ω–f) characteristics at various gate voltages at 400 K. The maximum value of Gp/ω((Gp/ω)max), representing the density of interface states, increases with the increase in gate voltage, which agrees well with the energy dependence of Dit extracted by the high-low method. We can see that the Gp/ω–f curves were broadening, which implies that the surface potential fluctuation occurs. According to Nicollian’s theory by considering the surface potential fluctuation, the theoretical Gp/ω can be expressed as

Reprinted with permission from Ref. [39] (https://creativecommons.org/licenses/by/4.0/).

Frequency dependence of experimental (denoted by circles) and theoretical (denoted by lines) Gp/ω at 400 K.

where Us and τit respectively represent the normalized surface potential and the interface state time constant [80]. P(Us) is a probability distribution of the surface potential fluctuation, expressed by

where \(\overline{{U_{{\text{s}}} }}\) and σs represent the normalized mean surface potential and the standard deviation due to surface potential fluctuation [80]. These two equations indicate that we can employ Gaussian approximation to analyze the Gp/ω–f properties. Here, Brews’s graphical approach with assuming the validity of the Gaussian approximation to broadening of the conductance peak, was employed to extract the parameters of interface states, including Dit, hole capture cross section (σp), time constant of interface states (τit), and standard deviation of surface potential fluctuation (σs) [86, 87]. The experimental and theoretical Gp/ω–f curves were compared to confirm the fitting results and thus the accuracy of the extracted parameters. The solid lines in Fig. 8 represents the obtained theoretical Gp/ω–f curves at various gate voltages. The good fitting was clearly observed from Fig. 8, suggesting the accuracy of the extracted parameters. The energy distribution of Dit is illustrated in Fig. 9a. Note that we also demonstrate the energy dependences of Dit extracted by the high-low method and conductance method without considering surface potential fluctuation to make a comparison. The Dit result extracted by conductance method is in accordance with that by high-low method; however, a big error occurs for the case without considering the surface potential fluctuation. Besides, the detectable energy range of Dit is narrow by using conductance method, owing to the measurement limitation that the peak frequencies (fp) of Gp/ω at other energy positions were out of the measurement frequency range and cannot be detected. Figure 9b and c show the energy dependence of the extracted σp and τit of interface states. The extracted σp was on the order of around 10−17 cm2, comparable to the hole capture cross section at SiO2/Si interface [81]. According to the dependence of energy position on τit, which reflects the characteristic time required to fill and empty interface traps at various levels, it can be deduced that the capture and emission of holes by interface states obey the Shockley–Read–Hall (SRH) statistics [88]. Figure 9d demonstrates σs as a function of the energy position from Ev of diamond. σs decreases as the trap energy level becomes away from Ev of diamond, which is a feature of donor-like traps. Here, we use the schematic band diagram illustrated in Fig. 10 to explain this phenomenon and the feature of donor-like traps. Donor-like traps are positive when empty, and neutral when full of electrons. When EF moves towards Ev of diamond, as shown in Fig. 10a, the donor-like traps above EF remain positive and the ones below EF become neutral because they have occupied electrons. Note that the positive charging states can affect the surface potential fluctuation. Therefore, the σs is large when EF is close to Ev of diamond. When EF moves far from Ev, as shown in Fig. 10b, more donor-like traps will capture electrons and become neutral; therefore, the positive charging states will decrease. As a result, they can hardly affect the surface potential fluctuation and thus σs decreases. In terms of other oxide/semiconductor MOS structures, the lower part of the bandgap generally is occupied with donor-like traps and the upper half is occupied with acceptor-like traps [40, 89]. To date, the investigation of diamond MOS interfaces is far from satisfactory and the origin of donor-like interface states is still not clear in the Al2O3/diamond interface [90, 91]. Concerning the oxide/Si interface, the Pb centers are considered as the main reason for interface states and they are amphoteric. They behave acceptor-like in the upper half of the bandgap whereas they behave donor-like in the lower half of the bandgap [92]. Based on the Electrically-Detected-Magnetic-Resonance (EDMR) Study for SiO2/SiC interface, the C-related defects act as interfacial hole traps via their donor level and result in the negative threshold voltage shift for SiC MOSFETs [93]. Even though our interface structure is different from the SiO2/SiC case, we can make a hypothesis that the C dangling bonds which are similar with Pb centers could be one possible candidate for the donor-like interface traps in the Al2O3/diamond interface. However, further theoretical and experimental investigations are required to clarify the physical mechanism of the donor-like interface states.

Reprinted with permission from Ref. [39] (https://creativecommons.org/licenses/by/4.0/).

Energy distribution of (a) interface state density (Dit), (b) capture cross section (σp), (c) time constant of interfaces states (τit), and (d) standard deviation of surface potential fluctuation (σs).

Reprinted with permission from Ref. [39] (https://creativecommons.org/licenses/by/4.0/).

Interpretation for the feature of donor-like traps using the band diagrams of (a) Fermi level (EF) close to valence band edge (Ev) and (b) EF level far from Ev of diamond.

Conclusion

In conclusion, the research progress of the inversion-type p-channel diamond MOSFETs and corresponding p-type MOS capacitors have been reviewed in this paper. The inversion-channel homoepitaxial and heteroepitaxial diamond MOSFETs were developed on OH-terminated diamond formed on O-diamond followed by wet annnealing. Aiming at the low μFE for both kinds of MOSFETs, one of main limiting factors is the high Dit. Concerning the high Dit, we proposed a novel technique to form OH-termination to improve the interface quality of Al2O3/diamond by using H-diamond followed by wet annealing, instead of the previous OH-termination formed on O-diamond. The interface quality was significantly improved based on our precise interface characterization and comparison for diamond MOS capacitors by using the high-low C–V method. Furthermore, we employed the conductance method to give further insights into the trap properties at Al2O3/diamond interface, which would be beneficial for deep understanding of the interface states and would facilitate the exploration of more efficient passivation techniques to improve the interface quality and device performance. Besides, with respect to the effect of the surface roughness on channel mobility, we should focus more on the fattening of the diamond surface in the next step, for example, we can employ the lateral overgrowth technique to form a better atomically flat diamond surface. With these efforts of surface roughness and interface quality, the device performance of the inversion-type p-channel diamond MOSFETs can be improved and their commercialization can be promoted. Besides, we desire to develop the trench-type inversion-channel diamond MOSFETs to facilitate their power application based on our novel technique that the V- and U-shaped diamond trench structures were successfully formed using Ni etching in high-temperature water vapour [94, 95].

Experimental methods

Inversion-type p-channel MOSFETs on homoepitaxial diamond substrates

We used the HPHT synthetic Ib (111) semi-insulating single-crystal diamond substrates to fabricate the inversion-type p-channel homoepitaxial MOSFETs. First, the phosphorus-doped n-type body layer was deposited with a concentration of about ~ 1 × 1017 cm−3 by microwave plasma-assisted chemical vapor deposition (MPCVD). The methane concentration was 0.4%, plasma power 3.6 kW, and chamber pressure 150 Torr, respectively. The thickness of the deposited n-type body was ~ 10 μm. Then, a boron-doped p+-layer with a concentration of about 1 × 1020 cm−3 was selectively grown by MPCVD using a metal mask of Ti/Au (10 nm/200 nm). The methane concentration, plasma power and chamber pressure were respectively 0.2%, 1200 W and 50 Torr. The thickness of the p+-layer was around 50 nm. After removing the metal mask by acid cleaning, the samples were subject to water vapor annealing to realize OH terminated diamond surface. The water vapor treatment was conducted by bubbling of N2 carrier gas through de-ionized water at 500 °C for 60 min in a quartz tube of an electric furnace. After that, 34 nm thick Al2O3 film was deposited by atomic layer deposition (ALD) process at 300 °C. Finally, Ti/Pt/Au were evaporated to form gate, drain and source electrodes and their thicknesses were 30, 30, and 100 nm, respectively. The electrical properties of the diamond MOSFET were measured with a Keithley 4200-SCS parameter analyzer at room temperature. The surface roughness of the n-type diamond body was examined with a SHIMADZU SPM-9700 atomic force microscopy (AFM). Cross-sectional transmission electron microscopy (TEM) images were obtained using a JEOL JEM-ARM200F TEM system operated at an acceleration voltage of 14.5 keV.

Inversion-type p-channel MOSFETs on heteroepitaxial diamond substrates

The Ir/intermediate layer/Si (111) substrate with a diameter of 10 mm was used to grow the heteroepitaxial diamond film using DC plasma CVD. Then, the heteroepitaxial diamond surface was mechanically polished to form the free-standing diamond substrate in 104 mm thick. After that, the free-standing heteroepitaxial diamond with size of 2 mm × 2 mm was cut from the hetero substrate to fabricate the inversion-channel diamond MOSFET. Due to the similarity of the fabrication process with the homoepitaxial diamond MOSFETs, the specific fabrication conditions would not be explained here.

Fabrication of Al2O3/p-type OH-diamond MOS capacitors on O-diamond

The OH-terminated diamond was formed on O-terminated one followed by wet annealing. Specifically, the wet annealing was performed under an atmosphere of N2 gas bubbled through ultrapure water in a quartz tube in an electric furnace at 500 °C for 60 min. Then, ALD process was performed at 300 °C to deposit a 34-nm-thick Al2O3 layer, where the thickness was confirmed by an ellipsometer for the sample with the identical ALD process on Si. Ti/Pt/Au (30 /30/ 100 nm) were then deposited to form top and bottom electrodes. All electrical properties were measured at room temperature in an ambient air atmosphere.

Fabrication of Al2O3/p-type OH-diamond MOS capacitors on H-diamond

The HPHT synthetic IIb 2.6° off-axis (111) single-crystal diamond substrate was used. In terms of the backside of diamond, a heavily boron-doped diamond layer with a concentration of ~ 1 × 1021 atom/cm3 was deposited, with the purpose of forming excellent ohmic contact. After cleaning with sulfuric–peroxide mixture, the diamond sample was subject to hydrogen plasma to form hydrogen termination in the MPCVD chamber. The pressure, microwave power, temperature and time of the plasma were 225 Torr, 800 W, 900 °C and 10 min, respectively. Then, OH-termination of wet annealing was performed at 500 °C for 60 min in a quartz tube of an electric furnace. As always, the wet ambient was formed by bubbling of N2 carrier gas through de-ionized water. Then, a Al2O3 film in 50 nm thick was deposited by ALD at 300 °C. Finally, Au electrodes were deposited to form gate and backside ohmic contacts. The circular gate electrodes were 200 μm in diameter.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

I. Akimoto, Y. Handa, K. Fukai, N. Naka, High carrier mobility in ultrapure diamond measured by time-resolved cyclotron resonance. Appl. Phys. Lett. 105, 032102 (2014)

I. Akimoto, N. Naka, N. Tokuda, Time-resolved cyclotron resonance on dislocation-free HPHT diamond. Diam. Relat. Mater. 63, 38 (2016)

C.J.H. Wort, R.S. Balmer, Diamond as an electronic material. Mater. Today 11, 22 (2008)

T. Shimomura, Y. Kubo, J. Barjon, N. Tokuda, I. Akimoto, N. Naka, Quantitative relevance of substitutional impurities to carrier dynamics in diamond. Phys. Rev. Mater. 2, 094601 (2018)

J. Isberg, J. Hammersberg, E. Johansson, T. Wikström, D.J. Twitchen, A.J. Whitehead, S.E. Coe, G.A. Scarsbrook, High carrier mobility in single-crystal plasma-deposited diamond. Science 297, 1670 (2002)

T. Iwasaki, Y. Hoshino, K. Tsuzuki, H. Kato, T. Makino, M. Ogura, D. Takeuchi, T. Matsumoto, H. Okushi, S. Yamasaki, M. Hatano, Diamond junction field-effect transistors with selectively grown n+-side gates. Appl. Phys. Express 5, 091301 (2012)

T. Iwasaki, Y. Hoshino, K. Tsuzuki, H. Kato, T. Makino, M. Ogura, D. Takeuchi, H. Okushi, S. Yamasaki, M. Hatano, High-temperature operation of diamond junction field-effect transistors with lateral p-n junctions. IEEE Electron. Device Lett. 34, 1175 (2013)

H. Kato, K. Oyama, T. Makino, M. Ogura, D. Takeuchi, S. Yamasaki, Diamond bipolar junction transistor device with phosphorus-doped diamond base layer. Diam. Relat. Mater. 27–28, 19 (2012)

H. Kato, T. Makino, M. Ogura, D. Takeuchi, S. Yamasaki, Fabrication of bipolar junction transistor on (001)-oriented diamond by utilizing phosphorus-doped n-type diamond base. Diam. Relat. Mater. 34, 41 (2013)

H. Umezawa, K. Hirama, T. Arai, H. Hata, H. Takayanagi, T. Koshiba, K. Yohara, S. Mejima, M. Satoh, K.S. Song, H. Kawarada, RF diamond transistors: current status and future prospects. Jpn. J. Appl. Phys. 44, 7789 (2005)

H. Umezawa, Recent advances in diamond power semiconductor devices. Mater. Sci. Semicond. Process. 78, 147 (2018)

T. Matsumoto, T. Mukose, T. Makino, D. Takeuchi, S. Yamasaki, T. Inokuma, N. Tokuda, Diamond Schottky-pn diode using lightly nitrogen-doped layer. Diam. Relat. Mater. 75, 152 (2017)

T. Makino, S. Tanimoto, Y. Hayashi, H. Kato, N. Tokuda, M. Ogura, D. Takeuchi, K. Oyama, H. Ohashi, H. Okushi, S. Yamasaki, Diamond Schottky-pn diode with high forward current density and fast switching operation. Appl. Phys. Lett. 94, 262101 (2009)

K. Hirama, H. Sato, Y. Harada, H. Yamamoto, M. Kasu, Diamond field-effect transistors with 1.3 A/mm drain current density by Al2O3 passivation layer. Jpn. J. Appl. Phys. 51, 090112 (2012)

H. Kawarada, T. Yamada, D. Xu, H. Tsuboi, Y. Kitabayashi, D. Matsumura, M. Shibata, T. Kudo, M. Inaba, A. Hiraiwa, Durability-enhanced two-dimensional hole gas of C-H diamond surface for complementary power inverter applications. Sci. Rep. 7, 42368 (2017)

J. Liu, M. Liao, M. Imura, A. Tanaka, H. Iwai, Y. Koide, Low on-resistance diamond field effect transistor with high-k ZrO2 as dielectric. Sci. Rep. 4, 6395 (2014)

J. Liu, H. Ohsato, X. Wang, M. Liao, Y. Koide, Design and fabrication of high-performance diamond triple-gate field-effect transistors. Sci. Rep. 6, 34757 (2016)

M. Inaba, T. Muta, M. Kobayashi, T. Saito, M. Shibata, D. Matsumura, T. Kudo, A. Hiraiwa, H. Kawarada, Hydrogen-terminated diamond vertical-type metal oxide semiconductor field-effect transistors with a trench gate. Appl. Phys. Lett. 109, 033503 (2016)

Z. Ren, J. Zhang, J. Zhang, C. Zhang, S. Xu, Y. Li, Y. Hao, Diamond field effect transistors with MoO3 gate dielectric. IEEE Electron. Device Lett. 38, 786 (2017)

Z. Ren, G. Yuan, J. Zhang, L. Xu, J. Zhang, W. Chen, Y. Hao, Hydrogen-terminated polycrystalline diamond MOSFETs with Al2O3 passivation layers grown by atomic layer deposition at different temperatures. AIP Adv. 8, 065026 (2018)

J. Liu, O. Auciello, E. de Obaldia, B. Da, Y. Koide, Science and technology of integrated super-high dielectric constant AlOx/TiOy nanolaminates/diamond for MOS capacitors and MOSFETs. Carbon 172, 112 (2021)

J.W. Liu, H. Oosato, B. Da, T. Teraji, A. Kobayashi, H. Fujioka, Y. Koide, Operations of hydrogenated diamond metal-oxide-semiconductor field-effect transistors after annealing at 500 °C. J. Phys. D. Appl. Phys. 52, 315104 (2019)

J. Liu, Y. Koide, An overview of high-k oxides on hydrogenated-diamond for metal-oxide-semiconductor capacitors and field-effect transistors. Sensors 18, 1813 (2018)

N. Oi, M. Inaba, S. Okubo, I. Tsuyuzaki, T. Kageura, S. Onoda, A. Hiraiwa, H. Kawarada, Vertical-type two-dimensional hole gas diamond metal oxide semiconductor field-effect transistors. Sci. Rep. 8, 10660 (2018)

M. Iwataki, N. Oi, K. Horikawa, S. Amano, J. Nishimura, T. Kageura, M. Inaba, A. Hiraiwa, H. Kawarada, Over 12000 A/cm2 and 3.2 mΩ cm2 miniaturized vertical-type two-dimensional hole gas diamond MOSFET. IEEE Electron Device Lett. 41, 111 (2020)

T.T. Pham, N. Rouger, C. Masante, G. Chicot, F. Udrea, D. Eon, E. Gheeraert, J. Pernot, Deep depletion concept for diamond MOSFET. Appl. Phys. Lett. 111, 173503 (2017)

T.T. Pham, J. Pernot, G. Perez, D. Eon, E. Gheeraert, N. Rouger, Deep-depletion mode Boron-doped monocrystalline diamond metal oxide semiconductor field effect transistor. IEEE Electron. Device Lett. 38, 1571 (2017)

C. Masante, N. Rouger, J. Pernot, Recent progresses in deep depletion diamond metal oxide semiconductor field effect transistor. J. Phys. D 54, 233002 (2021)

J.W. Liu, M.Y. Liao, M. Imura, Y. Koide, Normally-off HfO2-gated diamond field effect transistors. Appl. Phys. Lett. 103, 092905 (2013)

Y. Kitabayashi, T. Kudo, H. Tsuboi, T. Yamada, D. Xu, M. Shibata, D. Matsumura, Y. Hayashi, M. Syamsul, M. Inaba, A. Hiraiwa, H. Kawarada, Normally-off C-H diamond MOSFETs with partial C-O Channel achieving 2-kV Breakdown Voltage. IEEE Electron. Device Lett. 38, 363 (2017)

T. Suwa, T. Iwasaki, K. Sato, H. Kato, T. Makino, M. Ogura, D. Takeuchi, S. Yamasaki, M. Hatano, Normally-off diamond junction field-effect transistors with submicrometer channel. IEEE Electron. Device Lett. 37, 209 (2016)

T. Iwasaki, H. Kato, T. Makino, M. Ogura, D. Takeuchi, S. Yamasaki, M. Hatano, High-temperature bipolar-mode operation of normally-off diamond JFET. IEEE J. Electron. Devices Soc. 5, 95 (2017)

T. Matsumoto, H. Kato, K. Oyama, T. Makino, M. Ogura, D. Takeuchi, T. Inokuma, N. Tokuda, S. Yamasaki, Inversion channel diamond metaloxide-semiconductor field-effect transistor with normally off characteristics. Sci. Rep. 6, 31585 (2016)

T. Matsumoto, H. Kato, T. Makino, M. Ogura, D. Takeuchi, S. Yamasaki, T. Inokuma, N. Tokuda, Inversion channel mobility and interface state density of diamond MOSFET using N-type body with various phosphorus concentrations. Appl. Phys. Lett. 114, 242101 (2019)

X. Zhang, T. Matsumoto, Y. Nakano, H. Noguchi, H. Kato, T. Makino, D. Takeuchi, M. Ogura, S. Yamasaki, C.E. Nebel, T. Inokuma, N. Tokuda, Inversion channel MOSFET on heteroepitaxially grown free-standing diamond. Carbon 175, 615 (2021)

T. Matsumoto, H. Kato, T. Makino, M. Ogura, D. Takeuchi, S. Yamasaki, M. Imura, A. Ueda, T. Inokuma, N. Tokuda, Direct observation of inversion capacitance in p-type diamond MOS capacitors with an electron injection layer. Jpn. J. Appl. Phys. 57, 04FR01 (2018)

R. Yoshida, D. Miyata, T. Makino, S. Yamasaki, T. Matsumoto, T. Inokuma, N. Tokuda, Formation of atomically flat hydroxyl-terminated diamond (111) surfaces via water vapor annealing. Appl. Surf. Sci. 458, 222 (2018)

X. Zhang, T. Matsumoto, U. Sakurai, T. Makino, M. Ogura, S. Yamasaki, M. Sometani, D. Okamoto, H. Yano, N. Iwamuro, T. Inokuma, N. Tokuda, Energy distribution of Al2O3/diamond interface states characterized by high temperature capacitance-voltage method. Carbon 168, 659 (2020)

X. Zhang, T. Matsumoto, U. Sakurai, T. Makino, M. Ogura, Insight into Al2O3/B-doped diamond interface states with high-temperature conductance method. Appl. Phys. Lett. 117, 092104 (2020)

S.M. Sze, K.K. Ng, Physics of Semiconductor Devices, 3rd edn. (Wiley, New York, 2007)

H. Kato, M. Ogura, T. Makino, D. Takeuchi, S. Yamasaki, N-type control of single-crystal diamond films by ultra-lightly phosphorus doping. Appl. Phys. Lett. 109, 142102 (2016)

W. Fei, T. Bi, M. Iwataki, S. Imanishi, H. Kawarada, Oxidized Si terminated diamond and its MOSFET operation with SiO2 gate insulator. Appl. Phys. Lett. 116, 212103 (2020)

Y. Sasama, T. Kageura, M. Imura, K. Watanabe, T. Taniguchi, T. Uchihashi, Y. Takahide, High-mobility p-channel wide bandgap transistors based on h-BN/diamond heterostructures. arXiv Prepr. arXiv 2102, 05982 (2021)

Y. Sasama, T. Kageura, K. Komatsu, S. Moriyama, J.I. Inoue, M. Imura, K. Watanabe, T. Taniguchi, T. Uchihashi, Y. Takahide, Charge-carrier mobility in hydrogen-terminated diamond field-effect transistors. J. Appl. Phys. 127, 185707 (2020)

C. Bednarski, Z. Dai, A.P. Li, B. Golding, Studies of heteroepitaxial growth of diamond. Diam. Relat. Mater. 12, 241 (2003)

J.C. Arnault, Highly oriented diamond films on heterosubstrates: current state of the art and remaining challenges. Surf. Rev. Lett. 10, 127 (2003)

T. Murooka, J. Yaita, T. Makino, M. Ogura, H. Kato, S. Yamasaki, M. Natal, S.E. Saddow, T. Iwasaki, M. Hatano, Characterization of Schottky barrier diodes on heteroepitaxial diamond on 3C-SiC/Si Substrates. IEEE Trans. Electron. Devices 67, 212 (2020)

M. Syamsul, N. Oi, S. Okubo, T. Kageura, H. Kawarada, Heteroepitaxial diamond field-effect transistor for high voltage applications. IEEE Electron. Device Lett. 39, 51 (2018)

Z. Dai, C. Bednarski-Meinke, B. Golding, Heteroepitaxial diamond film growth: the a-plane sapphire-iridium system. Diam. Relat. Mater. 13, 552 (2004)

Y. Ando, J. Kuwabara, K. Suzuki, A. Sawabe, Patterned growth of heteroepitaxial diamond. Diam. Relat. Mater. 13, 1975 (2004)

N. Vaissiere, S. Saada, M. Bouttemy, A. Etcheberry, P. Bergonzo, J.C. Arnault, Heteroepitaxial diamond on iridium: New insights on domain formation. Diam. Relat. Mater. 36, 16 (2013)

M. Schreck, J. Asmussen, S. Shikata, J.C. Arnault, N. Fujimori, Large-area high-quality single crystal diamond. MRS Bull. 39, 504 (2014)

H. Aida, S.W. Kim, K. Ikejiri, Y. Kawamata, K. Koyama, H. Kodama, A. Sawabe, Fabrication of freestanding heteroepitaxial diamond substrate via micropatterns and microneedles. Appl. Phys. Express 9, 035504 (2016)

H. Kawashima, H. Noguchi, T. Matsumoto, H. Kato, M. Ogura, T. Makino, S. Shirai, D. Takeuchi, S. Yamasaki, Electronic properties of diamond Schottky barrier diodes fabricated on silicon-based heteroepitaxially grown diamond substrates. Appl. Phys. Express 8, 104103 (2015)

B.C. Gallheber, M. Fischer, M. Mayr, J. Straub, M. Schreck, Growth, stress, and defects of heteroepitaxial diamond on Ir/YSZ/Si. J. Appl. Phys. 123, 22302 (2018)

K. Ichikawa, K. Kurone, H. Kodama, K. Suzuki, A. Sawabe, High crystalline quality heteroepitaxial diamond using grid-patterned nucleation and growth on Ir. Diam. Relat. Mater. 94, 92 (2019)

S. Takagi, A. Toriumi, M. Iwase, H. Tango, On the universality of inversion layer mobility in Si MOSFET’s: Part I—effects of substrate impurity concentration. IEEE Trans. Electron Devices 41, 2357 (1994)

G. Daligou, J. Pernot, 2D hole gas mobility at diamond/insulator interface. Appl. Phys. Lett. 116, 162105 (2020)

Y. Li, J.F. Zhang, G.P. Liu, Z.Y. Ren, J.C. Zhang, Y. Hao, Mobility of two-dimensional hole gas in H-terminated diamond. Phys. Status Solidi 12, 1700401 (2018)

H. Umezawa, T. Arima, N. Fujihara, H. Taniuchi, H. Ishizaka, M. Tachiki, C. Wild, P. Koidl, H. Kawarada, RF performance of high transconductance and high-channel-mobility surface-channel polycrystalline diamond metal-insulator-semiconductor field-effect transistors. Japanese J. Appl. Phys. Part 1 Regul. Pap. Short Notes Rev. Pap. 41, 2611 (2002)

M. Syamsul, Y. Kitabayashi, T. Kudo, D. Matsumura, H. Kawarada, High voltage stress induced in transparent polycrystalline diamond field-effect transistor and enhanced endurance using thick Al2O3 passivation Layer. IEEE Electron. Device Lett. 38, 607 (2017)

N.C. Saha, T. Oishi, S. Kim, Y. Kawamata, K. Koyama, M. Kasu, 145-MW/cm2 heteroepitaxial diamond MOSFETs with NO2 p-type doping and an Al2O3 passivation layer. IEEE Electron. Device Lett. 41, 1066 (2020)

N. Tokuda, H. Umezawa, S.G. Ri, M. Ogura, K. Yamabe, H. Okushi, S. Yamasaki, Atomically flat diamond (111) surface formation by homoepitaxial lateral growth. Diam. Relat. Mater. 17, 1051 (2008)

N. Tokuda, H. Umezawa, K. Yamabe, H. Okushi, S. Yamasaki, Growth of atomically step-free surface on diamond 111 mesas. Diam. Relat. Mater. 19, 288 (2010)

N. Tokuda, T. Makino, T. Inokuma, S. Yamasaki, Formation of step-free surfaces on diamond (111) mesas by homoepitaxial lateral growth. Jpn. J. Appl. Phys. 51, 090107 (2012)

K. Nakanishi, H. Kuroshima, T. Matsumoto, T. Inokuma, N. Tokuda, Atomically flat diamond (100) surface formation by anisotropic etching of solid-solution reaction of carbon into nickel. Diam. Relat. Mater. 68, 127 (2016)

N. Tokuda, M. Ogura, S. Yamsaki, T. Inokuma, Anisotropic lateral growth of homoepitaxial diamond (111) films by plasma-enhanced chemical vapor deposition. Jpn. J. Appl. Phys. 53, 04EH04 (2014)

N. Tokuda, M. Ogura, T. Matsumoto, S. Yamasaki, T. Inokuma, Influence of substrate misorientation on the surface morphology of homoepitaxial diamond (111) films. Phys. Status Solidi 213, 2051 (2016)

J.C. Zheng, X.N. Xie, A.T.S. Wee, K.P. Loh, Oxygen-induced surface state on diamond (100). Diam. Relat. Mater. 10, 500 (2001)

Y. Itoh, Y. Sumikawa, H. Umezawa, H. Kawarada, Trapping mechanism on oxygen-terminated diamond surfaces. Appl. Phys. Lett. 89, 203503 (2006)

Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P.C. McIntyre, P.M. Asbeck, M.J.W. Rodwell, Y. Taur, A distributed model for border traps in Al2O3-InGaAs MOS devices. IEEE Electron Device Lett. 32, 485 (2011)

Y. Yuan, B. Yu, J. Ahn, P.C. McIntyre, P.M. Asbeck, M.J.W. Rodwell, Y. Taur, A distributed bulk-oxide trap model for Al2O3-InGaAs MOS devices. IEEE Trans. Electron Devices 59, 2100 (2012)

X. Zhang, D. Okamoto, T. Hatakeyama, M. Sometani, S. Harada, R. Kosugi, N. Iwamuro, H. Yano, Characterization of near-interface traps at 4H-SiC metal–oxide–semiconductor interfaces using modified distributed circuit model. Appl. Phys. Express 10, 064101 (2017)

X. Zhang, D. Okamoto, T. Hatakeyama, M. Sometani, S. Harada, N. Iwamuro, H. Yano, Impact of oxide thickness on the density distribution of near-interface traps in 4H-SiC MOS capacitors. Jpn. J. Appl. Phys. 57, 06KA04 (2018)

C.C. Cheng, C.H. Chien, G.L. Luo, J.C. Liu, Y.C. Chen, Y.F. Chang, S.Y. Wang, C.C. Kei, C.N. Hsiao, C.Y. Chang, Five-element circuit model using linear-regression method to correct the admittance measurement of metal-oxide-semiconductor capacitor. J. Vac. Sci. Technol. B 27, 130 (2009)

C.N. Berglund, Surface states at steam-grown silicon-silicon dioxide interfaces. IEEE Trans. Electron Devices 13, 701 (1966)

H. Yoshioka, T. Nakamura, T. Kimoto, Characterization of very fast states in the vicinity of the conduction band edge at the SiO2/SiC interface by low temperature conductance measurements. J. Appl. Phys. 115, 014502 (2014)

N. Taoka, M. Yokoyama, S.H. Kim, R. Suzuki, T. Hoshii, R. Iida, S. Lee, Y. Urabe, N. Miyata, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Takenaka, S. Takagi, AC response analysis of C-V curves and quantitative analysis of conductance curves in Al2O3/InP interfaces. Microelectron. Eng. 88, 1087 (2011)

E.H. Nicollian, A. Goetzberger, Bell Syst. Tech. J. 46, 1055 (1967)

E.H. Nicollian, J.R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology (Wiley, New York, 1982)

K.K. Hung, Y.C. Cheng, Characterization of Si-SiO2 interface traps in p-metal-oxide-semiconductor structures with thin oxides by conductance technique. J. Appl. Phys. 62, 4204 (1987)

N. Taoka, K. Ikeda, W. Mizubayashi, Y. Morita, S. Migita, H. Ota, S. Takagi, Accurate evaluation of Ge metal-insulator-semiconductor interface properties. J. Appl. Phys. 110, 064506 (2011)

N. Taoka, T. Yamada, M. Shimizu, Impacts of Al2O3/GaN interface properties on the screening effect and carrier mobility in an inversion layer. Jpn. J. Appl. Phys. 58, SAAF03 (2019)

T.T. Pham, A. Maréchal, P. Muret, D. Eon, E. Gheeraert, N. Rouger, J. Pernot, Comprehensive electrical analysis of metal/Al2O3/O-terminated diamond capacitance. J. Appl. Phys. 123, 1623 (2018)

N.C. Saha, M. Kasu, Heterointerface properties of diamond MOS structures studied using capacitance–voltage and conductance–frequency measurements. Diam. Relat. Mater. 91, 219 (2019)

J.R. Brews, Rapid interface parameterization using a single MOS conductance curve. Solid State Electron. 26, 711 (1983)

Y. Karamoto, X. Zhang, D. Okamoto, M. Sometani, T. Hatakeyama, S. Harada, N. Iwamuro, H. Yano, Analysis of fast and slow responses in AC conductance curves for p-type SiC MOS capacitors. Jpn. J. Appl. Phys. 57, 06KA06 (2018)

W. Shockley, W.T. Read, Statistics of the recombinations of holes and electrons. Phys. Rev. 87, 835 (1952)

T. Kimoto, J.A. Cooper, Fundamentals of Silicon Carbide Technology (Wiley, Singapore, 2014)

N. Kawakami, Y. Yokota, T. Tachibana, K. Hayashi, K. Kobashi, Atomic layer deposition of Al2O3 thin films on diamond. Diam. Relat. Mater. 14, 2015 (2005)

M.W. Geis, J.A. Gregory, B.B. Pate, Capacitance-voltage measurements on metal-SiO2-diamond structures fabricated with (100)- and (111)-oriented substrates. IEEE Trans. Electron. Devices 38, 619 (1991)

P.M. Lenahan, P.V. Dressendorfer, An electron spin resonance study of radiation-induced electrically active paramagnetic centers at the Si/SiO2 interface. J. Appl. Phys. 54, 1457 (1983)

T. Umeda, M. Okamoto, H. Yoshioka, G.-W. Kim, S. Ma, R. Arai, T. Makino, T. Ohshima, S. Harada, Interface defects in C-face 4H-SiC MOSFETs: an electrically-detected-magnetic-resonance study. ECS. Trans 80, 147 (2017)

M. Nagai, K. Nakanishi, H. Takahashi, H. Kato, T. Makino, S. Yamasaki, T. Matsumoto, T. Inokuma, N. Tokuda, Anisotropic diamond etching through thermochemical reaction between Ni and diamond in high-Temperature water vapour. Sci. Rep. 8, 6687 (2018)

M. Nagai, Y. Nakamura, T. Yamada, T. Tabakoya, T. Matsumoto, T. Inokuma, C.E. Nebel, T. Makino, S. Yamasaki, N. Tokuda, Formation of U-shaped diamond trenches with vertical 111 sidewalls by anisotropic etching of diamond (110) surfaces. Diam. Relat. Mater. 103, 107713 (2020)

Acknowledgments

This work was partially supported by Adaptable and Seamless Technology transfer Program through Target-driven R&D (A-STEP) from Japan Science and Technology Agency (JST), Kanazawa University SAKIGAKE Project 2020, a NEDO Feasibility Study Program (Uncharted Territory Challenge 2050) grant number 19101600-0, and JSPS KAKENHI grant numbers JP18KK0383, JP19K15042, and JP20K14773.

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interest.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Zhang, X., Matsumoto, T., Yamasaki, S. et al. Inversion-type p-channel diamond MOSFET issues. Journal of Materials Research 36, 4688–4702 (2021). https://doi.org/10.1557/s43578-021-00317-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1557/s43578-021-00317-z