Abstract

To accommodate the ever-growing data requirements in densely populated areas and address the need for high-resolution sensing in diverse next-generation applications, there is a noticeable trend towards utilizing large unallocated frequency bands above 100 GHz. To overcome the harsh propagation conditions, large-scale antenna arrays are crucial and urge the need for cost-effective, mass-manufacturable technologies. A dedicated Any-Layer High Density Interconnect PCB technology for highly efficient wireless D-band (110–170 GHz) systems is proposed. Specifically, the adapted stack accommodates broadband air-filled substrate-integrated-waveguide components for efficient long-range signal distribution and low-loss passives. The viability of the suggested technology platform is demonstrated by designing, fabricating and measuring several essential low-loss air-filled substrate-integrated-waveguide components, such as a dual rectangular filter, with a minimal insertion loss of 0.87 dB and 10 dB-matching within the (132.8–139.2 GHz) frequency band, and an air-filled waveguide with a routing loss of only 0.08 dB/mm and a flat amplitude variation within 0.01 dB/mm over the (115–155 GHz) frequency range. A broadband transition towards stripline, with a limited loss of 1.1 dB, is described to interface these waveguides with compactly integrated chips. A tolerance analysis is included as well as a comparison to the state of the art.

Similar content being viewed by others

Introduction

Adding sensing capabilities to the future communications network will greatly improve overall safety in a wide variety of situations and will facilitate reliable spatial signal distribution. To this end, joint communication and sensing (JCAS) in 6G networks enables massive machine-to-machine (M2M) communications, for example on the road for object detection and traffic monitoring, or on a factory ground to ensure machine-safety for operators1,2. The increasing resolution for next-generation radar systems and the growing data demand, both in terms of bandwidth and data rate, which originate from the aforementioned paradigm, force technology to explore the higher sub- and terahertz frequency spectrum where large chunks of the spectrum are still unallocated. Beneficial atmospheric properties, even in rainy conditions, favor D-band (110–170 GHz) frequencies for emerging systems3. The latest research achieves datarates up to 150 Gbps in this band, resulting in a hundredfold throughput increase compared to our current network speed4.

The deployment of antenna arrays to overcome increased path loss when upscaling to higher frequencies introduces its own challenges5,6,7,8. On the one hand, the required power handling capability for future systems, next to low-loss routing towards the antenna elements, advocates air-filled substrate-integrated-waveguide (AFSIW) transmission line technology9,10,11. Cost-effective mass-manufacturability and integration prospects of active electronics, on the other hand, restrict the fabrication technology further. To this end, an elaborate comparison between existing technology platforms is discussed and summarized in Table 1. The most traditional high-precision fabrication process with excellent repeatability is computer numerical controlled (CNC) milling. The resulting prototypes are commonly constructed out of aluminum or a steel alloy, which may be gold plated to improve the conductivity and avoid potential detrimental effects of the magnetic properties of the base material12,13,14,15,16,17. Interfacing monolithic microwave integrated circuits (MMICs) proves to be quite cumbersome, while manufacturing is done sequentially and remains expensive for high-accuracy parts, reducing the scalability towards mass-production. Excellent surface roughness is achieved by polishing at the cost of an expensive time consuming process. A low-cost, chemical metal etching process alternative10 with similar insertion loss has been proposed to tackle equivalent hurdles. However, the prospects of MMIC integration remains an obstacle. The stereolithograpy (SLA) and direct metal laser sintering (DMLS), also called micro metal laser sintering (\(\mu\)MLS) or selective laser melting (SLM), 3D-printing technologies provide an alternative to counter the material waste of milling18,19,20,21,22,23,24. In contrast to DMLS-prints, the intermediate SLA resin samples have to be plated before a functional prototype is obtained. The feature size and surface roughness are mainly limited to the particle size, in case of DMLS, and to the laser properties, in case of SLA. Injection molding provides a scalable alternative for high volume productions. Promoting this technology for commercial future terahertz systems requires solving the current pitfalls of demoulding defects and the limited aspect ratio25,26,27,28. Excellent feature size and aspect ratio are obtained with SU-8 and silicon micromachining fabrication. Where mechanical stability and poor thermal properties constitute the main drawbacks of SU-8 technology13,29,30,31,32, a pitfall of the silicon micromachined waveguide (SMW) process is the cost14,33,34,35,36,37,38. For both approaches, compact MMIC integration is very challenging due to the presence of silicon, leading to high interface losses and reduced bandwidth11, and the additional need for dense networks to distribute DC and control signals to all MMICs4. Furthermore, low temperature co-fired ceramics (LTCC) technology allows development of (partial) dielectric antenna topologies, although at the cost of high losses due to its high relative permittivity39,40,41. The limited thickness of the ceramic substrates requires stacking multiple layers, making the process prone to fabrication defects, warpage and alignment errors. Finally, multiple printed circuit board (PCB)-based D-band multi-antenna systems have been proposed5,8,42. While promising results are obtained, they suffer from considerable routing losses due to the use of conventional transmission line technology, leading to a degraded noise figure at the receive side, reduced effective isotropic radiated power (EIRP) at transmit side and a restriction on the amount of supported antenna elements.

In this paper, we present an innovative cost-effective PCB-based technology platform that enables the implementation of highly efficient AFSIW-based routing and compact integration of active electronics. Two transitions, one from grounded coplanar waveguide (GCPW) to stripline, and, one from stripline to AFSIW, are designed to access the low-loss AFSIW section. In this region, transmission lines of different lengths and functional components, such as a filter, are designed in AFSIW to validate the proof of concept. Comparing different line lengths allows extracting the measured transmission loss, which remains around 0.08 dB/mm in the entire D-band. Furthermore, the stripline-to-AFSIW transition exhibits 1.1 dB-loss, characterized by comparing the different calibration planes for a single line length. The proposed two-cavity filter showcases the reliability of the fabrication process for more complex AFSIW components. This component has a footprint of 5.2 mm \(\times\) 2.2 mm \(\times\) 300 \({\upmu }\)m, a minimal measured insertion loss of 0.9 dB at 136 GHz, with a 10 dB impedance matching bandwidth ranging from 132.9 to 139.2 GHz and a group delay smaller than 0.07 ns. The main characteristics of this novel technology platform are compared to existing state-of-the-art D-band technology platforms in Table 1, including only the best results employing optimal fabrication processes for the latter. By eliminating dielectric losses, the employed AFSIW layer allows significant reduction of the insertion loss w.r.t. Any-Layer High Density Interconnect (HDI) PCB and LTCC technology. It can be seen that our proposed PCB technology platform with a dedicated AFSIW layer offers a low-cost, mass-manufacturable alternative at D-band frequencies that facilitates compact MMIC integration versus CNC milling, (\(\mu\)MLS), injection molding, SU-8 or SMW, paving the way for future cost-effective, highly integrated wideband and low-loss JCAS systems43,44.

Leveraging an air substrate for the implementations of high-efficiency microwave components in PCB technology, such as filters, beamsteering networks and antennas, is well established at sub-6 GHz and lower millimeterwave frequencies45,46,47,48,49. These proposed solutions make use of cheap standard PCB manufacturing technology and achieve their multi-layer stack-up by manually aligning and fixing with screws. This approach is cumbersome for beyond 100 GHz frequencies. Therefore, we suggest to evolve towards multi-layer PCB manufacturing to avoid manual alignment, screws or solder. In this respect, the significant routing losses of the current PCB implementations at D-band (110–170 GHz) highlight the importance of adding a highly efficient AFSIW routing layer, as introduced in our proposed solution. This article extends previously published work50, by discussing the technology platform in more detail, performing an in-depth tolerance analysis and validation of fabricated air-filled components, showcasing the viability of more complex AFSIW component, such as filters, and comparing the proposed solution to the current state of the art at the component and the technology level.

System technology

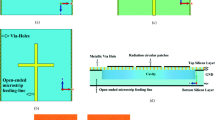

Future system platform implementations need to minimize signal insertion loss when distributing high-frequency signals in large-scale active antenna arrays, while maintaining good power handling. Therefore, we implement air cavities in the middle layer of the PCB stack, as illustrated in Fig. 1, to realize waveguides, filters, antenna cavities and other essential components in a low-loss way, by eliminating dielectric losses. Besides this highly efficient AFSIW layer, which may be used, among others, for signal routing, a low-loss transition to GCPW is present for integration of active devices and measurement purposes50. Moreover, a symmetrical stack is proposed for the ease of manufacturing and to reduce the thermal stress when mounting active electronics.

The Any-Layer HDI PCB technology, forming the starting point of our proposed technology platform, is a new generation of the standard HDI PCB technology51 that enables the stacking of lasered microvias52. This allows connecting each individual layer, enhancing the routing possibilities, along with improved fabrication resolution53. We build further up on the Any-Layer HDI PCB technology by including an AFSIW layer, to alleviate the routing loss of this technology, whilst maintaining equivalent fabrication processes54 to guarantee compliance with the standard55. In particular, the incorporation of the AFSIW layer involves following steps. First, a core laminate \(\textcircled {1}\) is patterned, followed by the attachment of a thick prepreg laminate \(\textcircled {2}\), in which the AFSIW is lasered and edge-plated. Thereafter, another patterned core layer \(\textcircled {3}\), of the same thickness as the first layer \(\textcircled {1}\), is attached by means of a sintering process after correct alignment w.r.t. the first two layers55. After eliminating dielectric losses, this approach further reduces insertion loss by minimizing the surface roughness of the top and bottom walls of the air-filled components. As the electromagnetic fields propagate in the air-filled region, the surface roughness of the copper foil at the copper/air-cavity interface needs to be considered, in contrast to conventional dielectric-filled substrate-integrated-waveguide (DFSIW) structures where the surface roughness at the conductor/substrate interface needs to be taken into account. The surface roughness at the conductor/substrate interface is typically substantially larger than the surface roughness of the copper foils at the conductor/air-cavity interface to ensure good adhesion of the copper foil to the laminate56. To maintain symmetry, each additional prepreg layer \(\textcircled {4}\) is added by aligning and pressing51 on both sides of the current PCB stack and with equal thickness until the required amount of layers is achieved for the envisaged application. The top layers, above the laminate containing the AFSIW \(\textcircled {2}\), facilitate the integration of wideband antenna topologies. The bottom layers enable the routing towards the integrated circuit (IC), including heat sinks to subdue thermal issues. Note the trade-off considered when fixing the thickness of the AFSIW layer: a higher cavity may exhibit a higher Q-factor, whereas a lower cavity enables essentially lower loss in terms of transition towards surrounding layers. Here, we focus on the development of a test vehicle to validate the performance of the proposed manufacturing process, demonstrating its potential as cost-effective alternative to SMW platforms for future sub-terahertz systems.

AFSIW components

The adopted Any-Layer HDI PCB stack is presented in this section, followed by an in-depth analysis of the AFSIW transmission line, the transition from stripline to AFSIW, employed for measurements and MMIC integration prospects, and the AFSIW dual rectangular cavity filter.

PCB Stack

All aforementioned considerations of the system technology are taken into account when dimensioning the proposed PCB stack. The thickness of each layer is indicated on the right of Fig. 2, together with the order in which the layers are added. The employed process warrants fabrication tolerances down to 10 \(\upmu\)m for the smallest AFSIW features, such as inductive irises. However, reliable laser-milling and edge-plating imposes a minimal protrusion width of 0.25 mm. This criterion is equally employed as diameter to round off all sharp corners. The features implemented through etching on the conductor layers are precisely manufactured up to 10 \(\upmu\)m.

Adopted PCB stack, where the top four layers are intended for future antenna array implementations. A ground–signal–ground (GSG) probe allows measuring the device under test (DUT), whereas the grounded coplanar waveguide (GCPW) to stripline (STL) transition and the STL to air-filled substrate-integrated-waveguide (AFSIW) transition allow calibration up to two different port planes (CAL1 and CAL2).

Two transitions, transmission lines of different lengths and more complex AFSIW structures, such as filters, are designed following the aforementioned guidelines to validate this PCB stack. For measurement purposes, a GCPW landing pad is currently implemented as an interface to a ground–signal–ground (GSG) probe, which connects to a short GCPW section. In a later stage, these landing pads are to be replaced by MMICs. This results in the signal flows indicated by the red arrows in Fig. 2. A first transition from the short GCPW section to the stripline, integrated on laminates \(\textcircled {3}\) and \(\textcircled {4}\), allows initial, very compact routing, splitting and combining of the RF signals. The stripline interconnect transitions into the AFSIW components through aperture coupling, which represents the second transition. To extract the maximum amount of characterization data when validating this stack, two additional thru-reflect-line (TRL) calibration sets57 are added: one de-embeds up to the stripline section (indicated by CAL1 in Fig. 2), and the other shifts the port plane into the AFSIW transmission line (indicated by CAL2). To this end, each calibration set consists of three standards: a thru, a short that acts as reflect, and a line of which the phase difference with the thru standard remains within [20\(^\circ\), 160\(^\circ\)] to ensure unambiguous TRL calibration.

Air-filled substrate-integrated-waveguide

(a) The cross-section of the AFSIW transmission lines with indicated dimensions in millimeter. The influence on the transmission coefficient due to (b) variations in height (H), width (W) and slant sidewall angle (\(\varphi\)) for a length of 5 cm, and, (c) the surface roughness variations for line lengths of 5 cm and 10 cm.

In this section, the AFSIW transmission lines of two different lengths are analyzed, through full-wave simulations in CST Microwave Studio, based on the cross-section in Fig. 3a. Simulations of the 5 cm-long transmission line, which corresponds to \(23.35\lambda _{140\, \text {GHz}, 0}\) in terms of the free-space wavelength at 140 GHz, in Fig. 3b, c, show robust behavior against a change in width or sidewall angle. However, an AFSIW height increase yields an improvement in terms of insertion loss, as can be observed in Fig. 3b. The major influence of the surface roughness is shown for two line lengths, 5 cm and 10 cm, in Fig. 3c. As expected, we find that the insertion loss doubles for the 10 cm-line when compared to the 5 cm-line. Moreover, each 200 nm increase in surface roughness gives rise to an additional 0.01 dB/mm insertion loss. The reflection coefficient remains below − 40 dB for all simulated AFSIW lines.

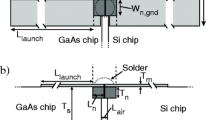

Transition from stripline to air-filled substrate-integrated-waveguide

A transition from AFSIW to stripline is designed to supply compact routing features on the one hand, but more importantly, to enable the integration of active electronics and measurements on the other hand. The robustness of the design is ensured for misalignments up to 20 \(\upmu\)m between the laminate containing the coupling slot \(\textcircled {3}\), and the laminate containing the AFSIW \(\textcircled {2}\), resulting in a variation in insertion loss smaller than ± 0.02 dB over the entire D-band. To minimize transition loss and ensure maximal routing flexibility, it is important to keep the transition length as short as possible. However, the minimal transition length is restricted by the minimal technologically achievable distance between the shorting via at the end of the stripline and the coupling slot towards the AFSIW. The proposed design50 exhibits a transition length of only 0.775 mm, which is equivalent to \(0.36\lambda _{140 \,\text {GHz}, 0}\) in terms of the free-space wavelength at 140 GHz. The edge-plated lasercut laminates and the patterning of all relevant conductors in the proposed PCB stack are illustrated in Fig. 4a, employing the same color coding and build up as in Fig. 2.

(a) AFSIW-to-stripline transition layout50, (b) influence of AFSIW height variations on scattering parameters (dashed |S\(_{11}|\), solid |S\(_{12}|\) = |S\(_{21}|\) and dotted |S\(_{22}|\)).

It is important to analyze the influence of the height of laminate \(\textcircled {3}\), containing the AFSIW components. The resulting S-parameters for height variations of ± 40 \(\upmu\)m are presented in Fig. 4b, showing a degradation in matching as soon as a height deviation occurs, since coupling of the fields into the AFSIW becomes more troublesome. The larger this deviation, the worse the matching, which also leads to an increased insertion loss, indicated in the zoomed part of Fig. 4b. After identification of the actual height, this can be corrected for by re-optimizing the shorting position of the stripline and the coupling slot dimensions towards the AFSIW to improve the matching.

Filter design

The fabrication of more intricate structures, including protrusions and varying cavity dimensions, are included in a representative D-band system design to validate the proposed PCB stack. A proof of concept consists of a dual rectangular cavity filter, since filters are important elements in the next-generation systems for the exclusion of spurious signals and the reduction of noise. A bandwidth of 6 GHz centered around 135 GHz58 is targeted, with a flat transmission response in which the insertion loss remains smaller than 1 dB. In this section, the corresponding theoretical coupling matrix model is compared to a full-wave simulated 3D model of the proposed dual rectangular cavity filter. A tolerance analysis on the crucial properties of the proposed filter is performed to ensure design robustness against the anticipated fabrication inaccuracies.

Filter architecture

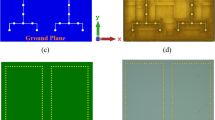

To account for fabrication tolerances, we extend the target 6 GHz operational bandwidth around the system’s center frequency with a guard band of at least 1 GHz, resulting in a bandwidth of minimally 8 GHz centered around 135 GHz. To this end, the envisaged second-order Chebychev filter characteristic is created using coupling matrix theory59,60, represented by a simple filter diagram in Fig. 5. The appurtenant external coupling factors (\(Q_e\)) and coupling matrix (CM) for the designed filter are given in equation (1). The scattering parameters pertaining to this theoretical analysis are plotted by dashed lines in Fig. 6b. The minimal insertion loss is trivial: since this is a lossless theoretical model, it amounts to 0 dB. The 3 dB-bandwidth of the transmission characteristic (|S\(_{12}|\)=|S\(_{21}|\)) equals 10.2 GHz, ranging from 129.8 to 140 GHz. The transmission exhibits a very flat response, which can be observed in the zoomed in part of Fig. 6b. The filter’s reflection coefficient (|S\(_{11}|\)=|S\(_{22}|\)) is matched from 131.7 to 138 GHz, resulting in a fractional bandwidth (FBW) of 4.67%.

Full-wave simulations

Consequently, the theoretical matrices are converted into a physical design, of which the optimized dimensions, based on full-wave simulations in CST, are shown in Fig. 6a. This design takes into account the minimal width of 0.25 mm-wide protrusions imposed by fabrication restrictions. By relying solely on two cavities, the design fits within a footprint of only 5.2 mm \(\times\) 2.2 mm \(\times\) 300 \(\upmu\)m. The iris width between the AFSIW feed and the cavity controls the external coupling factor \(Q_e\), while the iris width between both cavities is responsible for the coupling coefficient \(CM_{ij}\) between both resonators. This design does not suffer from any self-coupling of the cavities (\(CM_{ii}=0\)).

In Fig. 6b, the resulting S-parameters (solid lines) are compared to the curves obtained from the theoretically conceived filter (dashed lines). The full-wave simulation is carried out with a realistic surface roughness of 300 nm. The deviations w.r.t. the coupling matrix theory, represented by some asymmetry found in the full-wave simulation at higher frequencies, is caused by the propagation of modes with orders higher than the fundamental \(TE_{10}\)-mode. The minimal insertion loss amounts to 0.48 dB. The 3 dB-bandwidth of 11.2 GHz for the transmission coefficient, ranging from 129.9 to 141.1 GHz, maintains the flat response predicted by the coupling matrix model. The filter’s reflection coefficient is matched from 131.5 to 138.4 GHz, resulting in a FBW of 5.11%. Employing the current dimensions to calculate the quality factor for a single cavity61, resulting in \(Q_{theory, single} = 975.5\), allows comparison to the full-wave simulated equivalent, being \(Q_{CST, single} = 1393.2\). However, neither the measured surface roughness nor the employed surface finish of the fabricated prototype is taken into account in these calculations, while their importance will be confirmed later in this paper.

Fabrication cornerstone analysis

This analysis investigates three important fabrication imperfections, being (1) the influence of the surface roughness, (2) the variation of several key dimensions of the dual rectangular filter, and (3) the potentially slant sidewall angle of the AFSIW cross-sections. A moderate change in surface roughness on the sidewalls of the AFSIW barely has any consequences, since the fields are contained in the center of the structure. Conversely, a variation on the surface roughness on the top and bottom conductors of the AFSIW results mostly in an elevated insertion loss and a slight shift towards lower frequencies due to the increase in path length. This is indicated in Fig. 7a for a surface roughness of 100 nm, 300 nm (nominal) and 500 nm. Each 200 nm increase in surface roughness causes 0.2 dB additional insertion loss. This shows the importance of smooth copper foils when fabricating the AFSIW components, to keep the overall insertion losses in future communication systems to a bare minimum.

The subsequent key dimensions of the design are tightly related to the operating mechanism of this filter. The cavity dimensions determine the resonant frequencies and, therefore, the passband location. By decreasing the cavity dimensions, the resonances will shift towards higher frequencies, as will the passband. This behavior can be observed from Fig. 7b, where the cavity dimension varies from 2.13 mm, 2.15 mm (nominal) to 2.17 mm. Each joint length and width increase of 20 \(\upmu\)m results in a 1 GHz-decrease in operating frequency, neatly indicating our previously defined guard bands around the operating frequencies.

The coupling matrix coefficients (\(CM_{12}=CM_{21}\)) are directly affected by changing the iris width between both cavities. Increasing the iris width increases the coupling between both cavities, which is confirmed in Fig. 8a. When the cavities are too tightly coupled, the passband is deprived of its flat characteristic, since the resonances shift too far away from each other. This is illustrated for an iris width of 0.84 mm in Fig. 8a (dashed-dotted line). On the other hand, the iris width of 0.8 mm decouples the cavities, bringing the resonances so close together that the passband is greatly reduced (dashed line). Ultimately, an optimum can be found to obtain the desired flatness and operational bandwidth. The external loading factors (Qe) are directly affected by changing the iris widths between the incoming AFSIW feed and the neighboring cavity. Figure 8b shows that an increase of this iris width brings the resonances closer together and lowers the passband very slightly in frequency.

The increase in AFSIW height, as stated previously, improves the Q-factor61. Figure 9a corroborates this improvement by showing lower insertion loss for increasing heights. The last possible fabrication deviation occurs at the sidewalls of the AFSIW. The sidewalls may be slant due to laser beam diffusion when fabricating the AFSIW segments. The resulting effect on the filter characteristic is demonstrated in Fig. 9b, proving robust behavior against minor variations in sidewall angle. A 2\(^\circ\) increase in sidewall angle results in a shift towards lower frequencies by less than 0.2 GHz for both resonances. The simulated slant angles are defined by rotating the sidewalls around their height-center. Therefore, a height of 300 \(\upmu\)m gives rise to a wall location variation of ± 5 \(\upmu\)m per 2\(^\circ\) increase in sidewall angle. In case of a 2\(^\circ\) sidewall angle, the width of the cavity dimension varies in the range 2.15 mm ± 10 \(\mu\)m.

Measurement results

AFSIW routing

The first validation step of the suggested PCB technology platform, presented in Fig. 2, consists of measuring the double transition with two AFSIW lines of different length: 5 cm and 10 cm. These measurements are performed by attaching the Infinity Waveguide Probes (with a GSG pitch of 100 \(\upmu\)m) to the Tx/Rx VDI Extension Modules WR6.5 (110–170 GHz). These range extenders are connected to the Keysight N5247B PNA-X vector network analyzer (VNA), as schematically explained in Fig. 10a, according to the annotations in Fig. 2 to clarify each step. An MPI microscope is employed to validate the positioning of the probes on the GCPW landing pads, as shown in the actual measurement setup in Fig. 10b.

The acquired data are post-processed using the Python scikit-rf package for TRL calibration57. Two separate calibrations are executed up to the port planes marked in Fig. 10a, called CAL1 and CAL2. The measurement deembedded up to CAL2 yields the characteristic of an electromagnetic wave traveling through a purely AFSIW section, while the CAL1 calibration planes include two transitions leading up to the striplines. The CAL1 calibration for the 5 cm-long AFSIW line is plotted in Fig. 11a, comparing our simulation model to the measured result. Good correspondence between both can be observed. The repeatability of the fabrication is validated by measuring three prototypes and further processing is done on the average of the transmission characteristics of all measurements. Comparing both CAL1 and CAL2 data, of which the corresponding curves are plotted in Fig. 11b, shows a 1.1 dB-transition loss from stripline to AFSIW. Figure 11b also demonstrates that the AFSIW interconnect has a measured insertion loss of around 0.08 dB/mm in the D-band and an amplitude variation smaller than 0.01 dB/mm from 115 to 155 GHz.

Table 2 compares the implementation of different routing options in different fabrication technologies. The DFSIW, microstrip line (MSL) or GCPW suffer from a high dielectric loss, which corresponds to an increased loss per unit length. Other AFSIW options, such as CNC milling, 3D printed SLA or SLM and SMW, outperform our proposed solution in terms of insertion loss, owing to lower surface roughness at the conductor–air interface and/or higher waveguides. Nevertheless, they face several challenges associated with MMIC integration11,62. To this end, our proposed solution delivers a cost-efficient, mass-manufacturable alternative that facilitates integration of MMICs. Future research concerning the optimization of the fabrication procedure might decrease the surface roughness further and/or increase the height of the AFSIW section, thereby, decreasing the insertion loss of our proposed solution. While showcasing the importance of the conductor foils with low surface roughness, our results compete with other AFSIW-containing technologies as a cost-efficient, mass-manufacturable alternative that promotes integration of MMICs.

AFSIW filter

To illustrate the technology’s potential for the development of high-performance functional components in the proposed Any-Layer HDI PCB stack, besides routing components, we now characterize the dual rectangular cavity filter, realized in this proof of concept. It consists of the layout represented in Fig. 6a, which is directly connected to the AFSIW-to-stripline transition for measurement purposes. A top view of the fabricated AFSIW filter is shown in Fig. 12a before the third laminate \(\textcircled {3}\) is added, as explained previously. A cross-section of the AFSIW feed is shown in Fig. 12b, indicating a slight inclination of the sidewalls, of which the effect should be negligible, as discussed during the tolerance analysis.

The corresponding S-parameters in Fig. 13a are in good agreement with the simulations. The minimal insertion loss of the measured filter is 0.87 dB. The target operating bandwidth of 6 GHz around 135 GHz is achieved, since the measured 10 dB-match spans from 132.8 to 139.2 GHz, which corresponds to a FBW of 4.74%. The 3 dB-bandwidth covers 10.3 GHz, ranging from 130.6 to 140.9 GHz. In contrast to the aforementioned quality factor calculations, more realistic Q-factors can be obtained based on the scattering characteristics61. In simulation, we obtain a value of \(Q_{sim,filter} = 236\), while the measurements yield a value of \(Q_{meas,filter} = 153\). The decreased measured value is expected, since the higher insertion loss with respect to the simulation is not compensated by the smaller 3 dB-bandwidth61. Figure 13b show the maximal measured group delay of 0.067 ns and its simulated equivalent of 0.084 ns. The filter provides a solicited flat group delay within the passband, competing with literature65,66.

All high-end D-band filters in the state-of-the-art literature are fabricated in AFSIW technology to minimize the routing losses and maximize power throughput. Table 3 compares some high-end filters implemented in DFSIW and AFSIW based on different fabrication procedures to our proposed solution. The LTCC prototype shows an excellent footprint, but has limited FBW and suffers from large transmission losses due to the prominent presence of a dielectric laminate. Comparing the CNC and DMLS prototypes to each other, reveals an increased insertion loss due to the surface roughness in case of DMLS 3D-printing. The SMW filter yields an excellent compromise between the latter two alternatives, further enabling integration of MMICs and parallel mass-manufacturing to suppress the cost. Our proposed PCB filter is compact for an AFSIW implementation, owing to the dual-cavity topology and, therefore, maintains a broadband characteristic and a low insertion loss. The validation of this filter characteristic paves the way to the design of more complex filters, which will be in competition with the current state of the art, as predicted by Table 3.

Conclusion

This paper presents a versatile, mass-producible Any-Layer High Density Interconnect (HDI) printed circuit board (PCB) technology for future joint communication and sensing (JCAS) systems at D-band (110–170 GHz). The addition of a low-loss air-filled substrate-integrated-waveguide (AFSIW) layer, for highly efficient D-band routing and filtering, helps to overcome the current shortcomings of PCB technology by avoiding dielectric losses and minimizing losses due to surface roughness. A dedicated transition from AFSIW to stripline is designed for compact and broadband interfacing to integrated circuits (ICs), accentuating an additional advantage of PCB technology. To this end, several AFSIW components, including an AFSIW-to-stripline transition, are analyzed and their measured characteristics are validated with respect to simulated data. We demonstrate that the measured air-filled routing loss is around 0.08 dB/mm, while ensuring a flat amplitude variation within 0.01 dB/mm over a broad range (115–155 GHz). The manufactured transition towards stripline reveals a loss of only 1.1 dB. The fabricated dual rectangular filter has a minimal insertion loss of 0.87 dB and exhibits 10 dB-matching within the (132.8–139.2 GHz) frequency band, while maintaining a good quality factor of 153 and a group delay not exceeding 0.067 ns. Moreover, the insertion loss can be further improved in future generations by reducing the surface roughness of the conductor layers at the AFSIW boundaries and/or further increasing the AFSIW height. To this end, additional research is to be performed for optimization of the fabrication procedure. The good performance of the measured prototypes showcase the potential of this novel PCB-based technology platform, thereby paving the way for the development of full system front-ends consisting of chip integration, routing, filtering and radiating features, alleviating future obstacles towards the next-generation wireless systems.

Data availibility

The datasets used and analyzed during the current study available from the corresponding author on reasonable request.

References

Fang, X., Feng, W., Chen, Y., Ge, N. & Zhang, Y. Joint communication and sensing toward 6G: Models and potential of using MIMO. IEEE Internet Things J. 10, 4093–4116. https://doi.org/10.1109/JIOT.2022.3227215 (2023).

Wild, T., Braun, V. & Viswanathan, H. Joint design of communication and sensing for beyond 5G and 6G systems. IEEE Access 9, 30845–30857. https://doi.org/10.1109/ACCESS.2021.3059488 (2021).

Schneider, T., Wiatrek, A., Preussler, S., Grigat, M. & Braun, R.-P. Link budget analysis for terahertz fixed wireless links. IEEE Trans. Terahertz Sci. Technol. 2, 250–256. https://doi.org/10.1109/TTHZ.2011.2182118 (2012).

Maiwald, T. et al. A review of integrated systems and components for 6G wireless communication in the D-band. Proc. IEEE 111, 220–256. https://doi.org/10.1109/JPROC.2023.3240127 (2023).

Lamminen, A., Säily, J., Ala-Laurinaho, J., de Cos, J. & Ermolov, V. Patch antenna and antenna array on multilayer high-frequency PCB for D-band. IEEE Open J. Antennas Propag. 1, 396–403. https://doi.org/10.1109/OJAP.2020.3004533 (2020).

Cheng, Y. J., Tan, F. Y., Zhou, M. M. & Fan, Y. Dual-polarized wideband plate array antenna with high polarization isolation and low cross polarization for D-band high-capacity wireless application. IEEE Antennas Wirel. Propag. Lett. 19, 2023–2027. https://doi.org/10.1109/LAWP.2020.3020385 (2020).

Zhou, M. M. & Cheng, Y. J. D-band high-gain circular-polarized plate array antenna. IEEE Trans. Antennas Propag. 66, 1280–1287. https://doi.org/10.1109/TAP.2018.2796299 (2018).

Saleh, W., Letestu, Y., Sauleau, R. & Cruz, E. M. Design and measurements of a high-performance wideband transmitarray antenna for D-band communications. IEEE Antennas Wirel. Propag. Lett. 20, 1765–1769. https://doi.org/10.1109/LAWP.2021.3096743 (2021).

Wu, K., Bozzi, M. & Fonseca, N. J. G. Substrate integrated transmission lines: Review and applications. IEEE J. Microw. 1, 345–363. https://doi.org/10.1109/JMW.2020.3034379 (2021).

Vosoogh, A., Zirath, H. & He, Z. S. Novel air-filled waveguide transmission line based on multilayer thin metal plates. IEEE Trans. Terahertz Sci. Technol. 9, 282–290. https://doi.org/10.1109/TTHZ.2019.2905775 (2019).

Zhang, Y., Zhang, J., Yue, R. & Wang, Y. Loss analysis of thin film microstrip line with low loss at D band. J. Lightw. Technol. 39, 2421–2430. https://doi.org/10.1109/JLT.2021.3052560 (2021).

Campion, J. et al. An ultra low-loss silicon-micromachined waveguide filter for D-band telecommunication applications. In 2018 IEEE/MTT-S International Microwave Symposium-IMS, 583–586. https://doi.org/10.1109/MWSYM.2018.8439601 (IEEE, 2018).

Yang, H. et al. WR-3 waveguide bandpass filters fabricated using high precision CNC machining and SU-8 photoresist technology. IEEE Trans. Terahertz Sci. Technol. 8, 100–107. https://doi.org/10.1109/TTHZ.2017.2775441 (2017).

Chattopadhyay, G., Reck, T., Lee, C. & Jung-Kubiak, C. Micromachined packaging for terahertz systems. Proc. IEEE 105, 1139–1150. https://doi.org/10.1109/JPROC.2016.2644985 (2017).

Virginia Diodes, Inc. VDI waveguide band designations. https://www.vadiodes.com/en/resources/app-notes. Online.

Koller, D., Bryerton, E. W. & Hesler, J. L. WM380 (675–700 GHz) bandpass filters in milled, split-block construction. IEEE Trans. Terahertz Sci. Technol. 8, 630–637. https://doi.org/10.1109/TTHZ.2018.2873114 (2018).

Kerr, A., Litton, C., Petencin, G., Koller, D. & Shannon, M. Loss of gold plated waveguides at 210–280 GHz. ALMA Memo 585, 25 (2009).

Zhang, B. & Zirath, H. Metallic 3-D printed rectangular waveguides for millimeter-wave applications. IEEE Trans. Compon. Packag. Manuf. Technol. 6, 796–804. https://doi.org/10.1109/TCPMT.2016.2550483 (2016).

Chin, S. Y., Dikshit, V., Meera Priyadarshini, B. & Zhang, Y. Powder-based 3D printing for the fabrication of device with micro and mesoscale features. Micromachines 11, 658. https://doi.org/10.3390/mi11070658 (2020).

Nagarajan, B., Hu, Z., Song, X., Zhai, W. & Wei, J. Development of micro selective laser melting: The state of the art and future perspectives. Engineering 5, 702–720. https://doi.org/10.1016/j.eng.2019.07.002 (2019).

Zhang, B., Guo, Y.-X., Zirath, H. & Zhang, Y. P. Investigation on 3-D-printing technologies for millimeter-wave and terahertz applications. Proc. IEEE 105, 723–736. https://doi.org/10.1109/JPROC.2016.2639520 (2017).

Shen, J. et al. Rapid prototyping of low loss 3D printed waveguides for millimeter-wave applications. In 2017 IEEE MTT-S International Microwave Symposium (IMS), 41–44. https://doi.org/10.1109/MWSYM.2017.8058593 (IEEE, 2017).

Lomakin, K., Sippel, M., Helmreich, K. & Gold, G. Design and analysis of 3D printed slotted waveguides for D-band using stereolithography and electroless silver plating. In 2020 IEEE/MTT-S International Microwave Symposium (IMS), 177–180. https://doi.org/10.1109/IMS30576.2020.9223819 (IEEE, 2020).

von Bieren, A., De Rijk, E., Ansermet, J.-P. & Macor, A. Monolithic metal-coated plastic components for mm-wave applications. In 2014 39th International Conference on Infrared, Millimeter, and Terahertz waves (IRMMW-THz), 1–2. https://doi.org/10.1109/IRMMW-THz.2014.6956222 (IEEE, 2014).

Sinanis, M. D., Adhikari, P., Jones, T. R., Abdelfattah, M. & Peroulis, D. High-Q high power tunable filters manufactured with injection molding technology. IEEE Access 10, 19643–19653. https://doi.org/10.1109/ACCESS.2022.3151849 (2022).

Giboz, J., Copponnex, T. & Mélé, P. Microinjection molding of thermoplastic polymers: A review. J. Micromech. Microeng. 17, R96. https://doi.org/10.1088/0960-1317/17/6/R02 (2007).

Sammoura, F. et al. Plastic 95-GHz rectangular waveguides by micro molding technologies. Sens. Actuators A 127, 270–275. https://doi.org/10.1016/j.sna.2005.07.020 (2006).

Farjana, S. et al. Realizing a 140 GHz gap waveguide-based array antenna by low-cost injection molding and micromachining. J. Infrared Millimeter Terahertz Waves 42, 893–914. https://doi.org/10.1007/s10762-021-00812-8 (2021).

Ghalichechian, N. & Sertel, K. Permittivity and loss characterization of SU-8 films for mmW and terahertz applications. IEEE Antennas Wirel. Propag. Lett. 14, 723–726. https://doi.org/10.1109/LAWP.2014.2380813 (2014).

Shang, X., Ke, M., Wang, Y. & Lancaster, M. J. WR-3 band waveguides and filters fabricated using SU8 photoresist micromachining technology. IEEE Trans. Terahertz Sci. Technol. 2, 629–637. https://doi.org/10.1109/TTHZ.2012.2220136 (2012).

Glynn, D. et al. Submillimetre rectangular waveguides based on SU-8 photoresist micromachining technology. In 2016 46th European Microwave Conference (EuMC), 1346–1349. https://doi.org/10.1109/EuMC.2016.7824601 (2016).

Li, Y. Challenges and issues of using polymers as structural materials in MEMS: A review. J. Microelectromech. Syst. 27, 581–598. https://doi.org/10.1109/JMEMS.2018.2837684 (2018).

Campion, J. et al. Toward industrial exploitation of THz frequencies: Integration of SiGe MMICs in silicon-micromachined waveguide systems. IEEE Trans. Terahertz Sci. Technol. 9, 624–636. https://doi.org/10.1109/TTHZ.2019.2943572 (2019).

Beuerle, B., Campion, J., Shah, U. & Oberhammer, J. Low-loss silicon micromachined waveguides above 100 GHz utilising multiple H-plane splits. In 2018 48th European Microwave Conference (EuMC), 1041–1044. https://doi.org/10.23919/EuMC.2018.8541605 (IEEE, 2018).

Reck, T. et al. A silicon micromachined eight-pixel transceiver array for submillimeter-wave radar. IEEE Trans. Terahertz Sci. Technol. 5, 197–206. https://doi.org/10.1109/TTHZ.2015.2397274 (2015).

Leong, K. M. et al. WR15 silicon micromachined waveguide components and active circuit integration methodology. IEEE Trans. Microw. Theory Techn. 60, 998–1005. https://doi.org/10.1109/TMTT.2012.2184296 (2012).

Ermolov, V. et al. Micromachining integration platform for sub-terahertz and terahertz systems. Int. J. Microw. Wirel. Technol. 10, 651–659. https://doi.org/10.1017/S175907871800048X (2018).

Glubokov, O. et al. Investigation of fabrication accuracy and repeatability of high-Q silicon-micromachined narrowband sub-THz waveguide filters. IEEE Trans. Microw. Theory Tech. 67, 3696–3706. https://doi.org/10.1109/TMTT.2019.2926244 (2019).

Tajima, T., Song, H.-J. & Yaita, M. Design and analysis of LTCC-integrated planar microstrip-to-waveguide transition at 300 GHz. IEEE Trans. Microw. Theory Tech. 64, 106–114. https://doi.org/10.1109/TMTT.2015.2504474 (2015).

Bhutani, A., Göttel, B., Lipp, A. & Zwick, T. Packaging solution based on low-temperature cofired ceramic technology for frequencies beyond 100 GHz. IEEE Trans. Components Packag. Manuf. Technol. 9, 945–954. https://doi.org/10.1109/TCPMT.2018.2882062 (2018).

Ihle, M., Ziesche, S., Zech, C. & Baumann, B. Functional printing of MMIC-interconnects on LTCC packages for sub-THz applications. In 2019 22nd European Microelectronics and Packaging Conference and Exhibition (EMPC), 1–4. https://doi.org/10.23919/EMPC44848.2019.8951799 (IEEE, 2019).

Manzillo, F. F., Clemente, A. & González-Jiménez, J. L. High-gain D-band transmitarrays in standard PCB technology for beyond-5G communications. IEEE Trans. Antennas Propag. 68, 587–592. https://doi.org/10.1109/TAP.2019.2938630 (2019).

Peeters, M. et al. (Why do we need) wireless heterogeneous integration (anyway?). 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 256–257. https://doi.org/10.1109/VLSITechnologyandCir46769.2022.9830480 (2022).

de Kok, M., Smolders, A. B. & Johannsen, U. A review of design and integration technologies for D-band antennas. IEEE Open J. Antennas Propag. 2, 746–758. https://doi.org/10.1109/OJAP.2021.3089052 (2021).

Ghiotto, A., Parment, F., Vuong, T.-P. & Wu, K. Millimeter-wave air-filled SIW antipodal linearly tapered slot antenna. IEEE Antennas Wirel. Propag. Lett. 16, 768–771. https://doi.org/10.1109/LAWP.2016.2602280 (2016).

Esteban, H., Belenguer, A., Sánchez, J. R., Bachiller, C. & Boria, V. E. Improved low reflection transition from microstrip line to empty substrate-integrated waveguide. IEEE Microw. Wirel. Compon. Lett. 27, 685–687. https://doi.org/10.1109/LMWC.2017.2724011 (2017).

Van den Brande, Q. et al. A hybrid integration strategy for compact, broadband, and highly efficient millimeter-wave on-chip antennas. IEEE Antennas Wirel. Propag. Lett. 18, 2424–2428. https://doi.org/10.1109/LAWP.2019.2929428 (2019).

Van Messem, L. et al. A 4x4 millimeterwave-frequency butler matrix in grounded co-planar waveguide technology for compact integration with 5G antenna arrays. IEEE Trans. Microw. Theory Tech. 71, 122–134. https://doi.org/10.1109/TMTT.2022.3178073 (2022).

Moerman, A. et al. System-level simulation suite for the design of mmWave-over-fiber-based distributed antenna systems. IEEE Trans. Microw. Theory Tech.https://doi.org/10.1109/TMTT.2023.3267545 (2023).

Sinha, S., Trischler, H., Ocket, I. & Schaffler, E. D-band air-filled substrate integrated waveguide (AFSIW) and broadband stripline to AFSIW launcher embedded in multi-layer PCBs. IEEE Microw. Wirel. Technol. Lett.https://doi.org/10.1109/LMWT.2023.3267769 (2023).

IPC International, Inc. Sectional Design Standard for High Density Interconnect (HDI) Printed Boards. https://www.ipc.org/TOC/IPC-2226A.pdf. Online.

AT &S. HDI Circuit Boards. https://ats.net/en/products/hdi-printed-circuit-boards. Online.

Roodaki-Lavasani-Fard, M. et al. Shared aperture dual-wideband planar antenna arrays using any-layer PCB technology for mm-wave applications. IEEE Trans. Antennas Propag. 70, 1087–1096. https://doi.org/10.1109/TAP.2021.3111313 (2021).

AT &S. Taking printed circuit boards to a whole new level with 2.5D. https://ats.net/en/products/hdi-printed-circuit-boards. Online.

Trischler, H., Sinha, S., Schlaffer, E. & Ocket, I. Towards mass production of air filled substrate integrated waveguides (AFSIW) for ultra-low loss, broadband radar applications. In 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), 937–941. https://doi.org/10.1109/ECTC51906.2022.00152 (2022).

Parment, F., Ghiotto, A., Vuong, T.-P., Duchamp, J.-M. & Wu, K. Air-filled substrate integrated waveguide for low-loss and high power-handling millimeter-wave substrate integrated circuits. IEEE Trans. Microw. Theory Tech. 63, 1228–1238. https://doi.org/10.1109/TMTT.2015.2408593 (2015).

Arsenovic, A. et al. scikit-rf: An open source python package for microwave network creation, analysis, and calibration [Speaker’s Corner]. IEEE Microw. Mag. 23, 98–105. https://doi.org/10.1109/MMM.2021.3117139 (2022).

Farid, A. A., Ahmed, A. S. H., Dhananjay, A. & Rodwell, M. J. W. A fully packaged 135-GHz multiuser MIMO transmitter array tile for wireless communications. IEEE Trans. Microw. Theory Tech. 70, 3396–3405. https://doi.org/10.1109/TMTT.2022.3161972 (2022).

Matthaei, G., Young, L. & Jones, E. Microwave Filters, Impedance-Matching Networks, and Coupling Structures (Artech House, 1980).

Cameron, R. J., Kudsia, C. M. & Mansour, R. R. Microwave Filters for Communication Systems: Fundamentals, Design, and Applications (Wiley, 2018).

Pozar, D. M. Microwave Engineering (Wiley, 2011).

Bertrand, M. et al. Substrate integrated waveguides for mm-wave functionalized silicon interposer. In 2018 IEEE/MTT-S International Microwave Symposium-IMS, 875–878. https://doi.org/10.1109/MWSYM.2018.8439287 (IEEE, 2018).

McGrath, W. R., Walker, C., Yap, M. & Tai, Y.-C. Silicon micromachined waveguides for millimeter-wave and submillimeter-wave frequencies. IEEE Microw. Guided Wave Lett. 3, 61–63. https://doi.org/10.1109/75.205665 (1993).

Khan, W. T., Ulusoy, A. Ç. & Papapolymerou, J. D-band characterization of co-planar wave guide and microstrip transmission lines on liquid crystal polymer. In 2013 IEEE 63rd Electronic Components and Technology Conference, 2304–2309. https://doi.org/10.1109/ECTC.2013.6575905 (IEEE, 2013).

Miek, D., Kamrath, F., Braasch, K., Boe, P. & Höft, M. Quasi-elliptical stub-based multi-resonance waveguide filters with low manufacturing complexity for mm-wave applications. IEEE J. Microw. 3, 70–83. https://doi.org/10.1109/JMW.2022.3225629 (2022).

Vazquez-Roy, J. L., Rajo-Iglesias, E., Ulisse, G. & Krozer, V. Design and realization of a band pass filter at D-band using gap waveguide technology. J. Infrared Millimeter Terahertz Waves 41, 1469–1477. https://doi.org/10.1007/s10762-020-00729-8 (2020).

Yu, Y. et al. D-band waveguide diplexer fabricated using micro laser sintering. IEEE Trans. Compon. Packag. Manuf. Technol. 12, 1446–1457. https://doi.org/10.1109/TCPMT.2022.3204887 (2022).

Zhao, X. et al. Silicon micromachined D-band diplexer using releasable filling structure technique. IEEE Trans. Microw. Theory Tech. 68, 3448–3460. https://doi.org/10.1109/TMTT.2020.3004585 (2020).

Khalil, A. H. et al. Quasi-elliptic and Chebyshev compact LTCC multi-pole filters functioning in the submillimetric wave region at 150 GHz. IEEE Trans. Microw. Theory Tech. 58, 3925–3935. https://doi.org/10.1109/TMTT.2010.2085012 (2010).

Acknowledgements

This work was made possible by AT &S, manufacturer for high-end printed circuit boards. Special thanks to Luc Pauwels and Nele Van Hoovels for providing their expertise during the measurements and to Francesco Filice and Andy Dewilde for the aid during the measurement time. I would like to express my gratitude to Olivier Caytan for proof reading this document.

Author information

Authors and Affiliations

Contributions

L.V.M. designed and measured the filter prototypes, post-processed the data and wrote the manuscript, S.S. conceived the proposed stack-up, set up the fabrication proceeding and extracted data for the loss analysis, H.T., E.S. and D.S. developed and researched the fabrication method, I.O., S.L. and H.R. shared their expertise for analyzing and interpreting the data, helped with the conceptualization of the proposed platform and managed the project. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Van Messem, L., Sinha, S., Ocket, I. et al. Air-filled SIW technology for mass-manufacturable and energy-efficient terahertz systems. Sci Rep 13, 16714 (2023). https://doi.org/10.1038/s41598-023-43887-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-43887-0

- Springer Nature Limited