Abstract

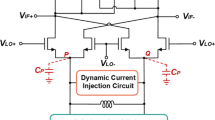

This paper explores the working principles of mixers, which is an integral part of superheterodyne transceiver system. Special emphasis has been led on the design of subharmonic mixers, which is a subclass of the mixer system by using 180-nm CMOS technology. The present paper highlights the design implementation of a 2× subharmonic mixer. From simulation results, it has been observed that the mixer attains 19 dBm IIP3, 12 dB conversion gain, 10 dB noise figure at 2–2.4 GHz RF range and 300–500 MHz of IF range. From 1.8 V supply, total power dissipation has been measured to be 3.8 mW.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Ding Y., Harjani, R.: High-Linearity CMOS Front-End Circuits. Springer, Berlin

Ellinger, F.: Radio Frequency Integrated Circuits and Technologies, 2nd edn. Springer, Berlin

Perumana, B.G., Lee, C.-H., Laskar, J., Charkraborty, S.: A subharmonic CMOS mixer based on threshold voltage modulation. IEEE MTT-S Int. Dig., pp 33–36 (2005)

Upadhyaya, P., Rajashekharaiah, M., Heo, D.: A 5.6 GHz CMOS doubly balanced sub-harmonic mixer for direct conversion zero IF receiver. IEEE Workshop on Microelectronics and Electron Devices Symposium, pp. 129–130 (2004)

Kim, Y., Kim, Y., Lee, S.: Linearized mixer using predistortion technique. IEEE Microw. Wirel. Compon. Lett. 12, 204–205 (2002)

Weng, R.M., Wang, J.C., Li, S.Y., Wei, H.C.: A low power folded mixer using even harmonic technology. IEEE International Workshop Radio-Frequency Integration Technology Symposium, pp. 247–249 (2007)

Jackson, B., Saavedra, C.: A CMOS Ku-band 4x subharmonic mixer. IEEE J. Solid-State Circuits 43(6), 1351–1359 (2008)

Wangl, K., Mal, K., Yel, W., Yeol, K.S., Zhang, B., Wang, Z.: A Low Voltage Low Power Highly Linear CMOS Quadrature Mixer Using Transconductance Cancellation Technique. 978-1-4673-1088-8/12/$31.00 © 2012 IEEE

Jackson, B.R.: Subharmonic Mixers in CMOS Microwave Integrated Circuits, PhD thesis, Department of Electrical & Computer Engineering, Queen’s University, Canada (2009)

Kim, T., Kim, B., Lee, K.: Highly Linear Receiver Front-end Adopting MOSFET Transconductance Linearization by Multiple Gated Transistors. IEEE J. Solid-State Circuits 39, 223–229 (2004)

Chong, W.K., Ramiah, H., Vitee, N., Tan, G.H.: Design of Inductorless, Low Power, High Conversion Gain CMOS Subharmonic Mixer for 2.4 GHz Application. In: IEEE Int. Microwave and RF Conf., pp. 274–277 (2014)

Jen, H.C., Rose, S.C., Meyer, R.G.: A 2.2 GHz sub-harmonic mixer for direct-conversion receivers in 0.13 μm CMOS. IEEE International Solid-State Circuits Symposium Digest of Technical Papers, pp. 1840–1849 (2006)

Acknowledgements

The authors are extremely thankful to SMDP-III(C2SD)(funded by Deity, under Ministry of Communication & IT, Government of India) for providing them with the required laboratory facilities and software to carry on the research works, and they also extend their sincere gratitude toward Integrated Circuit Centre of Electronics and Telecommunication Engineering Department of Jadavpur University for allowing them to use the laboratory.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Dandapat, S., Das, S., Das, M., Chatterjee, S. (2021). Design of a Low-Power Linear Down-Conversion Mixer at 2.45 GHz CMOS 180-nm Technology. In: Das, N.R., Sarkar, S. (eds) Computers and Devices for Communication. CODEC 2019. Lecture Notes in Networks and Systems, vol 147. Springer, Singapore. https://doi.org/10.1007/978-981-15-8366-7_73

Download citation

DOI: https://doi.org/10.1007/978-981-15-8366-7_73

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-8365-0

Online ISBN: 978-981-15-8366-7

eBook Packages: EngineeringEngineering (R0)