Abstract

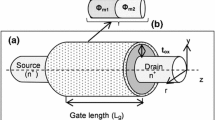

The research focuses on the design and analysis of a Gate Stacked Double Metal Surrounding Gate Nanowire MOSFET (DMSG-NWFET) using In1−xGaxAs as the channel material. The performance of this MOSFET has been evaluated through simulations conducted using the silvaco ATLAS TCAD tool. The study examines the impact of Channel Length (L) and the ratio of L1/L on various DC characteristics, including Drain-Induced-Barrier-Leakage (DIBL), OFF-current (Ioff), ON-current (Ion), Subthreshold Slope (SS), and threshold voltage (Vth). In-depth analysis has been performed by varying the indium portion (1−x) in the In1−xGaxAs channel. Additionally, we investigate the radio frequency (RF) performances by considering the variation of the 'In' fraction and incorporating the cut-off frequency (fT). The investigation demonstrates that the In1−xGaxAs based Gate Stacked Double Metal Surrounding-Gate Nanowire MOSFET exhibits superior DC and RF performance when an optimized fraction of In (Indium). We believe that the proposed device structure holds significant promise for low power VLSI applications.

Similar content being viewed by others

References

Y. Xuan, Y.Q. Wu, P.D. Ye, High-performance inversion-type enhancement-mode InGaAs MOSFET with maximum drain current exceeding 1 A/mm. IEEE Electron Device Lett. 29, 294–296 (2008)

F. Xue, A. Jiang, H. Zhao et al., Sub-50-nm $\hbox In _ {0.7}\hbox Ga _ {0.3}\hbox As $ mosfets with various barrier layer materials. IEEE Electron Device Lett. 33, 32–34 (2011)

S. Sharma, A. Goel, S. Rewari, R.S. Gupta, Gate-stack dual metal (DM) nanowire FET with enhanced analog performance for high frequency applications. In: 2021 Devices for Integrated Circuit (DevIC). IEEE, pp 373–377 (2021)

A. Lubow, S. Ismail-Beigi, T.P. Ma, Comparison of drive currents in metal-oxide-semiconductor field-effect transistors made of Si, Ge, GaAs, InGaAs, and InAs channels. Appl. Phys. Lett. 96, 122105 (2010)

G.A. Neeraj, S. Sharma et al., SiC-based analytical model for gate-stack dual metal nanowire FET with enhanced analog performance. Int. J. Numer. Model. Electron. Networks Devices Fields 35, e2986 (2022)

L. Morassi, G. Verzellesi, H. Zhao et al., Errors limiting split-$ CV $ mobility extraction accuracy in buried-channel InGaAs MOSFETs. IEEE Trans. Electron Devices 59, 1068–1075 (2012)

S. Tewari, A. Biswas, A. Mallik, Study of InGaAs-channel MOSFETs for analog/mixed-signal system-on-chip applications. IEEE Electron Device Lett. 33, 372–374 (2012)

S. Gupta, N. Pandey, R.S. Gupta, Modeling of dual-metal junctionless accumulation-mode cylindrical surrounding gate (DM-JAM-CSG) MOSFET for cryogenic temperature applications. Microelectron. J. 139, 105880 (2023)

P.H. Woerlee, M.J. Knitel, R. Van Langevelde et al., RF-CMOS performance trends. IEEE Trans. Electron Devices 48, 1776–1782 (2001)

S.K. Sharma, B. Raj, M. Khosla, Enhanced photosensitivity of highly spectrum selective cylindrical gate I n 1–x G ax A s nanowire MOSFET photodetector. Mod. Phys. Lett. B 33, 1950144 (2019)

S.K. Sharma, A. Jain, B. Raj, Analysis of triple metal surrounding gate (TM-SG) III–V nanowire MOSFET for photosensing application. Opto-Electron. Rev. 26, 141–148 (2018)

N. Mohankumar, B. Syamal, C.K. Sarkar, Influence of channel and gate engineering on the analog and RF performance of DG MOSFETs. IEEE Trans. Electron Devices 57, 820–826 (2010)

Y. Sun, E.W. Kiewra, J.P. de Souza et al., High-Performance $\hbox In _ {0.7}\hbox Ga _ {0.3}\hbox As $-Channel MOSFETs With High-$\kappa $ Gate Dielectrics and $\alpha $-Si Passivation. IEEE Electron Device Lett. 30, 5–7 (2008)

H.-C. Chin, X. Liu, X. Gong, Y.-C. Yeo, Silane and Ammonia Surface Passivation Technology for High-Mobility $\hbox In _ {0.53}\hbox Ga _ {0.47}\hbox As $ MOSFETs. IEEE Trans. Electron Devices 57, 973–979 (2010)

S.K. Sharma, B. Raj, M. Khosla, Subthreshold performance of In 1–x Ga x As based dual metal with gate stack cylindrical/surrounding gate nanowire MOSFET for low power analog applications. J. Nanoelectron. Optoelectron. 12, 171–176 (2017)

S. Takagi, S.-H. Kim, M. Yokoyama et al., High mobility CMOS technologies using III–V/Ge channels on Si platform. Solid State Electron. 88, 2–8 (2013)

P. Kiran Kumar, B. Balaji, M. Suman, et al., A detailed roadmap from conventional‐MOSFET to nanowire‐MOSFET. Mach. Learn VLSI Chip. Des. 65–93 (2023)

M.S. Narula, A. Pandey, Dual-gate silicon nanowire FET with a corner spacer for high-performance and high-frequency applications. J. Electron. Mater. 1–11 (2023)

L. Liu, V. Saripalli, E. Hwang et al., Multi-gate modulation doped InGa0.3 as quantum well FET for ultra low power digital logic. ECS Trans. 35, 311 (2011)

K. Tomioka, M. Yoshimura, T. Fukui, Vertical In 0.7 Ga 0.3 As nanowire surrounding-gate transistors with high-k gate dielectric on Si substrate. In: 2011 International Electron Devices Meeting. IEEE, p 33 (2011)

S.K. Sharma, B. Raj, M. Khosla, A Gaussian approach for analytical subthreshold current model of cylindrical nanowire FET with quantum mechanical effects. Microelectron. J. 53, 65–72 (2016)

P. Kumar, B. Raj, Parametric investigation and design of junctionless nanowire tunnel field effect transistor. Silicon 1–7 (2021)

K.P. Pradhan, S.K. Mohapatra, P.K. Sahu, D.K. Behera, Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-MOSFET. Microelectron. J. 45, 144–151 (2014)

S.P. Kumar, A. Agrawal, R. Chaujar et al., Device linearity and intermodulation distortion comparison of dual material gate and conventional AlGaN/GaN high electron mobility transistor. Microelectron. Reliab. 51, 587–596 (2011)

P. Chaturvedi, M.J. Kumar, Impact of gate leakage considerations in tunnel field effect transistor design. Jpn. J. Appl. Phys. 53, 74201 (2014)

A. Mallik, A. Chattopadhyay, Tunnel field-effect transistors for analog/mixed-signal system-on-chip applications. IEEE Trans. Electron Devices 59, 888–894 (2012)

W. Shockley, W.T. Read Jr., Statistics of the recombinations of holes and electrons. Phys. Rev. 87, 835 (1952)

A. Chaudhry, J.N. Roy, MOSFET models, quantum mechanical effects and modeling approaches: a review. JSTS J. Semicond. Technol. Sci. 10, 20–27 (2010)

B. Raj, A.K. Saxena, S. Dasgupta, Quantum mechanical analytical modeling of nanoscale DG FinFET: evaluation of potential, threshold voltage and source/drain resistance. Mater. Sci. Semicond. Process. 16, 1131–1137 (2013)

B. Raj, A.K. Saxena, S. Dasgupta, Analytical modeling for the estimation of leakage current and subthreshold swing factor of nanoscale double gate FinFET device. Microelectron. Int. (2009)

A. Jain, S.K. Sharma, B. Raj, Design and analysis of high sensitivity photosensor using cylindrical surrounding gate MOSFET for low power applications. Eng. Sci. Technol. Int. J. 19, 1864–1870 (2016)

B. Jena, K.P. Pradhan, P.K. Sahu et al., Investigation on cylindrical gate all around (GAA) to nanowire MOSFET for circuit application. Facta Univ. Ser. Electron Energ 28, 637–643 (2015)

E.G. Marin, F.G. Ruiz, V. Schmidt et al., Analytic drain current model for III–V cylindrical nanowire transistors. J. Appl. Phys. 118, 44502 (2015)

M.J. Kumar, S. Janardhanan, Doping-less tunnel field effect transistor: Design and investigation. IEEE Trans. Electron Devices 60, 3285–3290 (2013)

D. Chattopadhyay, S.K. Sutradhar, B.R. Nag, Electron transport in direct-gap III–V ternary alloys. J. Phys. C Solid State Phys. 14, 891 (1981)

S. Adachi, Physical properties of III–V semiconductor compounds (Wiley, 1992)

Funding

The authors declare that they have no funding available for the publication chargers of open access. Our institute is not providing any financial support for publications.

Author information

Authors and Affiliations

Contributions

We has been proposed In1−xGaxAs based gate stacked double metal surrounding gate nanowire MOSFET, which are immune to short channel effects and preferred for low power VLSI applications in nano regime.

Corresponding author

Ethics declarations

Conflict of interest

Authors declare that there is no conflict of Interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kumar, P., Sharma, S.K. & Raj, B. Analysis of Device Parameter Variations in In1−xGaxAs Based Gate Stacked Double Metal Surrounding Gate Nanowire MOSFET. Trans. Electr. Electron. Mater. 24, 570–578 (2023). https://doi.org/10.1007/s42341-023-00478-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42341-023-00478-0