Abstract

Aiming to integrate the respective merits of the switched-capacitor converter and the quasi-Z-source converter. An novel high step-up quasi-Z-source DC–DC converter with a single switched-capacitor branch is proposed. Compared to other high boost DC–DC converters, the proposed converter can provide higher output voltage gain, lower current stress across the switches, and lower voltage stress across the output diodes by using the same or similar passive and active components. Therefore, the efficiency and reliability of the converter can be improved. The topological derivation, operating principle, parameter selection, and comparison with other DC–DC converters are presented. Finally, both simulations and experimental results are given to verify the characteristics of the proposed converter.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

With the advance of modern industrial applications and the massive exploitation of conventional fossil energy, environmental pollution and energy shortages are becoming more and more serious. Therefore, it is necessary to develop new energy resources such as solar energy, and wind energy, which are renewable and environmental protection, to replace the traditional fossil energy [1, 2]. However, the output voltage of renewable energy sources tends to be low, and far from the desired dc-link voltage level of grid-connected inverters. Thus, there is more and more demand for high step-up DC–DC converters, and lots of research has been carried out on this topic. Many other industrial applications, such as TV-CRTs, X-ray systems, auxiliary power supplies for electrical vehicles, high-intensity discharge (HID) lamps for automobiles, also require dc/dc converters with high step-up voltage conversion ratio [3, 4].

Among the non-isolated DC–DC converter topologies, the traditional boost converter is one of the most commonly used topologies for voltage step-up. Theoretically speaking, its output voltage will be much higher than the input voltage when the duty ratio approaches 1. However, the duty ratio is limited when considering the parasitic parameters of each component. Therefore, in practical applications, the output voltage gain of the conventional boost converter is limited, which often cannot meet the requirements [5,6,7].

To obtain a higher voltage gain, conventional boost converters can be connected in series [8]. However, the whole system will become complicated due to many components and additional control units, which will increase its cost and size, degrade its efficiency and reliability. In addition to cascading, the voltage gain of the non-isolated DC–DC converters can be increased effectively by using coupled inductors with an appropriate turn ratio instead of traditional inductors [9, 10].However, the energy stored in the leakage inductance is another problem, which needs to be solved by additional snubber circuits, leading to high volume, high weight and low efficiency.

A converter adopting interleaved configuration has been presented in [11], which can be used to reduce the voltage and current stress and obtain a high voltage gain. In [12] and [13], some high step-up DC–DC converters with voltage multiplier cells have been presented. Moreover, using switched-inductors to replace traditional inductors, some non-isolated high step-up converters have been proposed in [14,15,16]. Similarly, as presented in [17,18,19,20,21,22], switched capacitor techniques can also be utilized in DC–DCconverter topologies to achieve high voltage gain.

However, the above DC–DC converters are all very complex, and the output voltage gain is still not high enough for many practical applications. Therefore, in 2003, the simple, novel and efficient idea of a Z-source network was firstly proposed by [23]. The Z-source impedance network consists of two inductors and two capacitors, connected in an X-shape. The Z-source network was firstly applied in DC–AC inverters, i.e., the traditional Z-source inverter (ZSI) [23], which gives the inverter both buck and boost conversion ability in a single-stage topology. Since then, the Z-source network has greatly advanced due to its distinct advantages, e.g., it utilizes the shoot-through zero state to realize high voltage gain, no dead time is needed, and it avoid misgating-on caused by the electromagnetic interference (EMI). Therefore, the Z-source inverter is suitable for renewable power generation systems, such as, fuel cells and photovoltaic (PV) applications. Based on the Z-source network, many publications have been reported to develop the performance of ZSI, e.g., the improved ZSI in [24] and the quasi-Z-source inverter (qZSI) in [25,26,27,28,29].

Especially, the quasi-Z-source inverter, not only retains the main characteristics of the ZSI, but also has its own new features, such as continuous input current, low capacitor voltage stress and a common ground for the input and output. The Z-source network and the quasi-Z-source network can also be applied to boost the output voltage gain of DC–DC converters. In [30], a PWM Z-source DC–DC converter is proposed, and its output voltage gain is higher than the traditional boost converter. In [31], a novel Z-source DC–DC converter is presented, which uses the Z-source network to replace the traditional inductor in a conventional boost converter. In [32], based on the quasi-Z-source network, a modified Z-source DC–DC converter is proposed, which provides a higher voltage gain than the converter in [30]. However, the output voltage-gains of these Z-source DC–DC converters are still not large enough for many industrial applications, so it remains a challenge to design higher step-up DC–DC converters.

In this paper, a novel high step-up quasi-Z-source DC–DC converter with a single switched-capacitor branch is proposed and thus named a switched-capacitor quasi-Z -source converter (SC-qZSC). When the switch is turned off, the energy transferred from the inductors is used to charge the capacitors in parallel. When switch is on, the switched capacitors are connected in series to supply the load. Therefore, the converter can provide higher output voltage gain.

The rest of the paper is organized as follows. Section 2 describes the derivation and configuration of the proposed converter. The operating principle and parameter selection are presented in Section 3 and Section 4, respectively. Section 4 also presents the boundary condition between continuous conduction mode (CCM) and discontinuous conduction mode (DCM), and the load ranges of the proposed converter under the CCM condition. It is followed by the comparison with other DC–DC converters in Section 5. In Section 6 and Section 7, the simulation and experimental results are presented respectively to verify the theoretical analysis. Finally, a conclusion is drawn in Section 8.

2 Configuration of the proposed converter

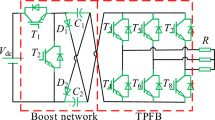

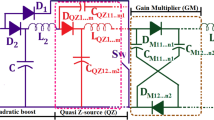

Based on the switched-capacitor converter in Fig. 1 [17], and the quasi-Z-source converter in Fig. 2 [32], the proposed converter is depicted in Fig. 3. The basic idea of the proposed converter is using an additional single switched capacitor branch (C 2, D 2) combined with another single switched-capacitor branch (C 1, D 1) which is hidden in the quasi-Z-source network to form a switched-capacitor cell(C 1, C 2, D 1, D 2).As shown in Fig. 3, the quasi-Z-source network consists of inductors L 1, L 2, capacitors C 1, C 3, and diode D 1.By combining the switched-capacitor cell with the quasi-Z-source network, the proposed converter can reach a higher output voltage gain. According to the position of the additional switched-capacitor branch (C 2, D 2), two kinds of SC-qZSC can be constructed, as shown in Fig. 3(a) and Fig. 3b.

3 Operating principle of proposed converter

For simplicity, the steady state analysis of the proposed converter is based on the following assumptions.

-

1)

The power switch S (MOSFET), diodes, load resistors, inductors and capacitors are all ideal, and the parasitic effect is ignored.

-

2)

L 1=L 2=L and C 1=C 3=C in the quasi-Z-source network, and C 1=C 2=C in the switched-capacitor cell, thus C 1=C 2=C 3=C.

Referring to Fig. 3a, when the converter is operating in CCM, there will exist two operation modes, and the corresponding equivalent circuits are shown in Fig. 4. When switch S is on, as shown in Fig. 4a, diodes D 1 and D 2 are off due to the reverse parallel connection with capacitors. The input voltage V i and C 3 charge L 1, and V i and C 1 charge L 2. Meanwhile, C 1 and C 2 are in series with V i to supply the load through S. By applying Kirchoff voltage law, the following steady-state equations can be derived: v L1=V i +V C3, v L2=V i +V C1, and v o =V i +V C1+V C2. When S is turned off, as shown in Fig. 4b, D 1 and D 2 are on, D o is reverse blocking, inductor L 1 charges C 1, L 2 charges C 3, V i and L 1 are in series with L 2 to charge C 2, and the load R L is powered by capacitor C o . Thus, similar relationships can be obtained: v L1+V C1=0, v L2+V C3=0, and V i =v L1−V C3+V C2. By the volt-second balance principle of the inductor, the average voltage across an inductor is zero in the steady state. Defining the duty cycle of S as D=T on /T s , where T on is the conduction time of switch S, T s is the corresponding switching period. Thus, we have:

From (1) and (2), the output voltage V o can be derived as:

Thus, the output voltage gain G of the proposed SC-qZSC Type-1 converter can be obtained as:

Similarly, for the converter in Fig. 3b, when S is turned on, diodes D 1 and D 2 are off, V i and C 3 charge L 1, and V i and C 1 charge L 2. Meanwhile, C 1 and C 2 are in series with V i and C 3 to supply the load through S. By applying Kirchoff voltage law, one can obtain the following equations: v L1=V i +V C3, v L2=V i +V C1, and v o =V i +V C1+V C2+V C3. When S is turned off, D 1 and D 2 are on, diode D o is reverse blocking, the inductor L 1charges C 1 and C 2 in parallel, L 2 charges C 3, and the load is powered by capacitor C o . Thus, v L1+V C1=0, v L1+V C2=0, and v L2+V C3=0. By the volt-second balance principle of inductors L 1 and L 2, one can obtain:

Therefore, the output voltage gain G’ of SC-qZSC Type-2 can be derived as:

Comparing the output voltage gain (4) with (7), it can be found that the output voltage gain of SC-qZSC Type-1 is higher than that of SC-qZSC Type-2. That is, G=G’+1. Therefore, we will take the SC-qZSC Type-1 as the example to present a detailed analysis in the rest of the paper.

4 Parameter selection

Based on the operating principle analysis in Section 3, parameter selection for SC-qZSC Type-1 will be discussed in this section. Normally, parameterselectionof passive and active components in a converter mainly depends on their rated voltages and rated currents. Hence, the voltage and current stresses of each component will be deduced first.

4.1 Voltage stress of each component

According to the operating principle analysis in Section 3, when switch S is on, diodes D 1 and D 2are off. From Fig. 4a, the voltage stresses of D 1 and D 2 can be obtained as:

When S is off, diodes D 1 and D 2 are on, and D o is off. From Fig. 4b, the voltage stresses of S and D o can be obtained as:

The output voltage V o and capacitor voltage stresses have been derived in Section 3.

4.2 Current stress of each component

Based on the ampere-second balance property of capacitor C, the average current through a capacitor in steady state is zero, and applying Kirchoff current law to capacitors C 1, C 2, C 3 and C o in Fig. 4a and b, we have:

where i L_on , i L_off and i in_on , i in_off are the inductor currents and the input currents when S is on and off, respectively. Assuming that the inductors are large enough, and the inductor currents in each operating mode change linearly, the average inductor current can be expressed as:

Combining (11) with (10), we can obtain:

When switch S is turned on, the currents through S and the output diode D o are:

When S is turned off, the currents through diodes D 1, D 2 are:

Therefore, the average current flow through switch S and the diodes over a switching period can be derived as:

4.3 Parameter selection of inductors

1) Inductors L 1 and L 2: When switch S is off, the inductance of L 1 and L 2, can be derived based on following differential equation:

where di L is the inductor current rippleduring the OFF state, and dt=(1-D)T s is the duration of the OFF state. Generally, a larger inductor current ripple will cause a larger current stress in the switch and diodes. Thus, the inductor current ripple should be limited to a permitted range. For a given permitted fluctuation range x L % of the inductor current, di L can be expressed as:

Then, from Fig. 4b, (16) and (17), we have:

Substituting (1) and (12) into (18), the inductance L 1 and L 2 should satisfy the following equations:

It can be observed that for a given load resistance RLand the duty ratio D, the inductance of L 1 and L 2will be determined by (19) directly.

2) Boundary condition between CCM and DCM: In order to ensure the proposed converter operates in continuous conduction mode, the inductor currents (i L1, i L2) should be maintained continuously during a whole switching cycle, thus:

Substituting (12) and (17) into (20), then we have:

Because the Z-source network is symmetric, L 1=L 2=L. Therefore, from (21), the boundary condition between CCM and DCM can be expressed as:

Denote K=2L/R L T s , and then, Fig. 5 shows a plot of the critical ratio K as a function of duty ratio D at the CCM and DCM boundary.

From (22), we can obtain:

which is the limited load condition for the converter operating in CCM. The load R L is proportional to the inductance L in (23). Thus, by increasing the inductance L, the load capacity of the converter can be further enhanced. Based on (23), when the duty ratio D is equal to 0.204, the maximum load resistance R Lmax can be derived as (24) for CCM operation.

Therefore, the proposed converter will operate in continuous conduction mode regardless of the duty ratio D as long as the load R L satisfies R L ≤R Lmax.

Moreover, a comparison of the CCM load range has been made between the proposed converter and the conventional Z-source DC–DC converter in [30], as shown in Fig. 6, for which the switching frequency f s is set to 50kHz . It can be seen that the load range of the proposed SC-qZSC Type-1 converter is much wider than that of the conventional Z-source DC–DCconverter with the same inductance.

4.4 Parameter selection of capacitors

1) Capacitors C 1, C 2 and C 3: From the above analysis, when switch S is on, the capacitor voltages V C1 and V C2 are in series with the input voltage V i to power the load R L . However, because the sum of V C1, V C2 and V i is a little higher than the output voltage V o , there will exist a small voltage ripple ΔV C on the capacitors at the switching frequency. In order to limit ΔV C to a small range, a permitted fluctuation range x C % of capacitor voltage V C is introduced here.

During the ON state of switch S, capacitors can be designed based on the following differential equation:

where I C_on is the capacitor current when S is on; dt=DT s is the ON time of S, and dv C =x C %V C . Now I C1_on = I in_on −I L1, I C2_on = I L1+I L2−I in_on , and I C3_on = −I L1, so substituting these three equations into (25) leads to:

Therefore, the capacitance of C 1, C 2 and C 3 can be designed by (26) directly.

2) Output filter capacitor C o : Similarly, when S is off, the output diode (D o ) will be reverse blocking. Therefore, the current flow through capacitor C o will be equal to the output current I o . Thus:

where dt=(1 − D)T s . Substituting (3) into (27), the capacitance of capacitor C o can be obtained as:

4.5 Parameter selection of switching devices

Generally, the parameters of diodes and MOFETs can be selected according to their voltage and current stresses, which have been summarized in Table 1.

5 Comparison with other DC–DC converters

5.1 Comparison of output voltage gains

The output voltage gain of the proposed SC-qZSC Type-1 is plotted in Fig.7as a function of the duty ratio D, and compared with the3-Z-network boost converter in [6], the symmetrical hybrid switched-inductor converter (SH-SLC) in [16], the converter in [19] (the turns ratio of the coupled inductor is set to 1), the high step-up converter with double inductor energy storage cell based switched-capacitors (DIESC-SC converter) in [20], and the conventional ZSC in [30] (Table 2).

The ideal expressions for the output voltage gains are given in Table 3. And all these five converters are non-isolated DC–DC topologies. From Fig. 7, it can be observed that the output voltage gain of the proposed SC-qZSC Type-1 converter is higher than that of the other four converters for all duty ratios in the range (0, 0.5).

5.2 Comparison of the number of components

Table 2 shows the comparison of the number of passive and active components used in these five converters. From this table, it can be seen that the total number of components used in the proposed converter is no more than in the other four DC–DC converters. Therefore, compared with these four topologies, the proposed converter can provide higher output voltage gain by using the same or similar active and passive components.

5.3 Comparison of stresses

In this section, the voltage and current stresses of these five converters are compared under the same DC input voltage V i , input current I in , and output voltage gain G. The stresses on components of these five DC–DC topologies have been summarized and tabulated in Table 3.

The comparison of the output diode voltage stress for these five converters is depicted in Fig. 8a.It can be seen, for producing the same output voltage gain G, the proposed converter has lower output diode voltage stress than the SH-SLC converter and the 3-Z boost converter. Although it is a little higher than the DIESC-SC converter and converter in [19], it requires one less inductor and one less capacitor than DIESC-SC converter and one less diode than the converter in [19]. Figure 8b shows the comparison of the switching voltage stress for these five topologies. It can be seen that the proposed converter has lower switching voltage stress than the 3-Z boost converter. However, when the output voltage gain G is larger than 5, it will be a little higher than the SH-SLC converter and the DIESC-SC converter. This is due to the proposed converter has higher boost ability. Fig. 8c shows the comparison of the switching current stress. It can be observed that the proposed converter only has a slightly higher switching current stress than DIESC-SC converter when G is larger than 5, but lower than the other three DC–DC converters.

6 Simulation results

The simulation parameters are selected according to the design conditions developed in Section 4: V i = 10 V, C 1 = C 2 = C 3 = 330 μF, L 1 = L 2 = 220 μH, output filter capacitor C o = 330 μF, switching frequency f s = 30 kHz, rated output power P out = 64 W and R L = 100 Ω.

The simulation results are shown in Fig. 9. The three graphs each show, from top to bottom, the simulated waveforms for the drain-source voltage of switch S, the voltage of diode D 1 (or D 2), the currents in L 1 and L 2, the voltages of C 1 (or C 3) and C 2, and the output voltage V o .

As shown in Fig. 9, the converter operates in CCM and includes two operating states. When the duty ratio is equal to 0.2, the capacitor voltages V C1 (or V C3) is about 3.3 V and V C2 is about 16.67 V, and the output voltage V o is about 30 V. When the duty ratio is 0.3, the capacitor voltageV C1 (or V C3) is 7.5 V, V C2 is 25 V, and the output voltages is 42.5 V. When the duty ratio is 0.4, the capacitor voltage V C1 (or V C3) is 20 V, V C2 are 50 V, and the output voltage is 80 V. Theseare all in accordance with the theoretical values calculated from (1), (2), and (3).

7 Experimental results

A prototype of the proposed SC-qZSC Type-1 converter was built to verify the steady state analysis in Section 3. The experimental parameters were chosen to match the simulation parameters given in Section 6.

The semiconductor switch S (Type:IRFP250N) is driven by the 2BB0108T basic board with driver 2SC0108T, and three MBRF30H150CTdiodes are used for D 1, D 2 and D o . The ON resistance r DS of switch S is 0.075 Ω.

The experimental waveforms of the proposed converter with a regulated DC input voltage source V i =10 V, are shown in Fig. 10. From the top to the bottom, in each graph, the waveforms are the driven voltage of switch S, v GS ; the current of inductor L 1, i L1; the current of inductor L 2, i L2; the capacitor voltages V C1 (or V C3) and V C2; and the output voltage V o .

As shown in Fig. 10a, when the duty ratio D = 0.2, the measured values of capacitor voltages and output voltage are V C1 = V C3 = 2.3 V, V C2 = 15.5 V, and V o =27.2 V, while the theoretical values are V C1 = V C3 = 3.3 V, V C2 = 16.67 V, and V o = 30 V. As shown in Fig. 10(b), when the duty ratio D = 0.3, the measured values of capacitor voltages and the output voltage are V C1=V C3 = 5.2 V, V C2 = 22.8 V, and V o = 38.1 V, while the expected values are V C1 = V C3 = 7.5 V, V C2 = 25 V, and V o = 42.5 V. Fig. 10c shows the experimental waveforms when D=0.4, the measured values of capacitor voltages and the output voltage are V C1 = V C3 = 16.8 V, V C2 = 45.1 V, and V o = 70.3 V, while the theoretical values are V C1 = V C3 = 20 V, V C2 = 50 V, and V o = 80 V. The comparison between theoretical values and measured values is given in Fig. 11. It shows there are some differences between the measured values and theoretical values, which are mainly caused by the equivalent series resistance (ESR) of each component and the forward voltage drop of diodes.

In order to take the parasitic parameters of passive and active components into consideration, we assume that the forward voltage drops on diodes are V D , the parasitic resistances of the inductors are r L , the equivalent series resistances (ESRs) of capacitors are r C , and the equivalent drain-to-source on-resistance of switch S is r DS . Therefore, the relationship between the efficiency and the duty ratio of the proposed converter can be derived as:

where Q = (1 − D + D 2)2 + (2D − D 2)2 + (2 − 2D + D 2)(1 − 2D)2, t r is the turn-on delay time, and t f is the turn-off delay time. The detailed derivation of (29) is given in the Appendix.

The efficiency of the proposed converter under the condition of V i =10 V, duty ratio D=0.2~0.4, R L =100 Ω was measured, and a comparison between the measured and the theoretical predicted efficiencies is presented in Fig. 12. It can be seen that by increasing the value of the duty cycle the measured efficiency of the proposed converter is reduced, and the difference between the calculated and experimental results is increased. The reason is that by increasing the duty cycle the conduction power losses on devices will be increased, too. This fact applies to all kinds of converters based on impedance source network.

8 Conclusion

Based on the respective merits of the switched -capacitor converter and the quasi-Z-source converter, anew high step-up quasi-Z-source DC–DC converter with a single switched-capacitor branch was proposed in this paper. The operating principle analysis, parameter selection, the boundary condition between continuous and discontinuous conduction mode (CCM and DCM), and the comparison with other existed high step-up DC–DC converters have been presented in detail. Finally, both the simulations and experimental results are given to validate the effectiveness of the proposed converter. In comparison with other existed high step-up DC–DC converters, the proposed converter provides higher output voltage gain, lower voltage stress across the output diodes, and lower current stress across the switches. Thus, the efficiency and reliability of the proposed converter can be improved, which implies that it would be suitable for high step-up voltage conversion applications, such as TV-CRTs, X-ray systems, high intensity discharge lamps for automobile headlamps, as well as grid connection of renewable energy sources.

This work was supported by the Key Program of National Natural Science Foundation of China (No. 51437005).

References

Li WH, He XN (2011) Review of nonisolated high step-up DC/DC converters in photovoltaic grid-connected applications. IEEE Trans Ind Electron 58(4):1239–1250

Shahin A, Hinaje M, Martin JP et al (2010) High voltage ratio DC–DC converter for fuel-cell applications. IEEE Trans Ind Electron 57(12):3944–3955

Rosas-Caro JC, Ramirez JM, Peng FZ et al (2010) A DC–DC multilevel boost converter. IET Power Electron 3(1):129–137

Ioinovici A (2013) Power electronics and energy conversion systems. Wiley, Hoboken

Hua CC, Chiang HC, Chuang CW (2014) New boost converter based on Sheppard–Taylor topology. IET Power Electron 7(1):167–176

Zhang GD, Zhang B, Li Z et al (2015) A 3-Z-network boost converter. IEEE Trans Ind Electron 62(1):278–288

Zhao Q, Lee FC (2003) High-efficiency, high step-up DC–DC converters. IEEE Trans Power Electron 18(1):65–73

Walker GR, Sernia PC (2004) Cascaded DC-DC converter connection of photovoltaic modules. IEEE Trans Power Electron 19(4):1130–1139

Hsieh YP, Chen JF, Liang TJ et al (2012) Analysis and implementation of a novel single-switch high step-up DC–DC converter. IET Power Electron 5(1):11–21

Wu TF, Lai YS, Hung JC et al (2008) Boost converter with coupled inductors and buck-boost type of active clamp. IEEE Trans Ind Electron 55(1):154–162

Henn GAL, Silva RNAL, Praca PP et al (2010) Interleaved-boost converter with high voltage gain. IEEE Trans Power Electron 25(11):2753–2761

Prudente JM, Pfitscher LL, Emmendoerfer G et al (2008) Voltage multiplier cells applied to non-isolated DC–DC converters. IEEE Trans Power Electron 23(2):871–887

Tseng KC, Huang CC (2014) High step-up high-efficiency interleaved converter with voltage multiplier module for renewable energy system. IEEE Trans Ind Electron 61(3):1311–1319

Axelrod B, Berkovich Y, Ioinovici A (2008) Switched -capacitor/switched-inductor structures for getting transformerless hybrid DC–DC PWM converters. IEEE Trans Circuits Syst I 55(2):687–696

Berkovich Y, Axelrod B (2011) Switched-coupled inductor cell for DC–DC converters with large conversion ratio. IET Power Electron 4(3):309–315

Tang Y, Fu DJ, Wang T et al (2015) Hybrid switched-inductor converters for high step-up conversion. IEEE Trans Ind Electron 62(3):1480–1490

Ismail EH, Al-Saffar MA, Sabzali AJ et al (2008) A familyof single-switch PWM converters with high step-up conversion ratio. IEEE Trans Circuits Syst I 55(4):1159–1171

Luo FL, Ye H (2004) Positive output multiple-lift push-pull switched-capacitor Luo-converters. IEEE Trans Ind Electron 51(3):594–602

Liang TJ, Chen SM, Yang LS et al (2012) Ultra-large gain step-up switched-capacitor DC–DC converter with coupled inductor for alternative sources of energy. IEEE Trans Circuits Syst I 59(4):864–874

Wu G, Ruan XB, Ye ZH (2015) Nonisolated high step-up DC-DC converters adopting switched-capacitor cell. IEEE Trans Ind Electron 61(1):383–393

Tang Y, Wang T, He YH (2014) A switched-capacitor based active-network converter for high step-up conversion. IEEE Trans Power Electron 29(6):2959–2968

Tang Y, Wang T, Fu DJ (2015) Multicell switched inductor /switched capacitor combined active network converters. IEEE Trans Power Electron 30(4):2063–2072

Peng FZ (2003) Z-source inverter. IEEE Trans Ind Appl 39(2):504–510

Tang Y, Xie SJ, Zhang CH et al (2009) Improved Z-source inverter with reduced Z-source capacitor voltage stress and soft-start capability. IEEE Trans Power Electron 24(2):409–415

Anderson J, Peng FZ (2008) Four quasi-Z-source inverters. In:Proceediings of IEEE power electronics specialists conference, Rhodes, Greece, 15–19 June 2008, 7pp

Cao D, Peng FZ (2009) A family of Z-source and quasi-Z-source DC–DC converters. In:Proceediings of 24th annual IEEE applied power electronics conference and exposition, Washington, DC, USA, 15–19 Feburay 2009, 5pp

Zhu M, Yu K, Luo FL (2010) Switched inductor Z-source inverter. IEEE Trans. Power Electron. 25(8):2150–2158

Li D, Loh PC, Zhu M et al (2013) Generalized multicell switched-inductor and switched-capacitor Z-source inverters. IEEE Trans Power Electron 28(2):837–848

Li D, Loh PC, Zhu M et al (2013) Cascaded multicell trans-Z-source inverters. IEEE Trans Power Electron 28(2):826–836

Galigekere VP, Kazimierczuk MK (2012) Analysis of PWM Z-source DC–DC converter in CCM for steady state. IEEE Trans Circuits Syst I 59(4):854–863

Fang XP (2009) A novel Z-source DC–DC converter. In:Proceediings of IEEE international conference on industrial technology, Chengdu, China, 21–24 April 2008, 5pp

Yang LQ, Qiu DY, ZhangB et al (2014) A modified Z-source DC–DC converter. In:Proceediings of 16th european conference on power electronics and applications (EPE’14-ECCE Europe), Lappeenranta, Finland, 26–28 August 2014, 10pp

Acknowledgements

Funding was provided by National Natural Science Foundation of China (51437005)

Author information

Authors and Affiliations

Corresponding author

Additional information

CrossCheck date: 7 June 2017

Appendix A

Appendix A

This Appendix shows the detailed derivation of the relationship between the efficiency and the duty ratio of the proposed converter given in equation (29).To simplify the calculation, we assume that inductors L 1, L 2 have the same parasitic resistance r L , capacitors C 1, C 2, C 3 and C o have the same ESR r C , and diodes D 1, D 2 and D o have the same forward voltage drop V D . The converter losses, and the voltage and current waveforms are assumed to be piecewise linear segment. Then, the derivation of (29) proceeds as follows.

-

1)

Active switch conduction loss

$$P_{{r_{DS} }} = I_{{S_{{\left( {RMS} \right)}} }}^{2} r_{DS} = \frac{{\left( {1 + D} \right)^{2} }}{{D\left( {1 - 2D} \right)^{2} }}\frac{{P_{o} }}{{R_{L} }}r_{DS}$$(A1) -

2)

Active switch switching loss

$$P_{sw} = \frac{1}{2}V_{{off_{ - } state}} I_{{on_{ - } state}} \left( {t_{r} + t_{f} } \right)f_{s} = \frac{{\left( {1 + D} \right)\left( {t_{r} + t_{f} } \right)f_{s} V_{in} }}{{2D\left( {1 - 2D} \right)^{2} }}\frac{{P_{o} }}{{V_{o} }}$$(A2) -

3)

Diode conduction losses

$$P_{{V_{F} }} = V_{F} I_{D} = \frac{4 - 5D}{1 - 2D}\frac{{P_{o} }}{{V_{o} }}V_{F}$$(A3) -

4)

Inductor conduction losses

$$P_{{r_{L} }} = I_{{L_{{\left( {RMS} \right)}} }}^{2} r_{L} = \frac{{\left( {2 - D} \right)^{2} + \left( {1 + D} \right)^{2} }}{{\left( {1 - 2D} \right)^{2} }}\frac{{P_{o} }}{{R_{L} }}r_{L}$$(A4) -

5)

Capacitor conduction losses

$$\begin{aligned} P_{{r_{C} }} = I_{{C_{{\left( {RMS} \right)}} }}^{2} r_{C} \hfill \\ \, = \frac{{\left( {1 - D + D^{2} } \right)^{2} + \left( {2D - D^{2} } \right)^{2} + \left( {2 - 2D + D^{2} } \right)\left( {1 - 2D} \right)^{2} }}{{D\left( {1 - D} \right)\left( {1 - 2D} \right)^{2} }}\frac{{P_{o} }}{{R_{L} }}r_{C} \hfill \\ \end{aligned}$$(A5)

Based on (A1)-(A5), the total power losses can be obtained as:

Therefore, the efficiency of the proposed converter can be derived as:

Substituting (A1), (A2), (A3), (A4) and (A5) into (A7), one can obtain

where Q = (1 − D + D 2)2 + (2D − D 2)2 + (2 − 2D + D 2)(1 − 2D)2; t r is the turn-on delay time; t f is the turn-off delay time. Therefore, (A8) is the same as (29).

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

ZHU, X., ZHANG, B. High step-up quasi-Z-source DC–DC converters with single switched capacitor branch. J. Mod. Power Syst. Clean Energy 5, 537–547 (2017). https://doi.org/10.1007/s40565-017-0304-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40565-017-0304-1