Abstract

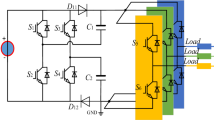

This paper presents a unique five-level inverter consisting of one DC voltage source and one capacitor. Here the capacitor acts like another source and is fed to the inverter along with the DC voltage source. The DC voltage source is also used to charge the capacitor with the help of an additional switch used inside the converter circuit. An inductor is used in the charging path to reduce the peak of the charging current. The in-phase disposition sinusoidal pulse-width modulation technique is used to generate the gate pulse for the devices of the presented converter. The proposed topology operates in two modes. One is energy stored mode and another is energy release mode. By using both modes of operation, the additional switch is triggered to charge the capacitor. The capacitor’s charging and discharging mode and inverter power loss have been described thoroughly in this paper. The proposed five-level inverter topology has been developed and verified inside the laboratory. The controller of the converter has been implemented in the FPGA platform. The experimental results are obtained to evaluate the efficacy of the proposed inverter.

Similar content being viewed by others

References

Wang, Y.; Yuan, Y.; Li, G.; Chen, T.; Wang, K.; Liang, J.: A generalized multilevel inverter based on T-Type switched capacitor module with reduced devices. Energies (Basel) 13, 4406 (2020)

Habib, S.; Khan, M.M.; Abbas, F.; Ali, A.; Faiz, M.T.; Ehsan, F.; Tang, H.: Contemporary trends in power electronics converters for charging solutions of electric vehicles. CSEE J. Power Energy Syst. 6, 911–929 (2020)

Wang, Y.; Yuan, Y.; Li, G.; Ye, Y.; Wang, K.; Liang, J.: A T-type switched-capacitor multilevel inverter with low voltage stress and self-balancing. IEEE Trans. Circuit Syst. 68, 2257–2270 (2021)

Lin, W.; Zeng, J.; Fu, B.; Yan, Z.; Liu, J.: Switched-capacitor based seven-level boost inverter with reduced devices. CSEE J. Power Energy Syst. 10, 381–391 (2021)

Wang, P.; Ma, S.; Akram, S.; Zhou, K.; Chen, Y.; Nazir, M.T.: Design of archimedes spiral antenna to optimize for partial discharge detection of inverter fed motor insulation. IEEE Access 8, 193202–193213 (2020)

Akram, S.; Wu, G.; Gao, G.; Liu, Y.: Effect of surface discharge on nano filled polyimide film under square voltage. In: 2015 IEEE Electrical Insulation Conference (EIC), pp. 226–229 (2015)

Norambuena, M.; Kouro, S.; Dieckerhoff, S.; Rodriguez, J.: Reduced multilevel converter: a novel multilevel converter with a reduced number of active switches. IEEE Trans. Ind. Electron. 65, 3636–3645 (2017)

Zeng, J.; Lin, W.; Cen, D.; Liu, J.: Novel K-type multilevel inverter with reduced components and self-balance. IEEE J. Emerg. Sel. Top. Power Electron. 8, 4343–4354 (2019)

Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E.: A survey on neutral-point-clamped inverters. IEEE Trans. Industr. Electron. 57, 2219–2230 (2009)

Susheela, N.; Kumar, P.S.; Sharma, S.K.: Generalized algorithm of reverse mapping based SVPWM strategy for diode-clamped multilevel inverters. IEEE Trans. Ind. Appl. 54, 2425–2437 (2018)

Khazraei, M.; Sepahvand, H.; Corzine, K.A.; Ferdowsi, M.: Active capacitor voltage balancing in single-phase flying-capacitor multilevel power converters. IEEE Trans. Industr. Electron. 59, 769–778 (2011)

Wang, Y.; Wang, K.; Li, G.; Wu, F.; Wang, K.; Liang, J.: Generalized switched-capacitor step-up multilevel inverter employing single DC source. CSEE J. Power Energy Syst. 8, 439–451 (2021)

Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A.: A survey on cascaded multilevel inverters. IEEE Trans. Industr. Electron. 57, 2197–2206 (2009)

Mokhberdoran, A.; Ajami, A.: Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology. IEEE Trans. Power Electron. 29, 6712–6724 (2014)

Lin, W.; Zeng, J.; Liu, J.; Yan, Z.; Hu, R.: Generalized symmetrical step-up multilevel inverter using crisscross capacitor units. IEEE Trans. Industr. Electron. 67, 7439–7450 (2019)

Lu, S.; Mariéthoz, S.; Corzine, K.A.: Asymmetrical cascade multilevel converters with noninteger or dynamically changing dc voltage ratios: concepts and modulation techniques. IEEE Trans. Industr. Electron. 57, 2411–2418 (2010)

Rech, C.; Pinheiro, J.R.: Hybrid multilevel converters: unified analysis and design considerations. IEEE Trans. Industr. Electron. 54, 1092–1104 (2007)

Kjaer, S.B.; Pedersen, J.K.; Blaabjerg, F.: A review of single-phase grid-connected inverters for photovoltaic modules. IEEE Trans. Ind. Appl. 41, 1292–1306 (2005)

Ahmad, A.; Singh, R.K.; Beig, A.R.: Switched-capacitor based modified extended high gain switched boost Z-source inverters. IEEE Access 7, 179918–179928 (2019)

Ellabban, O.; Abu-Rub, H.: Z-source inverter: topology improvements review. IEEE Ind. Electron. Mag. 10, 6–24 (2016)

Panda, K.P.; Bana, P.R.; Panda, G.: A switched-capacitor self-balanced high-gain multilevel inverter employing a single DC source. IEEE Trans. Circuits Syst. II Express Briefs 67, 3192–3196 (2020)

Axelrod, B.; Berkovich, Y.; Ioinovici, A.: A cascade boost-switched-capacitor-converter-two level inverter with an optimized multilevel output waveform. IEEE Trans. Circuits Syst. I Regul. Pap. 52, 2763–2770 (2005)

Liu, J.; Wu, J.; Zeng, J.; Guo, H.: A novel nine-level inverter employing one voltage source and reduced components as high-frequency AC power source. IEEE Trans. Power Electron. 32, 2939–2947 (2016)

Barzegarkhoo, R.; Moradzadeh, M.; Zamiri, E.; Kojabadi, H.M.; Blaabjerg, F.: A new boost switched-capacitor multilevel converter with reduced circuit devices. IEEE Trans. Power Electron. 33, 6738–6754 (2017)

Vahedi, H.; Labbé, P.-A.; Al-Haddad, K.: Sensor-less five-level packed U-cell (PUC5) inverter operating in stand-alone and grid-connected modes. IEEE Trans. Ind. Inf. 12, 361–370 (2015)

Naik, B.S.; Umanand, L.; Gopakumar, K.; Reddy, B.S.: A two-phase five-level converter with least number of power switches requiring only a single DC source. IEEE J. Emerg. Sel. Top. Power Electron. 6, 1942–1952 (2018)

Lee, S.S.; Yang, Y.; Siwakoti, Y.P.; Lee, K.B.: A novel boost cascaded multilevel inverter. IEEE Trans. Ind. Electron. 68, 8072–8080 (2020)

Barzegarkhoo, R.; Lee, S.S.; Siwakoti, Y.P.; Khan, S.A.; Blaabjerg, F.: Design, control, and analysis of a novel grid-interfaced switched-boost dual T-type five-level inverter with common-ground concept. IEEE Trans. Ind. Electron. 68, 8193–8206 (2020)

Kazimierczuk, M.K.: Pulse-width modulated DC-DC power converters. Wiley (2015)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Sahoo, R., Roy, M. An FPGA-Based Balancing of Capacitor Voltage for a Five-Level CHB Inverter. Arab J Sci Eng (2024). https://doi.org/10.1007/s13369-024-08972-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s13369-024-08972-0