Abstract

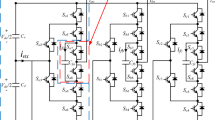

In this paper, a balancing control scheme of DC-link capacitor voltages for five-level hybrid T-type (5L-HT) inverters is proposed, where existing auxiliary balancing circuit is eliminated. The 5L-HT inverter has a significant advantage of the reduced number of devices compared with other five-level inverter topologies. However, this inverter requires an auxiliary balancing circuit, which is used to rectify the voltage imbalance at the DC-link capacitors, and thus negates the competitiveness of this topology in terms of device count and converter volume. To eliminate the auxiliary circuit, a carrier-overlapped PWM (COPWM) is applied in place of the conventional level-shifted PWM (LSPWM) to control the neutral-point currents, where the duty ratios of switches are adjusted by PI controllers. As a result, although the THD of the output voltage is rather increased, the cost and volume are saved by 27% and 52%, respectively, for a 1-MW/6.6-kV system. The effectiveness of the proposed balancing control method for the 5L-HT inverter has been verified through the simulation and experimental results for the prototype hardware.

Similar content being viewed by others

Data availability

The datasets generated during and/or analysed during current study are not publicaly available but may be available from the corresponding author if the request is reasonable.

References

Koshti, A. K., Rao M. N.: A brief review on multilevel inverter topologies. In: Proc. IEEE international conference on data management, analytics and innovation, pp. 187–193 (2017)

Gupta, K.K., Ranjan, A., Bhatnagar, P., Sahu, L.K., Jain, S.: Multilevel inverter topologies with reduced device count: a review. IEEE Trans. Power Electron. 31(1), 135–151 (2016)

El-Hosainy, A., Hamed, H. A., Azazi, H. Z., El-Kholy, E. E.: A review of multilevel inverter topologies, control techniques, and applications. In: Proc. IEEE International Middle East Power Systems Conference, pp. 1265–1275 (2017)

Omer, P., Kumar, J., Surjan, B.S.: A review on reduced switch count multilevel inverter topologies. IEEE Access 8, 22281–22302 (2020)

Soto, D., Green, T.C.: A comparison of high-power converter topologies for the implementation of FACTS controllers. IEEE Trans. Ind. Electron. O. 49(5), 1072–1080 (2002)

Wu, B.: High-power converters and AC drives. Wiley, Hoboken (2007)

Rodriguez, J., Lai, J.-S., Peng, F.-Z.: Multilevel inverters: a survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 49(4), 724–728 (2002)

Yuan, X., Barbi, I.: Fundamentals of a new diode clamping multilevel inverter. IEEE Trans. Power Electron. 15(4), 711–718 (2000)

Hakami, S.S., Lee, K.-B.: Proper flying capacitor selection for performance enhancement of five-level hybrid active neutral-point-clamped inverters. J. Power Electron. 22, 1687–1698 (2022)

Saberi, S., Rezaie, B.: Computationally efficient direct predictive speed control of PMSMs fed by three-level NPC convertors with guaranteed stability. J. Power Electron. 22, 1131–1141 (2022)

Anthon, A., Zhang, Z., Andersen, M.A.E., Holmes, D.G., McGrath, B., Teixeira, C.A.: The benefits of SiC MOSFETs in a T-Type inverter for grid-tie applications. IEEE Trans. Power Electron. 32(4), 2808–2821 (2017)

Aliaga, R., Rojas, D., Muñoz, J., et al.: 27-Level asymmetric multilevel inverter for photovoltaic energy conversion. J. Power Electron. 20, 904–915 (2020)

Zhuge, H., Zhang, L., Lou, X., et al.: Evaluation of DPWM schemes for Si/SiC three-level hybrid active NPC inverters. J. Power Electron. 22, 1825–1835 (2022)

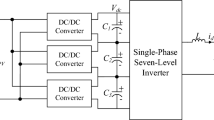

Hua, T., Ye, Y., Wang, X.: A new 7-level inverter for active and reactive power compensation using PEV in grid-connected applications. In: Proc. IEEE international conference on power electronics systems and applications, pp. 1–6 (2020)

Durgasukumar, G., Pathak, M. K.: THD reduction in performance of multi-level inverter fed induction motor drive. In: Proc. IEEE IICPE, pp. 1–6 (2011)

Mondal, G., Gopakumar, K., Tekwani, P. N., Levi, E.: A five-level inverter scheme with common-mode voltage elimination by cascading conventional two-level and three-level NPC inverters for an induction motor drive. In: Proc. IEEE European Conference on Power Electronics and Applications, pp. 1–10 (2007)

Jahan, H. K., Mohammadpour Shotorbani, A., Rostami Noshahr, M. R., Peimani, M., Sabahi, M., Blaabjerg, F.: Partial two-stage four-level inverter for grid-tied PV application. In: Proc. IEEE power electronics, drive systems, and technologies conference, pp. 264–268 (2022)

Tirupathi, A., Annamalai, K., Veeramraju Tirumala, S.: A three-phase inverter circuit using half-bridge cells and T-NPC for medium-voltage applications. Int J Circ Theor Appl. 48, 1744–1765 (2020)

Dao, N.D., Lee, D.-C.: Operation and control scheme of a five-level hybrid inverter for medium-voltage motor drives. IEEE Trans. Power Electron. 33(12), 10178–10187 (2018)

Narimani, M., Wu, B., Zargari, N.R.: A novel five-level voltage source inverter with sinusoidal pulse width modulator for medium-voltage applications. IEEE Trans. Power Electron. 31(3), 1959–1967 (2016)

Karthik, A., Loganathan, U.: A reduced component count five-level inverter topology for high reliability electric drives. IEEE Trans. Power Electron. 35(1), 725–732 (2020)

Davis, T.T., Dey, A.: Investigation on extending the dc bus utilization of a single-source five-level inverter with Single capacitor-fed H-bridge per phase. IEEE Trans. Power Electron. 34(3), 2914–2922 (2019)

Wang, Z., Gao, C., Chen, C., Xiong, J., Zhang, K.: Ripple analysis and capacitor voltage balancing of five-level hybrid clamped Inverter (5L-HC) for medium-voltage applications. IEEE Access 7, 86077–86089 (2019)

Pribadi, J., Le, D.D., Lee, D.-C.: Novel control scheme for fvelevel hybrid fying-capacitor inverters without DC-link balancing circuits. IEEE Trans. Power Electron. 37(7), 8133–8145 (2022)

Saeedifard, M., Iravani, R., Pou, J.: Analysis and control of DC-capacitor-voltage-drift phenomenon of a passive front-end five-level converter. IEEE Trans. Ind. Electron. 54(6), 3255–3266 (2007)

Wang, K., Zheng, Z., Xu, L., Li, Y.: A generalized carrier-overlapped PWM method for neutral-point-clamped multilevel converters. IEEE Trans. Power Electron. 35(9), 9095–9106 (2020)

Wang, K., Zheng, Z., Xu, L., Li, Y.: Neutral-point voltage balancing method for five-level NPC inverters based on carrier-overlapped PWM. IEEE Trans. Power Electron. 36(2), 1428–1440 (2021)

Kim, M.-S., Lee, D.-C.: DC-link capacitor voltage balancing control without auxiliary circuits for five-level hybrid t-type neural-point clamped inverters. In: IEEE International Conference on Communications and Electronics, pp. 421–425 (2022)

Singh, S., Sonar, S.: A new SVPWM technique to Reduce the inductor current ripple of three-phase Z-source inverter. IEEE Trans. Ind. Electron. 67(5), 3540–3550 (2020)

https://www.infineon.com/cms/en/product/power/igbt/igbt-modules/ff450r33t3e3/ (2022). Accessed 24 Sept 2022

https://www.infineon.com/cms/en/product/power/igbt/igbt-modules/dd500s65k3/ (2022) Accessed 24 Sept 2022

https://www.mouser.kr/ProductDetail/KEMET/C44UOGT7110M52K?qs=Cb2nCFKsA8p2K3edRsKtNQ%3D%3D (2022) Accessed 24 Sept 2022

https://www.coilws.com/index.php?main_page=index&cPath=208_212_366 (2022) Accessed 24 Sept 2022

Acknowledgements

This research was supported by the Yeungnam University Research Grants in 2020.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kim, MS., Lee, DC. Balancing control scheme of DC-link capacitor voltages for five-level hybrid T-type inverters without auxiliary circuit. J. Power Electron. 23, 467–477 (2023). https://doi.org/10.1007/s43236-023-00592-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-023-00592-5