Abstract

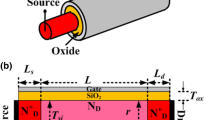

In this work, an innovative architecture of gate underlap junctionless double-gate MOSFET has been introduced with the idea of using triangular oxide layers to control the electric field near the drain side. A two-dimensional analytical model for the device has been developed based on 2D Poisson’s equation. We have applied Schwartz-Christoffel transformation to model the gate capacitance in the overlap region and conformal mapping to model the fringing electric flux in the gate underlap region and derived exclusive expressions for central potential, drain current, threshold voltage and subthreshold slope subsequently. TCAD tools have been adopted to validate our model. The results emphasize the effects of various device dimensions, especially the maximum oxide thickness and underlap length on various device parameters. The model is able to predict the impact of trapped charges on various device parameters. The structure exhibits excellent control over short channel effects and good designing flexibility obtained by varying the oxide geometry. We have also presented an application of the structure in the form of a CMOS inverter that yields promising results for low-power applications.

Similar content being viewed by others

References

C. Lee, A. Afzalian, N. Akhavan, R. Yan, I. Ferain and J. Colinge, "Junctionless multigate field-effect transistor", Appl Phys Lett, vol. 94, no. 5, p. 053511, 2009, https://doi.org/10.1063/1.3079411

Jaiswal N, Kranti A (2018) A model for gate-underlap-dependent Short- Channel effects in Junctionless MOSFET. IEEE Trans Electron Devices 65(3):881–887. https://doi.org/10.1109/TED.2018.2796602

Munteanu D, Autran J-L (2012) 3-D numerical simulation of bipolar amplification in Junctionless double-gate MOSFETs under heavy-ion irradiation. IEEE Trans Nucl Sci 59(4):773–780. https://doi.org/10.1109/TNS.2012.2184139

Park C-H, Ko M-D, Kim K-H, Sohn C-W, Baek CK, Jeong Y-H, Lee J-S (2011) “Comparative study of fabricated junctionless and inversion-mode nanowire FETs”. 69th Device Research Conference. https://doi.org/10.1109/drc.2011.5994478

Lee C-W, Borne A, Ferain I, Afzalian A, Yan R, Akhavan ND, Razavi P, Colinge J-P (2010) High-temperature performance of silicon Junctionless MOSFETs. IEEE Trans Electron Devices 57(3):620–625. https://doi.org/10.1109/TED.2009.2039093

Taur Y, Chen H-P, Wang W, Lo S-H, Wann C (2012) On–off charge–voltage characteristics and dopant number fluctuation effects in Junctionless double-gate MOSFETs. IEEE Transactions on Electron Devices 59(3):863–866. https://doi.org/10.1109/TED.2011.2181392

Vinet M, Poiroux T, Widiez J, Lolivier J, Previtali B, Vizioz C, Guillaumot B, Tiec YL, Besson P, Biasse B, Allain F, Casse M, Lafond D, Hartmann J-M, Morand Y, Chiaroni J, Deleonibus S (2005) Bonded planar double-metal-gate NMOS transistors down to 10 nm. IEEE Electron Device Letters 26(5):317–319. https://doi.org/10.1109/LED.2005.846580

Saha P, Banerjee P, Dash DK, Sarkar SK (2018) Exploring the Short-Channel characteristics of asymmetric Junctionless double-gate silicon-on-nothing MOSFET. J Mater Eng Perform 27(6):2708–2712. https://doi.org/10.1007/s11665-018-3281-2

Bansal A, Roy K (2007) Analytical subthreshold potential distribution model for gate underlap double-gate MOS transistors. IEEE Trans Electron Devices 54(7):1793–1798. https://doi.org/10.1109/ted.2007.898042

Sarkhel S, Manna B, Jana A, Naskar K, Sarkar SK (2013) “Analytical potential distribution model of symmetric double gate underlap MOSFET with binary metal alloy as gate electrode for subdued SCEs”. 2013 Annual international conference on emerging research areas and 2013 international conference on microelectronics, communications and renewable energy. https://doi.org/10.1109/aicera-icmicr.2013.6575979

Koley K, Dutta A, Saha SK, Sarkar CK (2015) Analysis of high-κ spacer asymmetric underlap DG-MOSFET for SOC application. IEEE Trans Electron Devices 62(6):1733–1738. https://doi.org/10.1109/ted.2015.2397699

Bansal A, Paul B, Roy K (2004) “Impact of gate underlap on gate capacitance and gate tunneling current in 16 nm DGMOS devices”. 2004 IEEE International SOI Conference (IEEE Cat. No.04CH37573). https://doi.org/10.1109/soi.2004.1391570

Hareland S, Tasch A, Maziar C (1993) New structural approach for reducing punchthrough current in deep submicrometre MOSFETs and extending MOSFET scaling. Electron Lett 29(21):1894. https://doi.org/10.1049/el:19931261

Ouyang Q, Chen X, Mudanai S, Wang X, Kencke D, Tasch A, Register L, Banerjee S (2000) A novel Si/SiGe heterojunction pMOSFET with reduced short-channel effects and enhanced drive current. IEEE Trans Electron Devices 47(10):1943–1949. https://doi.org/10.1109/16.870577

Chen X, Ouyang Q, Liu K-C, Shi Z, Tasch A, Banerjee S (n.d.) “Vertical P-MOSFETs with heterojunction between source/drain and channel”. 58th DRC. Device Research Conference. Conference Digest (Cat. No.00TH8526). https://doi.org/10.1109/drc.2000.877073

Dash DK, Saha P, Sarkar SK (2017) Analytical modeling of asymmetric hetero-dielectric engineered dual-material DG-TFET. J Comput Electron 17(1):181–191. https://doi.org/10.1007/s10825-017-1102-8

Young K (1989) Analysis of conduction in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36(3):504–506. https://doi.org/10.1109/16.19960

Li W et al. (2017) “600 V GaN vertical V-trench MOSFET with MBE regrown channel”. 2017 75th Annual Device Research Conference (DRC), pp. 1–2. https://doi.org/10.1109/DRC.2017.7999414

Lim G, Kim D-S, Lyu H-K, Park H-J, Shin J-K, Choi P, Lee J-H, Lee M (2004) Characteristics and Modeling of a Nonplanar Nonrectangular Metal Oxide Semiconductor Field Effect Transistor for Charge Sensing in the Si Micro-Fluidic Channel. Jpn J Appl Phys 43:3896–3900

Brown BJ et al. (n.d.) “Tapered gate oxide in ldmos devices”, US 2016/0190269 A1

Hattori T (1998) Trends in wafer cleaning technology. In: Hattori T (ed) Ultraclean surface processing of silicon wafers. Springer, Berlin. https://doi.org/10.1007/978-3-662-03535-1_32

Narang R, Rajendran G, Gupta M, Saxena M (2019) “Analytical model for tapered gate electrode double gate MOSFET incorporating fringing field effects”. Springer Proceedings in Physics The Physics of Semiconductor Devices, pp. 697–705. https://doi.org/10.1007/978-3-319-97604-4_108

Kim J, Kang M, Jeon J, Shin H (2019) Fringe capacitance modeling in NanoPlate MOSFET using conformal mapping. IEEE Trans Electron Devices 66(5):2446–2449. https://doi.org/10.1109/ted.2019.2903546

Xiang Y (2006) The electrostatic capacitance of an inclined plate capacitor. J Electrost 64(1):29–34. https://doi.org/10.1016/j.elstat.2005.05.002

Lang S (1985) Complex analysis. Springer-Verlag, New York

du Val P (1973) Elliptic functions and elliptic curves. Cambridge University Press, Cambridge

Xiang Y, Lin W (2001) A study of electrostatic force on the walls of N-regular polygon-multifin line. J Electrost 50(2):119–128. https://doi.org/10.1016/s0304-3886(00)00031-0

Paul DJ, Abdullah-Al-Kaiser M, Islam MS, Khosru QDM (2018) Fringing-field-based 2-D analytical model for a gate-underlap double-gate TFET. J Comput Electron 17(4):1567–1577. https://doi.org/10.1007/s10825-018-1234-5

Collin RE, Plonsey R (1961) Principles and applications of electromagnetic fields. Tata McGraw-Hill Publishing Company, New Delhi

Singh B, Gola D, Singh K, Goel E, Kumar S, Jit S (2017) 2-D analytical threshold voltage model for dielectric pocket double-gate Junctionless FETs by considering source/drain depletion effect. IEEE Trans Electron Devices 64(3):901–908. https://doi.org/10.1109/TED.2016.2646460

ATLAS (2015) User’s manual. Silvaco Inc., Santa Clara

Naskar K, Jana A, Sarkhel S, Manna B, Sarkar SK (2013) “Study of power dissipation and delay of TWO dimensional SOI and SON based MOSFET inverter”. 2013 Annual international conference on emerging research areas and 2013 international conference on microelectronics, communications and renewable energy. https://doi.org/10.1109/aicera-icmicr.2013.6575980

Vaddi R, Agarwal RP, Dasgupta S (2012) Compact modeling of a generic double-gate MOSFET with gate–S/D underlap for subthreshold operation. IEEE Trans Electron Devices 59:2846–2849. https://doi.org/10.1109/ted.2012.2208464

Manna B, Sarkhel S, Islam N, Sarkar S, Sarkar SK (2012) Spatial composition grading of binary metal alloy gate electrode for Short-Channel SOI/SON MOSFET application. IEEE Trans Electron Devices 59:3280–3287. https://doi.org/10.1109/ted.2012.2220143

Holtij T, Graef M, Hain FM, Kloes A, Iniguez B (2014) Compact model for Short-Channel Junctionless accumulation mode double gate MOSFETs. IEEE Trans Electron Devices 61:288–299. https://doi.org/10.1109/ted.2013.2281615

Basak A, Sarkar A (2020) Drain current modelling of asymmetric Junctionless dual material double gate MOSFET with high K gate stack for analog and RF performance. Silicon. https://doi.org/10.1007/s12633-020-00783-w

Lacord J, Huguenin J-L, Skotnicki T, Ghibaudo G, Boeuf F (2012) Simple and efficient MASTAR threshold voltage and subthreshold slope models for low-doped double-gate MOSFET. IEEE Trans Electron Devices 59:2534–2538. https://doi.org/10.1109/ted.2012.2201942

Jaiswal N, Kranti A (2019) Modeling Short-Channel effects in Core–Shell Junctionless MOSFET. IEEE Trans Electron Devices 66:292–299. https://doi.org/10.1109/ted.2018.2881006

Lee C-W, Ferain I, Afzalian A, Yan R, Akhavan ND, Razavi P, Colinge JP (2010) Performance estimation of junctionless multigate transistors. Solid State Electron 54:97–103. https://doi.org/10.1016/j.sse.2009.12.003

Banerjee P, Sarkar SK (2017) 3-D analytical modeling of high-k gate stack dual-material tri-gate strained silicon-on-nothing MOSFET with dual-material bottom gate for suppressing short channel effects. J Comput Electron 16:631–639. https://doi.org/10.1007/s10825-017-1002-y

Basak S, Saha P, Sarkar SK (2014) A semi 2D analytical Vth model for junctionless double gate nanoscale silicon on nothing (JLDG-SON) MOSFET. 2014 recent advances in engineering and computational sciences (RAECS). https://doi.org/10.1109/raecs.2014.6799531

Availability of Data and Material

The authors confirm that the data supporting the findings of this study are available within the article.

Author information

Authors and Affiliations

Contributions

All authors whose names appear on the submission.

1) Made substantial contributions to the conception of the work and analysis of data.

2) Drafted the work and revised it critically for important intellectual content;

3) Approved the version to be published; and.

4) Agree to be accountable for all aspects of the work in ensuring that questions related to the accuracy or integrity of any part of the work are appropriately investigated and resolved.

Corresponding author

Ethics declarations

Informed Consent

Not applicable.

Consent to Participate

Not applicable.

Consent for Publication

Not applicable.

Research Involving Human Participants and/or Animals

Not applicable.

Conflict of Interest

The authors have no conflicts of interest relevant to the content of this article to declare.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Maiti, S., De, A. & Sarkar, S.K. Structural Innovation for Better MOSFET Performance Suitable for Low Power Application. Silicon 14, 6219–6231 (2022). https://doi.org/10.1007/s12633-021-01390-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01390-z