Abstract

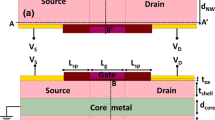

Herein we introduce and investigate a new architectural design strategy for planar single gate field effect transistors (SG-FETs) that delivers advantages from all fronts of design, fabrication and performance perspectives. The amalgamation of schottky buried metal layer (BML) and charge plasma (CP) mechanism of doping in planar single gate architecture yields a novel type of FET called as CP-BML FET. Owing to the schottky BML induced depletion region created on the bottom side of device layer reduces effective device layer thickness (TSi) suppressing short channel effects (SCEs) including drain induced barrier lowering (DIBL) and threshold voltage roll-off. The proposed FET has been analyzed for DC and RF performance figure of merits (FOMs) and compared to counter part state of the art technologies with reference to ITRS performance projections. The proposed FET is also investigated the performance FOMs on for criticality of physical parameters including gate length (Lg), device layer thickness (TSi), BML workfunction (ϕBML). The ION and IOFF for proposed device at Lg = 20nm read at 730μ A/μ m and 7 × 10− 2 pA/μ m respectively. RF performance analysis reveal transition frequency (ft) of 390 GHz with SS \(\simeq \ \text {75mV/dec}\) coherent with ITRS performance projections. It is found that ultra scaled (7 nm) proposed device exhibits intrinsic delay τ of 0.6 ps which is superior to ITRS projections of 1.71 ps at 28 nm technology node. The proposed device yields Pdyn of 0.248 fJ/μ m at Lg= 7nm implicating it to be potential candidate for low power with high performance application requirements.

Similar content being viewed by others

Data Availability

There is no linked research data for this submission.

References

Sheu B, Olstein K (2015) . IEEE Solid-State Circuits Magazine 7(2):67. https://doi.org/10.1109/MSSC.2015.2418472

Ávila Herrera F, Hirano Y, Miura-Mattausch M, Iizuka T, Kikuchihara H, Mattausch HJ, Ito A (2019) . IEEE Trans Electron Devices 66(9):3726. https://doi.org/10.1109/TED.2019.2931749

Jaiswal N, Kranti A (2018) . IEEE Trans Electron Devices 65(9):3669. https://doi.org/10.1109/TED.2018.2856839

Angelov GV, Nikolov DN, Hristov MH (2019) . J Electr Comput Eng 2019:4792461. https://doi.org/10.1155/2019/4792461

Gargini P (2017) .. In: 2017 Fifth Berkeley symposium on energy efficient electronic systems steep transistors workshop (E3S). https://doi.org/10.1109/E3S.2017.8246153, pp 1–62

Lu W-Y, Taur Y (2006) . IEEE Trans Electron Devices 53 (5):1137. https://doi.org/10.1109/TED.2006.871879

Pacheco-Sanchez A, Loroch D, Mothes S, Schröter M, Claus M (2016) .. In: 2016 International conference on simulation of semiconductor processes and devices (SISPAD). https://doi.org/10.1109/SISPAD.2016.7605201, pp 277–280

Sahay S, Kumar MJ (2017) . IEEE Trans Electron Devices 64(6):2604. https://doi.org/10.1109/TED.2017.2688134

Xie Q, Wang Z, Taur Y (2017) . IEEE Trans Electron Devices 64(8):3511. https://doi.org/10.1109/TED.2017.2716969

Shafi N, Sahu C, Periasamy C (2019) . IEEE Electron Device Letters 40(6):997. https://doi.org/10.1109/LED.2019.2911334

Colinge J, Lee C, Afzalian A, Akhavan ND, Yan R, Ferain I, Razavi P, O’Neill B, Blake A, White M, Kelleher AM, McCarthy B, Murphy R (2010) . Nature Nanotechnology 5 (3):225. https://doi.org/10.1038/nnano.2010.15

Colinge J, Kranti A, Yan R, Lee C, Ferain I, Yu R, Dehdashti Akhavan N, Razavi P (2011) . Solid-State Electronics 65-66:33. Selected Papers from the ESSDERC 2010 Conference. https://doi.org/10.1016/j.sse.2011.06.004

Sahu C, Singh J (2014) . IEEE Electron Device Letters 35(3):411. https://doi.org/10.1109/LED.2013.2297451

Hueting RJE, Rajasekharan B, Salm C, Schmitz J (2008) . IEEE Electron Device Letters 29(12):1367. https://doi.org/10.1109/LED.2008.2006864

Lahgere A, Kumar MJ (2017) . IEEE Trans Electron Devices 64(1):3. https://doi.org/10.1109/TED.2016.2622741

Gupta PS, Kanungo S, Rahaman H, Dasgupta PS (2012) .. In: 2012 International conference on computing, electronics and electrical technologies (ICCEET). https://doi.org/10.1109/ICCEET.2012.6203784, pp 761–765

Gundapaneni S, Ganguly S, Kottantharayil A (2011) . IEEE Electron Device Letters 32 (3):261. https://doi.org/10.1109/LED.2010.2099204

Shafi N, Sahu C, Periasamy C (2020) . IEEE Sensors J 20(9):4749. https://doi.org/10.1109/JSEN.2020.2964625

Shafi N, Sahu C, Periasamy C (2018) . Superlattices Microstruct 120:75. https://doi.org/10.1016/j.spmi.2018.05.006

Saraswat KC, Brors DL, Fair JA, Monnig KA, Beyers R (1983) . IEEE Trans Electron Devices 30(11):1497. https://doi.org/10.1109/T-ED.1983.21328

Chen C, Liu W, Ma X, Shen Q, Song Z, Lin C (2009) . Thin Solid Films 517(8):2724. https://doi.org/10.1016/j.tsf.2008.10.043. http://www.sciencedirect.com/science/article/pii/S0040609008012704

Zhu S, Huang Y, Ru G, Qu X, Li B (1999) . Journal of The Electrochemical Society 146(7):2712. https://doi.org/10.1149/1.1391997

Alam K, Lake R (2012) . IEEE Trans Electron Devices 59:3250

Ehteshamuddin M, Loan SA, Rafat M (2018) . IEEE Electron Device Letters 39(6):799. https://doi.org/10.1109/LED.2018.2829915

Avci UE, Morris DH, Young IA (2015) . IEEE J Electron Devices Soc 3(3):88. https://doi.org/10.1109/JEDS.2015.2390591

Lee K, Lee J, Kim S, Lee R, Kim S, Kim M, Lee J, Kim S, Park B (2020) . IEEE Trans Nanotechnol 19:168. https://doi.org/10.1109/TNANO.2020.2972605

Chen W, Zhang J, He Q, Zhou H, Huang X, Ren Z, Su K, Mao W, Xue J, Zheng X, Zhang J, Hao Y (2019) . IEEE Trans Electron Devices 66(11):4673. https://doi.org/10.1109/TED.2019.2940504

Kale S, Kondekar PN (2017) . IEEE Trans Electron Devices 64(11):4400. https://doi.org/10.1109/TED.2017.2754881

Tripathy MR, Singh AK, Samad A, Singh PK, Baral K, Jit S (2020) . Semiconductor Science and Technology 35(10):105014. https://doi.org/10.1088/1361-6641/aba418

Yu E, Lee WJ, Jung J, Cho S (2018) IEEE Trans Electron Devices: 1. https://doi.org/10.1109/TED.2018.2808764

Sahay S, Kumar MJ (2016) . IEEE Trans Electron Devices 63(10):4138. https://doi.org/10.1109/TED.2016.2601239

Shafi N, Bhat AM, Parmar JS, Sahu C, Periasamy C (2021) IEEE Trans Nanotechnology: 1–1. https://doi.org/10.1109/TNANO.2021.3089717

Acknowledgments

The authors would like to thank head of the department, Department of Electronics and Communication Engineering, Malaviya National Institute of Technology for providing necessary support for carrying out the simulation work.

Funding

No funding was received for this work.

Author information

Authors and Affiliations

Contributions

The main conception of this work is brainchild of N. Shafi (Author 1). A. M. Bhat, J. S. Parmar and A. Powral provided the necessary support regarding simulation and data interpretation. C. Sahu and C. Periasamy supervised the work and made important discussions and modifications to the final manuscript.

Corresponding author

Ethics declarations

Ethics approval

All procedures performed in studies involving human participants were in accordance with the ethical standards of the institutional and/or national research committee and with the 1964 Helsinki declaration and its later amendments or comparable ethical standards.

Informed Consent

Not applicable.

Competing interests

The authors declare for no competing interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shafi, N., Bhat, A.M., Parmaar, J.S. et al. Virtually Doped Schottky Buried Metal Layer Planar Junctionless FET for SCE Suppression at sub-28nm Technology Nodes. Silicon 14, 4619–4631 (2022). https://doi.org/10.1007/s12633-021-01242-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01242-w