Abstract

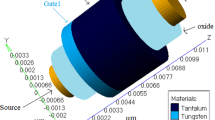

The promising capability of Triple Material Surrounding Gate Junctionless Tunnel FET (TMSG – JL – TFET) based 6 T SRAM structure is demonstrated by employing Germanium (Ge) and High-K gate dielectric material. The high – K insulation guarantees the proposed device to be used in low leakage memory systems. The corresponding analytical model is developed to extract various device parameters such as surface potential, electric field and threshold voltage. The results yield minimization of hot carrier effects at the drain end, when compared to conventional Silicon (Si) based Tunnel FETs (TFETs). Further, the ambipolar characteristics of the proposed device is explored and 6 T Ge – TMS – SG – JL – TFET based SRAM design is proposed. The results are compared with CMOS based SRAM and the analytical model presented is validated using 3D - TCAD ATLAS simulation, which ensures the accuracy and exactness of the developed model.

Similar content being viewed by others

References

Thompson SE, Parthasarathy S (2006) Moore’s law: the future of Si microelectronics. Mater Today 9:20–25. https://doi.org/10.1016/S1369-7021(06)71539-5

Reddy GV, Kumar MJ (2005) A new dual-material double-gate (DMDG) nanoscale SOI MOSFET - two-dimensional analytical modeling and simulation. IEEE Trans Nanotechnol 4:260–268. https://doi.org/10.1109/TNANO.2004.837845

Chen Z, Xiao Y, Tang M, Xiong Y, Huang J, Li J, Gu X, Zhou Y (2012) Surface-potential-based drain current model for long-channel junctionless double-gate MOSFETs. IEEE Trans Electron Devices 59:3292–3298. https://doi.org/10.1109/TED.2012.2221164

Preethi S, Balamurugan NB (2020) Analytical modeling of surrounding gate Junctionless MOSFET using finite differentiation method. Silicon. https://doi.org/10.1007/s12633-020-00653-5

Baruah RK, Paily RP (2014) A dual-material gate junctionless transistor with high-k spacer for enhanced analog performance. IEEE Trans Electron Devices 61:123–128. https://doi.org/10.1109/TED.2013.2292852

Lee MJ, Choi WY (2011) Analytical model of single-gate silicon-on-insulator (SOI) tunneling field-effect transistors (TFETs). Solid State Electron 63:110–114. https://doi.org/10.1016/j.sse.2011.05.008

Ghosh B, Akram MW (2013) Junctionless tunnel field effect transistor. IEEE Electron Device Lett 34:584–586. https://doi.org/10.1109/LED.2013.2253752

Bal P, Ghosh B, Mondal P, Akram MW, Tripathi BMM (2014) Dual material gate junctionless tunnel field effect transistor. J Comput Electron 13:230–234. https://doi.org/10.1007/s10825-013-0505-4

Long W, Ou H, Kuo J, Chin KK (1999) Dual-material gate (DMG) field effect transistor. IEEE Trans Electron Devices 46:865–870. https://doi.org/10.1109/16.760391

Agrawal AK, Koutilya PNVR, Jagadesh KM (2015) A pseudo 2-D surface potential model of a dual material double gate junctionless field effect transistor. J Comput Electron 14:686–693. https://doi.org/10.1007/s10825-015-0710-4

Priya GL, Balamurugan NB (2019) New dual material double gate junctionless tunnel FET: subthreshold modeling and simulation. AEU - Int J Electron Commun 99:130–138. https://doi.org/10.1016/j.aeue.2018.11.037

Kumar MJ, Chaudhry A (2004) Two-dimensional analytical modeling of fully depleted DMG SOI MOSFET and evidence for diminished SCEs. IEEE Trans Electron Devices 51:569–574. https://doi.org/10.1109/TED.2004.823803

Skotnicki T, Fenouillet-Beranger C, Gallon C, Boeuf F, Monfray S, Payet F, Pouydebasque A, Szczap M, Farcy A, Arnaud F, Clerc S, Sellier M, Cathignol A, Schoellkopf JP, Perea E, Ferrant R, Mingam HÉ (2008) Innovative materials, devices, and CMOS technologies for low-power mobile multimedia. IEEE Trans Electron Devices 55:96–130. https://doi.org/10.1109/TED.2007.911338

Robertson J (2004) High density plasma enhanced chemical vapor deposition of optical thin films. EurPhys J ApplPhys 28:265–291. https://doi.org/10.1051/epjap

Toh EH, Wang GH, Chan L, Sylvester D, Heng CH, Samudra GS, Yeo YC (2008) Device design and scalability of a double-gate tunneling field-effect transistor with silicon - germanium source. Jpn J ApplPhys 47:2593–2597. https://doi.org/10.1143/JJAP.47.2593

Venkatesh M, Priya GL, Balamurugan NB (2020) Investigation of Ambipolar conduction and RF stability performance in novel germanium source dual halo dual dielectric triple material surrounding gate TFET. Silicon 13:911–918. https://doi.org/10.1007/s12633-020-00856-w

Priya GL, Balamurugan NB (2018) Subthreshold modeling of triple material gate-all-around junctionless tunnel FET with germanium and high-K gate dielectric material.Journal of microelectronics. Electronic Components Mater 48:53–61

Boucart K, IonescuAM (2007) Double-gate tunnel FETs with high-k gate dielectric. IEEE Trans Electron Devices 54:1725–1733. https://doi.org/10.1109/TED.2007.899389

Venkatesh M, Balamurugan NB (2021) Influence of threshold voltage performance analysis on dual halo gate stacked triple material dual gate TFET for ultra low power applications. Silicon 13:275–287. https://doi.org/10.1007/s12633-020-00422-4

Venkatesh M, Balamurugan NB (2019) New subthreshold performance analysis of germanium based dual halo gate stacked triple material surrounding gate tunnel field effect transistor. Superlattices and Microstructures – Elsevier 130:485–498. https://doi.org/10.1016/j.spmi.2019.05.016

Ajayan J, Nirmal D, Prajoon P, Charles PJ (2017) Analysis of nanometer-scale InGaAs/InAs/InGaAs composite channel MOSFETs using high-K dielectrics for high speed applications. AEU - Int J Electron Commun 79:151–157. https://doi.org/10.1016/j.aeue.2017.06.004

Ren C, Yu HY, Kang JF, Wang XP, Ma HHH, Yeo YC, Chan DSH, Li MF, Kwong DL (2004) A dual-metal gate integration process for CMOS with sub-1-nm EOT HfO2 by using HfN replacement gate. IEEE Electron Device Lett 25:580–582. https://doi.org/10.1109/LED.2004.832535

Darwin S, Samuel TSA (2019) A holistic approach on Junctionless dual material double gate ( DMDG ) MOSFET with high k gate stack for low power digital applications. Silicon 12:393–403. https://doi.org/10.1007/s12633-019-00128-2

Priya GL, Balamurugan NB (2020) Improvement of subthreshold characteristics of Dopingless tunnel FET using hetero gate dielectric material: analytical modeling and simulation. Silicon 12:2189–2201. https://doi.org/10.1007/s12633-019-00314-2

Iniguez B, Jimenez D, Roig J, Hamid HA, Marsal LF, Pallarès J (2005) Explicit continuous model for long-channel undoped surrounding gate MOSFETs. IEEE Trans Electron Devices 52:1868–1873. https://doi.org/10.1109/TED.2005.852892

Tsormpatzoglou A, Dimitriadis CA, Clerc R, Pananakakis G, Ghibaudo G (2008) Semianalyticalmodeling of short-channel effects in lightly doped silicon trigate MOSFETs. IEEE Trans Electron Devices 55:2623–2631. https://doi.org/10.1109/TED.2008.2003096

Chen YN, Fan ML, Pi-Ho Hu V, Pin S, Chuang C (2013) Design and analysis of robust tunneling FET SRAM. IEEE Trans Electron Devices 60:1092–1098. https://doi.org/10.1109/TED.2013.2239297

Agarwal N, Liu H, Arghavani R, Narayanan V, Datta S (2015) Impact of variation in Nanoscale silicon and non-silicon FinFETs and tunnel FETs on device and SRAM performance. IEEE Trans Electron Devices 62:1691–1697. https://doi.org/10.1109/TED.2015.2406333

Liu JS, Clavel MB, Hudait MK (2017) An energy-efficient tensile-strained Ge/InGaAs TFET 7T SRAM cell architecture for ultralow-voltage applications. IEEE Trans Electron Devices 64:2193–2200. https://doi.org/10.1109/TED.2017.2675364

Young K (1989) Analysis of conduction in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36:504–506. https://doi.org/10.1109/16.19960

Suzuki K (2000) Short Channel MOSFET model using a universal channel depletion width parameter. IEEE Trans Electron Devices 47:1202–1208. https://doi.org/10.1109/16.842962

Acknowledgments

We thank the anonymous referees for their useful suggestions.

Availability of Data and Material

There are no linked research data sets for this submission. The following reason is given: No data was used for the research described in the article.

Code Availability

Not Applicable.

Funding

The authors of the manuscript did not receive any funding, grants, or in-kind support in support of the research or the preparation of the manuscript.

Author information

Authors and Affiliations

Contributions

Author 1 (G. Lakshmi Priya): Conceived and design the analysis, contributed data and analysis tools, and wrote the paper. Author 2 (M. Venkatesh): Performed the analysis, calibrated the results, and wrote the paper. Author 3 (N. B. Balamurugan): Worked in TCAD portion of the proposed device, Experimental data analysis. Author 4 (T. S. Arun Samuel): Worked in TCAD simulation of SRAM design, and wrote the paper for the corresponding portion.

Corresponding author

Ethics declarations

Conflict of Interest

All authors have participated in (a) conception and design, or analysis and interpretation of the data; (b) drafting the article or revising it critically for important intellectual content; and (c) approval of the final version. This manuscript has not been submitted to, nor is under review at, another journal or other publishing venue. The authors have no affiliation with any organization with a direct orindirect financial interest in the subject matter discussed in the manuscript.

Ethical Approval

“All procedures performed in studies involving human participants were in accordance with the ethical standards of the institutional and/or national research committee and with the 1964 Helsinki declaration and its later amendments or comparable ethical standards.

Informed Consent

“Informed consent was obtained from all individual participants included in the study.”

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Priya, G.L., Venkatesh, M., Balamurugan, N.B. et al. Triple Metal Surrounding Gate Junctionless Tunnel FET Based 6T SRAM Design for Low Leakage Memory System. Silicon 13, 1691–1702 (2021). https://doi.org/10.1007/s12633-021-01075-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01075-7