Abstract

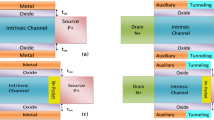

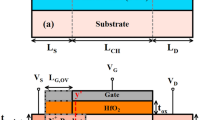

This article presents a study on the subthreshold swing (SS) and the ON–OFF current ratio of a negative capacitance source pocket double-gate tunnel field-effect transistor (NC-SP-DGTFET). In this analysis, a novel device is developed that integrates gate and channel engineering techniques. The combination of the ferroelectric material hafnium zirconium oxide (HZO) with the dielectric material SiO2 generates a negative capacitance (NC) effect. Additionally, the incorporation of a totally depleted source pocket into the DGTFET reduces the tunneling width. The addition of NC has the potential to improve the SS through the amplification of the electric field at the tunnel junction. Moreover, it has been observed that a fully depleted source pocket within the source/channel region significantly enhances the ION current when compared to the double-gate tunnel field-effect transistor (DGTFET). Following thorough device optimization, there has been a notable enhancement in the ION/IOFF current ratio, SS, and transconductance (gm) by a factor of 1.54 × 1013, 20.8 mV/dec, and 5.102 × 10−4 S/µm, respectively. These improvements signify superior energy efficiency and enhanced performance when compared to both DGTFET and source pocket based DGTFET (SP-DGTFET) configurations. Furthermore, substantial research has been conducted on the variation in electrical properties in relation to the thickness of ferroelectric materials. The findings indicate that the proposed device exhibits considerable potential as a viable option for applications requiring both low power consumption and high operational speed.

Similar content being viewed by others

References

R. Dennard, F. Gaensslen, W.-N. Yu, L. Rideout, E. Bassous, and A. Le Blanc, Design of ion-implanted small MOSFET’S dimensions with very. IEEE J. Solid State Circuits 9(5), 257 (1974).

A. Chaudhry and M.J. Kumar, Controlling short-channel effects in deep-submicron SOI MOSFETs for improved reliability: a review. IEEE Trans. Device Mater. Reliab.Reliab. 4(1), 99 (2004). https://doi.org/10.1109/TDMR.2004.824359.

K. Singh, S. Kumar, E. Goel, B. Singh, S. Dubey, and S. Jit, Effects of elevated source/drain and side spacer dielectric on the drivability optimization of non-abrupt ultra shallow junction gate underlap DG MOSFETs. J. Electron. Mater. 46, 520 (2017). https://doi.org/10.1007/s11664-016-4912-8.

Q. Xie, J. Xu, and Y. Taur, Review and critique of analytic models of MOSFET short-channel effects in subthreshold. IEEE Trans. Electron Devices 59(6), 1569 (2012). https://doi.org/10.1109/TED.2012.2191556.

Malvika, B. Choudhuri, and K. Mummaneni, A review on a negative capacitance field-effect transistor for low-power applications. J. Electron. Mater. 51, 923 (2022). https://doi.org/10.1007/s11664-021-09384-8.

D. Hisamoto, W. Lee, K. Jakub, H. Takeuchi, K. Asano, C. Kao, E. Anderson, T. King, J. Bokor, and C. Hu, FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 47(12), 2320 (2000). https://doi.org/10.1109/16.887014.

P.M. Solomon, K.W. Guarini, Y. Zhang, K. Chan, E.C. Jones, G.M. Cohen, A. Krasnoperova, M. Ronay, O. Dokumaci, H.J. Hovel, J.J. Bucchignano Jr., C. Cabral, C. Lavoie, V. Ku, D.C. Boyd, K.S. Petrarca, J.H. Yoon, and H.S.P. Wong, Two gates are better than one. IEEE Circuits Devices Mag. 19(1), 48 (2003). https://doi.org/10.1109/MCD.2003.1175108.

A. Biswas, S.S. Dan, C. Le Royer, W. Grabinski, and A.M. Ionescu, TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Microelectron. Eng.. Eng. 98, 334 (2012). https://doi.org/10.1016/j.mee.2012.07.077.

K.M.C. Babu and E. Goel, Evolution of tunnel field effect transistor for low power and high speed applications: a review. SILICON 14(17), 11051 (2022). https://doi.org/10.1007/s12633-022-01826-0.

M.R. Uddin Shaikh, and S.A. Loan, Drain-engineered TFET with fully suppressed ambipolarity for high-frequency application. IEEE Trans. Electron Devices 66(4), 1628 (2019). https://doi.org/10.1109/TED.2019.2896674.

W. Li and J.C.S. Woo, Optimization and scaling of Ge-pocket TFET. IEEE Trans. Electron Devices 65(12), 5289 (2018). https://doi.org/10.1109/TED.2018.2874047.

D.B. Abdi and M.J. Kumar, Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Devices Soc. 2(6), 187 (2014). https://doi.org/10.1109/JEDS.2014.2327626.

T. Mikolajick, U. Schroeder, and S. Slesazeck, The past, the present, and the future of ferroelectric memories. IEEE Trans. Electron Devices 67(4), 1434 (2020). https://doi.org/10.1109/TED.2020.2976148.

N. Bagga, N. Chauhan, A. Bulusu, and S. Dasgupta, Demonstration of a novel ferroelectric-dielectric negative capacitance tunnel FET, in 2019 IEEE International Conference on Modeling of Systems and Circuits Devices, MOS-AK India 2019, pp. 102–105, (2019) https://doi.org/10.1109/MOS-AK.2019.8902381.

S. Guha and P. Pachal, Heterojunction negative-capacitance tunnel-FET as a promising candidate for Sub-0.4V VDDDigital logic circuits. IEEE Trans. Nanotechnol.Nanotechnol. 20, 576 (2021). https://doi.org/10.1109/TNANO.2021.3096252.

A. Singh, S.K. Sinha, and S. Chander, Impact of Fe material thickness on performance of raised source overlapped negative capacitance tunnel field effect transistor (NCTFET). SILICON 14(14), 9083 (2022). https://doi.org/10.1007/s12633-022-01696-6.

H.W. Kim and D. Kwon, Gate-Normal negative capacitance tunnel field-effect transistor (TFET) with channel doping engineering. IEEE Trans. Nanotechnol.Nanotechnol. 20, 278 (2021). https://doi.org/10.1109/TNANO.2021.3068572.

M. Kobayashi, K. Jang, N. Ueyama, and T. Hiramoto, Negative capacitance for boosting tunnel FET performance. IEEE Trans. Nanotechnol.Nanotechnol. 16(2), 253 (2017). https://doi.org/10.1109/TNANO.2017.2658688.

Y. Zhao, Z. Liang, Q. Huang, C. Chen, M. Yang, Z. Sun, K. Zhu, H. Wang, S. Liu, T. Liu, P. Yue, G. Han, and R. Huang, A novel negative capacitance tunnel FET with improved subthreshold swing and nearly non-hysteresis through hybrid modulation. IEEE Electron Device Lett. 40(6), 989 (2019). https://doi.org/10.1109/LED.2019.2909410.

G. Rasheed and S. Sridevi, Design and analysis of a dual gate tunnel FET with InGaAs source pockets for improved performance. Microelectron. J. 129, 105587 (2022). https://doi.org/10.1016/j.mejo.2022.105587.

A. Singh, N. Kumar, S.I. Amin, and S. Anand, Implementation of negative capacitance over SiGe sourced doping-less tunnel FET. Superlattices Microstruct. Microstruct. 145, 106580 (2020). https://doi.org/10.1016/j.spmi.2020.106580.

S. Dash, S.K. Mohanty, and G.P. Mishra, Segmented drain engineered tunnel field effect transistor for suppression of ambipolarity. SILICON 14, 1671 (2022). https://doi.org/10.1007/s12633-021-00973-0.

G.D. Das, S. Dash, and G.P. Mishra, Impact of hetero-dielectric engineering on the performance of single gate tunnel FET, in 2018 International Conference on Control, Power, Communication and Computing Technologies (ICCPCCT), Kannur, India, pp. 114–117, (2018) https://doi.org/10.1109/ICCPCCT.2018.8574222.

H. Bennett, International technology roadmap for semiconductors 2015 edition outside system connectivity, ITRS, https://tsapps.nist.gov/publication/get_pdf.cfm?pub_id=919731, http://www.itrs2.net/401/login.php?redirect=/ircfocus-teamsitwg-information.html. Accessed 27 Feb 2024.

H.S.P. Wong, D.J. Frank, P.M. Solomon, C.H.J. Wann, and J.J. Welser, Nanoscale CMOS. Proc. IEEE 87(4), 537 (1999). https://doi.org/10.1109/5.752515.

Sentaurus Device User Guide, Version t-2022,03, Synopsys.inc. (Mountain View, CA, USA, 2022).

J. Gomez, S. Dutta, K. Ni, J.A. Smith, B. Grisafe, A. Khan, and S. Datta, Hysteresis-free negative capacitance in the multi-domain scenario for logic applications, in Technical Digest—International Electron Devices Meeting, IEDM, vol. 2019, no. i, pp. 138–141, (2019) https://doi.org/10.1109/IEDM19573.2019.8993638

C. Gastaldi, M. Cavalieri, A. Saeidi, E. O’Connor, F. Bellando, I. Stolichnov, and A.M. Ionescu, Negative capacitance in HfO2 gate stack structures with and without metal interlayer. IEEE Trans. Electron Devices 69(5), 2680 (2022). https://doi.org/10.1109/TED.2022.3157579.

L. Wang, M.R. Cho, Y.J. Shin, J.R. Kim, S. Das, J.G. Yoon, J.S. Chung, and T.W. Noh, Overcoming the fundamental barrier thickness limits of ferroelectric tunnel junctions through BaTiO3/SrTiO3 composite barriers. Nano Lett. 16(6), 3911 (2016).

C. Yoon, J.H. Lee, S. Lee, J.H. Jeon, J.T. Jang, D.H. Kim, Y.H. Kim, and B.H. Park, Synaptic plasticity selectively activated by polarization-dependent energy-efficient ion migration in an ultrathin ferroelectric tunnel junction. Nano Lett. 17(3), 1949 (2017).

K. Toprasertpong, K. Tahara, Y. Hikosaka, K. Nakamura, H. Saito, M. Takenaka, and S. Takagi, Low operating voltage, improved breakdown tolerance, and high endurance in Hf0.5Zr0.5O2 ferroelectric capacitors achieved by thickness scaling down to 4 nm for embedded ferroelectric memory. ACS Appl. Mater. Interfaces 14, 51137 (2022). https://doi.org/10.1021/acsami.2c15369.

C.I. Lin, A.I. Khan, S. Salahuddin, and C. Hu, Effects of the variation of ferroelectric properties on negative capacitance FET characteristics. IEEE Trans. Electron Devices 63(5), 2197 (2016). https://doi.org/10.1109/TED.2016.2514783.

B. Awadhiya, P.N. Kondekar, and A.D. Meshram, Effect of ferroelectric thickness variation in undoped HfO2-based negative-capacitance field-effect transistor. J. Electron. Mater. 48, 6762 (2019). https://doi.org/10.1007/s11664-019-07483-1.

K. Toprasertpong, K. Tahara, M. Takenaka, and S. Takagi, Evaluation of polarization characteristics in metal/ferroelectric/semiconductor capacitors and ferroelectric field-effect transistors. Appl. Phys. Lett. 116(24), 3 (2020). https://doi.org/10.1063/5.0008060.

P.K. Mudidhe and B.R. Nistala, An analytical drain current modelling of DMGC CGAA FET: a circuit level implementation. Phys. Scr. 98(11), 115008 (2023). https://doi.org/10.1088/1402-4896/acfcec.

A. Singh, S. Chaudhary, S.M. Sharma et al., Improved drive capability of silicon nano tube tunnel FET using halo implantation. SILICON 12, 2555 (2020). https://doi.org/10.1007/s12633-019-00350-y.

S. Yadav, R. Madhukar, D. Sharma et al., A new structure of electrically doped TFET for improving electronic characteristics. Appl. Phys. A 124, 517 (2018). https://doi.org/10.1007/s00339-018-1930-9.

A.N. Hanna and M.M. Hussain, Si/Ge hetero-structure nanotube tunnel field effect transistor. J. Appl. Phys. 117, 1 (2015). https://doi.org/10.1063/1.4905423.

D. Shekhar and A. Raman, Design and analysis of dual-gate misalignment on the performance of dopingless tunnel field effect transistor. Appl. Phys. A 126, 441 (2020). https://doi.org/10.1007/s00339-020-03615-1.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Babu, K.M.C., Goel, E. Analysis of Negative Capacitance Source Pocket Double-Gate TFET with Steep Subthreshold and High ON–OFF Ratio. J. Electron. Mater. (2024). https://doi.org/10.1007/s11664-024-11102-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11664-024-11102-z