Abstract

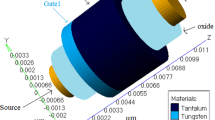

In this paper, the impact of drain drift region and vertical scaling on breakdown performance is investigated through exhaustive technology computer-aided design simulations. The breakdown behavior for drain-connected, gate-connected and dual field plate designs is explored and the physical insights were developed by studying their electric field and potential profile intricacies. Useful optimization laws are unraveled, and by this, breakdown voltage is pushed to higher limits by engineering the gallium nitride (GaN) buffer thickness, drain drift region and field plate length. A thicker GaN buffer with a field plate and larger drain drift region improve the breakdown voltage to maximum values by mitigating punch through and impact ionization mechanisms of performance degradation. The proposed dual field plate combines the merits of using thicker buffer, extended gate drain drift region and both field plates emerging as the optimized design. The breakdown limiting peak electric field is mitigated in dual field plate designs enhancing its breakdown voltage 1.4 to 1.7 times that of a conventional high electron mobility transistor without field plate. Finally, the input and output characteristics are also depicted along with the frequency response. These results demonstrate the efficacy of field plates in reducing and redistributing the critical peak electric fields and thicker GaN buffer giving further cushion to push the breakdown voltage to higher values by negotiating vertical effects such as punch through and lends design guidelines for further improvements.

Similar content being viewed by others

References

U.K. Mishra, L. Shen, T.E. Kazior, and Y. Wu, Proc. IEEE 96, 287 (2008)

O. Ambacher, J. Smart, J.R. Shealy, N.G. Weimann, K. Chu, M. Murphy, W.J. Schaff, L.F. Eastman, R. Dimitrov, L. Wittmer, M. Stutzmann, W. Rieger, and J. Hilsenbeck, J. Appl. Phys. 85, 3222 (1999).

E. Bahat-Treidel, F. Brunner, O. Hilt, E. Cho, J. Wurfl, and G. Trankle, IEEE Trans. Electron Devices 57, 3050 (2010).

D. Visalli, M. Van Hove, J. Derluyn, P. Srivastava, D. Marcon, J. Das, M.R. Leys, S. Degroote, K. Cheng, E. Vandenplas, M. Germain, and G. Borghs, IEEE Trans. Electron Devices 57, 3333 (2010).

T. Kabemura, S. Ueda, Y. Kawada, and K. Horio, IEEE Trans. Electron Devices 65, 3848 (2018).

B. Liao, Q. Zhou, J. Qin, and H. Wang, Electronics 8 (2019).

A. Toprak, S. Osmanoglu, M. Ozturk, D. Yilmaz, O. Cengiz, O. Sen, B. Butun, S. Ozcan, and E. Ozbay, Semicond. Sci. Technol. 33, 125017 (2018).

V. Joshi, S.P. Tiwari, and M. Shrivastava, IEEE Trans. Electron Devices (2019). https://doi.org/10.1109/TED.2018.2878770

N.K. Subramani, J. Couvidat, A.A. Hajjar, J. Nallatamby, and R. Quere, IEEE J. Electron Devices Soc. 39, 107 (2018).

E. Bahat-Treidel, O. Hilt, F. Brunner, J. Wurfl, and G. Trankle, IEEE Trans. Electron Devices 55(12), 3354 (2008).

P. Murugapandiyan, A. Mohanbabu, V.R. Lakshmi, M. Wasim, and K.M. Sundaram, J. Electron Mater. 49, 524 (2020).

H. Chiu, C. Yang, H. Wang, F. Huang, H. Kao, and F. Chien, IEEE Trans. Electron Devices 60, 3877 (2013).

Y.W. Lian, Y.S. Lin, H.C. Lu, Y.C. Huang, and S.H. Hsu, IEEE Electron Device Lett. (2012). https://doi.org/10.1109/LED.2012.2197171

A. Soni, and M. Shrivastava, IEEE Trans. Electron Devices (2020). https://doi.org/10.1109/TED.2020.2976636

W. Mao, W.B. She, C. Yang, J.F. Zhang, X.F. Zheng, C. Wang, and Y. Hao, Chin. Phys. B (2016). https://doi.org/10.1088/1674-1056/25/1/017303

Z. Sheng-Lei, W. Yuan, Y. Xiao-Lei, L. Zhi-Yu, W. Chong, Z. Jin-Cheng, M. Xiao-Hua, and H. Yue, Chin. Phys. B (2014). https://doi.org/10.1088/1674-1056/23/9/097305

M.T. Hassan, T. Asano, H. Tokuda, and M. Kuzuhara, IEEE Electron Device Lett. (2013). https://doi.org/10.1109/LED.2013.2280712

E. Bahat-Treidel, O. Hilt, F. Brunner, V. Sidorov, J. Wurfl, and G. Trankle, IEEE Trans. Electron Devices 57, 1208 (2010)

A. Ray, S. Bordoloi, B. Sarkar, P. Agarwal, and G. Trivedi, J. Electron Mater. 49, 2018 (2020)

S. Karmalker, and U.K. Mishra, Solid State Electron. (2001). https://doi.org/10.1016/S0038-1101(01)00158-7

G. Xie, E. Xu, J. Lee, N. Hashemi, B. Zhang, F.Y. Fu, and W.T. Ng, IEEE Electron Device Lett. (2015). https://doi.org/10.1109/LED.2012.2188492

S. Karmalkar, and U.K. Mishra, IEEE Trans. Electron Devices 48, 1515 (2001).

S. Aamir Ahsan, S. Ghosh, S. Khandelwal, and Y.S. Chauhan, IEEE Trans. Electron Devices 64, 816 (2017).

H. Huang, Y.C. Liang, G.S. Samudra, T. Chang, and C. Huang, IEEE Trans. Power Electron. 29, 2164 (2014).

G. Meneghesso, M. Meneghini, and E. Zanoni, Jpn. J. Appl. Phys. 53, 100211 (2014).

A.M. Bhat, N. Shafi, C. Sahu, and C. Periasamy, J. Electron Mater. (2021). https://doi.org/10.1007/s11664-021-09151-9

N.K. Subramani, J. Couvidat, A.A. Hajjar, J. Nallatamby, R. Sommet, R. Quere, IEEE Electron Device Lett. 5, 175 (2017).

I.B. Renowa, S.L. Selvaraj, and T. Egawa, IEEE Electron Device Lett. (2011). https://doi.org/10.1109/LED.2011.2166052

M. Borga, M. Meneghini, S. Stoffels, M.V. Hove, M. Zhao, X. Li, S. Decoutere, E. Zanoni, and M. Meneghesso, Microelectron. Reliab. (2011). https://doi.org/10.1016/j.microrel.2018.06.036

A.S.A. Fletcher, D. Nirmal, J. Ajayan, and L. Arivazhagan, Silicon 13, 1591–1598 (2021). https://doi.org/10.1007/s12633-020-00549-4

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bhat, A.M., Shafi, N., Poonia, R. et al. Design and Analysis of a Field Plate Engineered High Electron Mobility Transistor for Enhanced Performance. J. Electron. Mater. 51, 3773–3781 (2022). https://doi.org/10.1007/s11664-022-09646-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-022-09646-z