Abstract

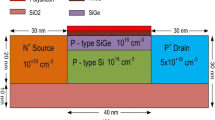

This work reports a simulation study of an InSb/Si heterojunction-based tunnelling field effect transistor (TFET) by employing drain doping engineering with an asymmetric gate structure to achieve high ON current and low subthreshold swing (SS). Incorporation of an n+ pocket towards the drain and InSb towards the source has improved the ION/IOFF ratio significantly. The ground plane in the proposed structure reduces the electric field towards the drain that increases the effective channel length for short-channel devices. A calibrated exhaustive TCAD study is deployed to analyse the device physics for the proposed structure. The values of the ION/IOFF ratio and average subthreshold swing (SSAvg) were found to be ~ 1012 and 29 mV/decade, respectively. Reduced average subthreshold swing and lower OFF current (IOFF) with suppressed ambipolar behaviour in the proposed TFET structure ensures its suitability for high-performance, ultralow-power applications.

Similar content being viewed by others

References

A. M. Ionescu, Energy efficient computing and sensing in the Zettabyte era: From silicon to the cloud. 2017 IEEE International Electron Devices Meeting (IEDM) 1 (2017).

A. C. Seabaugh and Q. Zhang, Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE, 98, 2095 (2010).

W. Young Choi, B.-G. Park, J. Duk Lee, and T.-J. King-Liu, Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28, 743 (2007).

K. Boucart, and A.M. Ionescu, Length scaling of the double gate tunnel FET with a high-k gate dielectric. Solid-State Electron. 51, 1500 (2007).

S. Kumar, E. Goel, K. Singh, B. Singh, M. Kumar, and S. Jit, A compact 2-D analytical model for electrical characteristics of double-gate tunnel field-effect transistors with a SiO2/High-$\kappa $ stacked gate-oxide structure. IEEE Trans. Electron Devices 63, 3291 (2016).

M. Venkatesh, M. Suguna, and N.B. Balamurugan, Subthreshold performance analysis of germanium source dual halo dual dielectric triple material surrounding gate tunnel field effect transistor for ultra low power applications. J. Electron. Mater. 48, 6724 (2019).

U.E. Avci, D.H. Morris, and I.A. Young, Tunnel field-effect transistors: Prospects and challenges. IEEE J. Electron Devices Soc. 3, 88 (2015).

J. Appenzeller, Y.M. Lin, J. Knoch, Z. Chen, and P. Avouris, Comparing carbon nanotube transistors-the ideal choice: a novel tunneling device design. IEEE Trans. Electron Devices 52, 2568 (2005).

L. Xu, C. Qiu, L.M. Peng, and Z. Zhang, Suppression of leakage current in carbon nanotube field-effect transistors. Nano Res. 14, 976 (2021).

A. Padilla, C. W. Yeung, C. Shin, C. Hu, and T.J.K. Liu, Feedback FET: A novel transistor exhibiting steep switching behavior at low bias voltages. 2008 IEEE International Electron Devices Meeting , 1. (2008).

S. Thomas, Guiding the design of negative-capacitance FETs. Nature Electronics 3, 72 (2020).

M.A. Alam, M. Si, and P.D. Ye, A critical review of recent progress on negative capacitance field-effect transistors. (2019).

M. Kim, Y. Jeon, Y. Kim, and S. Kim, Impact-ionization and tunneling FET characteristics of dual-functional devices with partially covered intrinsic regions. IEEE Trans. Nanotechnol. 14, 633 (2015).

K. Boucart, and A.M. Ionescu, Double-gate tunnel FET with high-$\kappa $ gate dielectric. IEEE Trans. Electron Devices 54, 1725 (2007).

The International Technology Roadmap for Semiconductors (ITRS) (2012).

P.K. Singh, K. Baral, S. Kumar, M.R. Tripathy, A.K. Singh, R.K. Upadhyay, and S. Jit, Analytical drain current model for source pocket engineered stacked oxide SiO2/HfO2 cylindrical gate TFETs. SILICON 13, 1731 (2021).

R. Jhaveri, V. Nagavarapu, and J.C. Woo, Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans. Electron Devices 58, 80 (2010).

W.Y. Choi, and W. Lee, Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans. Electron Devices 57, 2317 (2010).

G. Lee, and W.Y. Choi, Low-power circuit applicability of hetero-gate-dielectric tunneling field-effect transistors (HG TFETs). IEICE Trans. Electron. 95, 910 (2012).

K.N. Priyadarshani, S. Singh, and A. Naugarhiya, RF & linearity distortion sensitivity analysis of DMG-DG-Ge pocket TFET with hetero dielectric. Microelectron. J. 108, 104973 (2021).

K.N. Priyadarshani, S. Singh, and K. Singh, Analog/RF performance estimation of a dopingless symmetric tunnel field effect transistor. Journal of Electronic Materials, 1 (2021).

E. Lind, E. Memišević, A.W. Dey, and L. Wernersson, E III-V heterostructure nanowire tunnel FETs. IEEE J. Electron Devices Soc. 3, 96 (2015).

M.R. Tripathy, A.K. Singh, K. Baral, P.K. Singh, and S. Jit, III-V/Si staggered heterojunction based source-pocket engineered vertical TFETs for low power applications. Superlattices Microstruct. 142, 106494 (2020).

J.S. Jang, and W.Y. Choi, Ambipolarity factor of tunneling field-effect transistors (TFETs). JSTS J. Semicond. Technol. Sci. 11, 272 (2011).

M.G. Pala, D. Esseni, and F. Conzatti, Impact of interface traps on the IV curves of InAs tunnel-FETs and MOSFETs: A full quantum study. In 2012 International Electron Devices Meeting 6 (2012).

P. Kumari, A. Raj, K.N. Priyadarshani, and S. Singh, Impact of temperature and interface trapped charges variation on the Analog/RF and linearity of vertically extended drain double gate Si0.5Ge0.5 source tunnel FET. Microelectron. J. 113, 105 (2021).

S. Ahish, D. Sharma, M.H. Vasantha, and Y.B.N. Kumar, Design and analysis of novel InSb/Si Heterojunction double gate tunnel field effect transistor. In 2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI) 105 (2016).

M. Luisier, and G. Klimeck, Atomistic full-band design study of InAs band-to-band tunneling field-effect transistors. IEEE Electron Device Lett. 30, 602 (2009).

S. Garg, and S. Saurabh, Suppression of ambipolar current in tunnel FETs using drain-pocket: Proposal and analysis. Superlattices Microstruct. 113, 261 (2018).

M.J. Kumar, and M. Siva, The ground plane in buried oxide for controlling short-channel effects in nanoscale SOI MOSFETs. IEEE Trans. Electron Devices 55, 1554 (2008).

K.T. Lam, G. Seol, and J. Guo, Operating principles of vertical transistors based on monolayer two-dimensional semiconductor heterojunctions. Appl. Phys. Lett. 105, 013112 (2014).

G.A. Nemnes, U. Wulf, and P.N. Racec, Nonlinear I-V characteristics of nanotransistors in the Landauer-Büttiker formalism. J. Appl. Phys. 98, 084308 (2005).

W. Hsu, J. Mantey, L.F. Register, and S.K. Banerjee, Strained-Si/strained-Ge type-II staggered heterojunction gate-normal-tunneling field-effect transistor. Appl. Phys. Lett. 103, 093501 (2013).

J. Knoch, S. Mantl, and J. Appenzeller, Impact of the dimensionality on the performance of tunneling FETs: Bulk versus one-dimensional devices. Solid-State Electron. 51, 572 (2007).

E.O. Kane, Theory of tunneling. J. Appl. Phys. 32, 83 (1961).

"ATLAS User's Manual A 2D-3D Numerical Device Simulator", [online].

K. Boucart, and A.M. Ionescu, Threshold voltage in tunnel FETs: physical definition, extraction, scaling and impact on IC design. ESSDERC 2007-37th European Solid State Device Research Conference 299 (2007).

S. Ramaswamy, and M.J. Kumar, Double gate symmetric tunnel FET: investigation and analysis. IET Circuits Devices Syst. 11, 365 (2017).

H. Lee, S. Park, Y. Lee, H. Nam, and C. Shin, Random variation analysis and variation-aware design of symmetric tunnel field-effect transistor. IEEE Trans. Electron Devices 62, 1778 (2014).

Acknowledgments

The authors are thankful to the Department of Electronics and Communication Engineering, National Institute of Technology Patna, India, for extending the Silvaco simulation facility to complete this work.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflicts of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Swain, S.K., Malviya, N., Singh, S. et al. InSb/Si Heterojunction-Based Tunnelling Field-Effect Transistor with Enhanced Drive Current and Steep Switching. J. Electron. Mater. 51, 704–711 (2022). https://doi.org/10.1007/s11664-021-09325-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-021-09325-5