Abstract

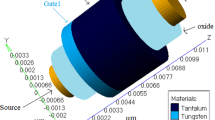

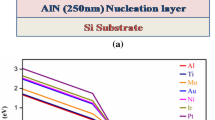

This paper presents the analytical approximation of device physics of heterojunction based double gate (DG) Tunnel field effect transistors (TFETs) in terms of potential distribution, electron density and electron barrier tunneling. In order to improve the device performance with respect to ON current (ION), DG TFET with gate-drain overlap is developed. An asymmetric gate oxide is introduced in the gate - drain overlap region and is compared to DG TFET. The device physics and its performance characteristics are studied by using various materials, such as Si, SiGe, InAs and GaSb. The simulated results are validated against the model values. DG TFETs with gate-drain overlap offers higher tunneling probability compared to DG TFETs. Also GaSb/Si based DG TFETs with gate-drain overlap shows good performance improvement by offering higher tunneling probability which in turn offers a higher ION of 1.15 mA/μm.

Similar content being viewed by others

Data Availability

Not Applicable.

References

McGuire F, Cheng FZ, Price K, Franklin A (2016) Sub-60 mV/decade switching in 2D negative capacitance field-effect transistors with integrated ferroelectric polymer. Appl Phys Lett 109:093101

Liu T, Jeon J, Nathanael R, Kam H, Pott V, Alon E (2011) Prospects for MEM logic switch technology. In 2010 IEEE International Electron Devices Meeting (IEDM '10): 424–427

Sarkar D, Singh N, Banerjee K (2010) A novel enhanced electric-field impact-ionization MOS transistor. IEEE Electron Device Lett 31:1175–1177

Salvatore, G., Bouvet, D., Ionescu, A. M. (2009) Demonstration of subthrehold swing smaller than 60mV/decade in Fe-FET with P(VDF-TrFE)/SiO2 gate stack. In 2008 IEEE International Electron Devices Meeting : 479–481

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479:329–337

Seabaugh A, Zhan Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. In 2010 ProSceWedings of the IEEE 98:2095–2110

Trivedi AR, Carlo S, Mukhopadhyay S (2013) Exploring tunnel-FET for ultra low power analog applications: A case study on operational transconductance amplifier. In 2013 Proceedings of 50th Annual Design Automation Conference: 109

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans Electron Devices 54:1725–1733

Zhang L, He J, Chan M (2013) A compact model for double-gate tunneling field-effect-transistors and its implications on circuit behaviors. In 2012 International Electron Devices Meeting (IEDM) 6.8.1–6.8.4

Vishnoi R, Jagadesh Kumar M (2014) A pseudo-2D analytical model of dual material gate all-around nanowire tunneling FET. IEEE Trans Electron Devices 61:2264–2270

Dash S, Mishra GP (2015) A 2D analytical cylindrical gate tunnel FET (CG-TFET) model: impact of shortest tunneling distance. Adv Nat Sci Nanosci Nanotechnol 6:035005

Xu H, Dai Y (2017) Two-dimensional analytical model of double-gate tunnel FETs with interface trapped charges including effects of channel mobile charge carriers. J Semiconduct 38:024004–1–024004-8

Mahajan A, Dash DK, Banerjee P, Sarkar SK (2018) Analytical modeling of triple-metal hetero-dielectric DG SON TFET. J Mater Eng Perform 27:2693–2700

Yunhe G, Li Z, Zhang W, Zhang Y, Liang F (2018) A full-range analytical current model for heterojunction TFET with dual material gate. IEEE Trans Electron Devices 65:5213–5217

Yunhe G, Li Z, Carrillo-nuñez H, Zhang Y, Georgiev VP, Asenov A, Liang F (2019) An accurate analytical model for tunnel FET output characteristics. IEEE Electron Device Lett 40:1001–1004

Sentaurus Device User Guide (2014) J-2014.09, in Synopsys Inc. Mountain View, CA, (Mountain View, CA, USA

Madan J, Shekhar S, Chaujar R (2017) Source material assessment of heterojunction DG-TFET for improved analog performance. In 2017 international conference on microelectronic devices, Circuits and Systems (ICMDCS)

Guan Y, Li Z, Zhang W, Zhang Y (2017) An accurate analytical current model of double-gate heterojunction tunneling FET. IEEE Trans Electron Devices 64:938–944

Elahi M, Ahmed K, Md Shofiqul Islam (2013) An improved analytical model of current in tunnel field effect transistor In 2012 7th International Conference on Electrical and Computer Engineering

Sze SM (1981) Physics of Semiconductor Devices, 2nd edn. (John Wiley & Sons, Inc)

Gupta S, Baidya A, Baishya S (2012) Simulation and analysis of gate engineered triple metal double gate (TM-DG) MOSFET for diminished short channel effects. Int J Advanced Sci Technol 38:15–24

Author information

Authors and Affiliations

Contributions

S. Poorvasha and B. Lakshmi have contributed to the design and implementation of the research, to the analysis of the results and to the writing of the manuscript.

Corresponding author

Ethics declarations

This study was approved by the university research ethics committee. All procedures performed in this study follow the ethical standards of the institutional and research committee.

Conflict of Interest

The authors declare that there is no conflict of interest.

Consent to Participate

Not Applicable.

Consent for Publication

Yes

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Poorvasha, S., Lakshmi, B. Investigation of the Device Electrical Parameters for Homo and Hetero Junction Based TFETs. Silicon 14, 1479–1488 (2022). https://doi.org/10.1007/s12633-020-00934-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00934-z