Abstract

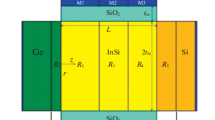

In this paper, analytical modeling of center channel potential has been performed for graded-channel gate-all-around (GC-GAA) junctionless field-effect transistor (JLFET). The three-dimensional (3D) Poisson’s equation has been solved to discover the center channel potential utilizing the parabolic approximation equation with excellent boundary conditions. The minimum center channel potential has been adopted to calculate the subthreshold current by the drift-diffusion method. The effect of high temperature and doping concentration on the center potential and subthreshold current has been investigated, and the results have been verified. The validity of the model has been verified using the ATLAS TCAD device simulator. The results reveal that the GC-GAA JLFET reduces the OFF-state leakage current with a high-graded abrupt junction inside the channel region. Hence, this finds many applications in low-power, high-speed, and high-density circuits.

Similar content being viewed by others

Data Availability

The data and material are available within the manuscript.

References

A. Chaudhry, and M.J. Kumar, IEEE Trans. Dev. Mater. Rel. 4, 99 (2004).

Y. Taur, and T.H. Ning, Fundamentals of Modern VLSI Devices (New York: Cambridge University Press, 2013).

B.G. Streetman, and S.K. Banerjee, Solid State Electronic Devices, 7th ed., (London: Pearson Education, 2016).

G. Leung, A. Pan, and C.O. Chui, IEEE Trans. Electron Dev. 62, 3208 (2015).

M.H. Han, C.Y. Chang, Y.R. Jhan, J.J. Wu, H.B. Chen, Y.C. Cheng, and Y.C. Wu, IEEE Electron Dev. Lett. 34, 157 (2013).

J.P. Colinge, C.W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B.O. Neill, A. Blake, M. White, A.M. Kelleher, B.M. Carthy, and R. Murphy, Nat. Nanotechnol. 5, 225 (2010).

S.R. Abhinav, Microelectron. J. 64, 60 (2017).

S. Sahay, and M.J. Kumar, Junctionless Field-Effect Transistors: Design, Modeling, and Simulation (Hoboken: Wiley-IEEE Press, 2009).

J.P. Colinge, C.W. Lee, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, A. Kranti, and R. Yu, Semiconductor-On-Insulator Materials for Nanoelectronics Applications (Berlin: Springer, 2011).

G. Groeseneken, J.P. Colinge, H.E. Maes, J.C. Alderman, and S. Holt, IEEE Electron Dev. Lett. 11, 329 (1990).

K. Akarvardar, A. Mercha, E. Simoen, V. Subramanian, C. Claeys, P. Gentil, and S. Cristoloveanu, Microelectron. Reliab. 47, 2065 (2007).

ATLAS User’s Manual, 3-D Device Simulator Software, Silvaco. Inc. (2016).

Abhinav, M. Srivastav, A. Kumar, and S. Rai, 4th International Conference on SPIN (2017), p. 256.

F.S. Shoucair, W. Hwang, and P. Jain, IEEE Trans. Compon. Hybrids Manuf. Technol. 7, 146 (1984).

F.S. Shoucair, W. Hwang, and P. Jain, Microelectron. Reliab. 24, 465 (1984).

R. Gautam, M. Saxena, R.S. Gupta, and M. Gupta, Microelectron. Reliab. 54, 37 (2014).

H. Cheng, S. Uno, and K. Nakazato, J. Comput. Electron. 14, 321 (2015).

A. Goel, S. Rewari, S. Verma, and R.S. Gupta, Appl. Phys. A 126, 346 (2020).

K. Kanda, K. Nose, H. Kawaguchi, and T. Sakurai, IEEE J. Solid-State Circ. 36, 1559 (2001).

Funding

This work did not receive financial support.

Author information

Authors and Affiliations

Contributions

All authors have made substantial contributions to the conception and design, or acquisition of data, or analysis and interpretation of data; have been involved in drafting the manuscript or revising it critically for important intellectual content; and have given final approval of the version to be published. Each author has participated sufficiently in the work to take public responsibility for appropriate portions of the content. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interest regarding the publication of this paper.

Ethical approval

The authors declare that all procedures followed were in accordance with the ethical standards.

Consent to Participate

All the authors declare their consent to participate in this research article.

Consent for Publication

All the authors declare their consent for publication of the article on acceptance.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, V., Kumar, N., Awasthi, H. et al. Temperature-Dependent Analytical Modeling of Graded-Channel Gate-All-Around (GC-GAA) Junctionless Field-Effect Transistors (JLFETs). J. Electron. Mater. 50, 3686–3691 (2021). https://doi.org/10.1007/s11664-021-08913-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-021-08913-9