Abstract

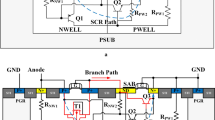

This work presents the design of a novel static-triggered power-rail electrostatic discharge (ESD) clamp circuit. The superior transient-noise immunity of the static ESD detection mechanism over the transient one is firstly discussed. Based on the discussion, a novel power-rail ESD clamp circuit utilizing the static ESD detection mechanism is proposed. By skillfully incorporating a thyristor delay stage into the trigger circuit (TC), the proposed circuit achieves the best ESD-conduction behavior while consuming the lowest leakage current (I leak) at the normal bias voltage among all investigated circuits in this work. In addition, the proposed circuit achieves an excellent false-triggering immunity against fast power-up pulses. All investigated circuits are fabricated in a 65-nm CMOS process. Performance superiorities of the proposed circuit are fully verified by both simulation and test results. Moreover, the proposed circuit offers an efficient on-chip ESD protection scheme considering the worst discharge case in the utilized process.

创新点

基于静态探测机制相对于瞬态探测机制在瞬态噪声性能上的优势, 本文提出了一种新型的静态触发型电源钳位ESD保护电路。通过有效的触发电路设计, 本文提出的新型保护电路能在ESD情况下相对于传统静态触发电路实现最好的泄放性能, 同时, 在正常操作情况下消耗最小的泄漏电流。本文提出的电路在65纳米CMOS工艺下得到了验证, 测试结果表明:本文提出的电路对与ESD事件一样快速的瞬态噪声具有免疫力, 同时, 本文提出的电路能为65纳米的CMOS工艺提供有效的片上ESD防护方案。

Similar content being viewed by others

References

Amerasekera A, Duvvury C, Anderson W, et al. ESD in Silicon Integrated Circuits. 2nd ed. Chichester: John Wiley & Sons, Ltd, 2002

Ker M D. Whole-chip ESD protection design with efficient VDD-to-VSS ESD clamp circuits for submicron CMOS VLSI. IEEE Trans Electron Devices, 1999, 46: 173–183

Smith J, Cline R, Boselli G. A MOSFET power supply clamp with feedback enhanced triggering for ESD protection in advanced CMOS technologies. In: Proceedings of Electrical Overstress/Electrostatic Discharge Symposium, Las Vegas, 2003. 1–9

Sarbishaei H, Semenov O. A transient power supply ESD clamp with CMOS thyristor delay element. In: Proceedings of Electrical Overstress/Electrostatic Discharge Symposium, Anaheim, 2007. 395–402

Ker M D, Yen C C. Investigation and design of on-chip power-rail ESD clamp circuits without suffering latchup-like failure during system-level ESD test. IEEE J Solid-State Circ, 2008, 43: 2533–2545

Wang Y, Zhang L, Cao J, et al. Research on electrostatic discharge characteristics of tunnel field effect transistors. Acta Phys Sin, 2014, 63: 178501

Li J J, Gauthier R, Mitra S, et al. Design and characterization of a multi-RC-triggered MOSFET-based power clamp for on-chip ESD protection. In: Proceedings of Electrical Overstress/Electrostatic Discharge Symposium, Anaheim, 2006. 179–185

Zhang L, Wang Y, Lu G, et al. A novel diode string triggered gated-PiN junction device for electrostatic discharge protection in 65 nm CMOS technology. Chin Phys B, 2015, 24: 000001

Liu H X, Yang Z N, Li L, et al. A novel ESD power supply clamp circuit with double pull-down paths. Sci China Inf Sci, 2013, 56: 102401

Lu G Y, Wang Y, Cao J, et al. Design and verification of a novel multi-RC-triggering power clamp circuit for on-chip ESD protection. In: Proceedings of Electrical Overstress/Electrostatic Discharge Symposium, Las Vegas, 2013. 56–62

Altolaguirre F A, Ker M D. Aea-efficient ESD clamp circuit with capacitance-boosting technique to minimize standby leakage current. IEEE Trans Device Mater Reliab, 2015, 15: 156–162

Wang Y, Lu G Y, Guo H B, et al. Area-efficient transient power-rail ESD clamp circuit with mis-triggering immunity in a 65-nm CMOS process. Sci China Inf Sci, in press, 2016. doi:10.1007/s11432-015-5398-3

Young W, Croft G. Schmitt Triggered-Configured ESD Protection Circuit. U.S. Patent 5978192. 1999

Ker M D, Chen T, Wang T, et al. On-chip ESD protection design by using polysilicon diodes in CMOS process. IEEE J Solid-State Circ, 2001, 36: 676–686

Altolaguire F A, Ker M D. Power-rail ESD clamp circuit with diode-string ESD detection to overcome the gate leakage current in a 40-nm CMOS process. IEEE Trans Electron Devices, 2013, 60: 3500–3507

Maloney T, Khurana N. Transmission line pulsing techniques for circuit modeling of ESD phenomena. In: Proceedings of Electrical Overstress/Electrostatic Discharge Symposium, Minneapolis, 1985. 49–54

Industry Council on ESD Target Levels. White Paper 1: a case for lowering component level HBM/MM ESD specifications and requirements. 2nd ed. 2010

Lu G Y, Wang Y, Zhang L Z, et al. Investigation on the layout strategy of ggNMOS ESD protection devices for uniform conduction behavior and optimal width scaling. Sci China Inf Sci, 2015, 58: 042402

Industry Council on ESD Target Levels. White paper 3—system level ESD, part I: Common misconceptions and recommended basic approaches. 1st ed. 2010

JEDEC Standard. IC latch-up test. JESD78D. http://www.jedec.org. 2011

Barth electronics. BARTH model 4002 TLP+ TMspecifications. http://barthelectronics.com

Ker M D, Hsu S. Transient-Induced Latchup in CMOS Integrated Circuits. New York: Wiley, 2009

JEDEC Standard. Electrostatic discharge (ESD) sensitivity testing, human body model (HBM). JESD22-A114F. http://www.jedec.org. 2007

Thermo Fisher Scientific. Key Tek zapmaster series 7: performance specifications. http://www.thermofisher.com

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lu, G., Wang, Y., Zhang, L. et al. Design of a novel static-triggered power-rail ESD clamp circuit in a 65-nm CMOS process. Sci. China Inf. Sci. 59, 122401 (2016). https://doi.org/10.1007/s11432-015-5455-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11432-015-5455-y

Keywords

- electrostatic discharge (ESD)

- power-rail ESD clamp circuit

- detection mechanism

- transient-noise immunity

- false triggering

- transmission line pulsing (TLP) test