Abstract

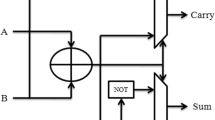

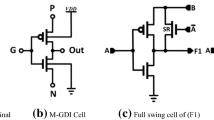

Adder is the critical component in any arithmetic application. Significant efforts have been made to improve their architecture. This paper introduces two novel symmetric designs for energy-efficient full adder (FA) employing Gate-Diffusion Input (GDI) logic. Our primary focus is achieving low-power operation with minimized area while ensuring full-voltage swing capability. The first design, referred to as AEG-FA, employs a novel strategy utilizing inverted and non-inverted Carry-inputs to produce complementary Carry-out and Sum outputs, thus achieving the desired performance characteristics. These techniques are then adapted in various combinations to construct adder architectures of higher bit widths, offering greater design flexibility across a spectrum of applications and reducing overall design complexity. In contrast, the second design, PEG-FA, follows a more conventional approach to minimize critical path delay and minimize switching activity within the GDI circuitry. This design prioritizes low-power consumption and high-speed operation while maintaining full voltage swing. Previous literature has noted challenges such as low-swing and high noise levels when operating adders at low supply voltages. Our proposed designs successfully address these issues, ensuring reliable operation even at lower voltages while maintaining signal integrity and driving capability. To assess the performance of the proposed FAs, we integrated them into an 8-bit ripple carry adder and optimized it for energy efficiency using 45 nm CMOS process technology. Comparative analysis with standard FA cells demonstrates improvements across all metrics. At the architecture level, the proposed adder provides power saving by 12.8%, 14.8%, and 11.4% than CMOS, hybrid, and other GDI logic, respectively, while exhibiting a 55% reduction in area.

Similar content being viewed by others

Data Availability

No.

Code Availability

No.

References

Foroutan, V., Taheri, M., Navi, K., & Mazreah, A. A. (2014). Design of two low-power full adder cells using GDI structure and hybrid CMOS logic style. Integration, 47(1), 48–61.

Moaiyeri, M. H., Faghih Mirzaee, R., Navi, K., Nikoubin, T., & Kavehei, O. (2010). Novel direct designs for 3-input XOR function for low-power and high-speed applications. International Journal of Electronics, 97(6), 647–662.

Garg, B. (2021). Energy efficient gaussian filtering for multimedia applications using novel approximate adders. Sādhanā, 46(4), 237.

Garg, B. (2021). Energy-efficient gaussian filter design using novel low-complexity accuracy reconfigurable reverse carry adder. National Academy Science Letters, 44(5), 409–414.

Garg, B., & Sharma, G. (2019). A process-tolerant low-power adder architecture for image processing applications. Turkish Journal of Electrical Engineering and Computer Sciences, 27(3), 1839–1854.

Morgenshtein, A., Yuzhaninov, V., Kovshilovsky, A., & Fish, A. (2014). Full-swing gate diffusion input logic-case-study of low-power CLA adder design. Integration, 47(1), 62–70.

Kumar, T. S., Rao, I. R. S. N., Vinod, Y. S., Harika, P., Satyanarayana, B., & Pravin, A. (2023). Area efficient and ultra low power full adder design based on GDI technique for computing systems. In International conference on cognitive computing and cyber physical systems (pp. 63–75). Springer.

Swathi, G., & Venkata Ganesh Kona, S. (2023). Electronic device performance enhancement through low-power, high-speed IC design with GDI-based carry look-ahead adders. Turkish Journal of Computer and Mathematics Education (TURCOMAT), 14(03), 1013–1020.

Sharma, P., Sutradhar, J., Akashe, S., & Sharma, S. (2023). Design of multi-bit full adder using low power m-GDI technique. In 2023 IEEE world conference on applied intelligence and computing (AIC) (pp. 834–838). IEEE.

Shiri, N., Sadeghi, A., & Rafiee, M. (2023). High-efficient and error-resilient gate diffusion input-based approximate full adders for complex multistage rapid structures. Computers and Electrical Engineering, 109, 108776.

Deymad, S. F., Shiri, N., & Pesaran, F. (2023). High-efficient reversible full adder realized by dynamic threshold-based gate diffusion input logics. Microelectronics Journal, 142, 105972.

Roodbali, K. M., Abiri, E., & Hassanli, K. (2023). Highly efficient low-area gate-diffusion-input-based approximate full adders for image processing computing. The Journal of Supercomputing, 80(6), 8129–8155.

Morgenshtein, A., Shwartz, I., & Fish, A. (2010). Gate diffusion input (GDI) logic in standard CMOS nanoscale process. In 2010 IEEE 26-th Convention of Electrical and Electronics Engineers in Israel (pp. 000 776–000 780). IEEE.

Hasan, M., Zaman, H. U., Hossain, M., Biswas, P., & Islam, S. (2020). Gate diffusion input technique based full swing and scalable 1-bit hybrid full adder for high performance applications. Engineering Science and Technology, an International Journal, 23(6), 1364–1373.

Sakthivel, B., & Padma, A. (2020). Area and delay efficient GDI based accuracy configurable adder design. Microprocessors and Microsystems, 73, 102958.

Rabaey, J. M., Chandrakasan, A. P., & Nikolić, B. (2003). Digital integrated circuits: A design perspective (Vol. 7). Upper Saddle River: Pearson Education.

Chang, C. H., Gu, J. M., & Zhang, M. (2005). A review of 0.18-\(\mu \)m full adder performances for tree.

Jiang, Y., Al-Sheraidah, A., Wang, Y., Sha, E., & Chung, J.-G. (2004). A novel multiplexer-based low-power full adder. IEEE Transactions on Circuits and Systems II: Express Briefs, 51(7), 345–348.

Morgenshtein, A., Fish, A., & Wagner, I. A. (2002). Gate-diffusion input (GDI): A power-efficient method for digital combinatorial circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 10(5), 566–581.

Purohit, S., & Margala, M. (2011). Investigating the impact of logic and circuit implementation on full adder performance. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 20(7), 1327–1331.

Hassoune, I., Flandre, D., O’Connor, I., & Legat, J.-D. (2008). ULPFA: A new efficient design of a power-aware full adder. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(8), 2066–2074.

Shoba, M., & Nakkeeran, R. (2016). GDI based full adders for energy efficient arithmetic applications. Engineering Science and Technology, an International Journal, 19(1), 485–496.

Sharma, A., & Mehra, R. (2013). Area and power efficient CMOS adder design by hybridizing PTL and GDI technique. International Journal of Computer Applications, 66(4), 15–22.

Uma, R., & Dhavachelvan, P. (2012). Modified gate diffusion input technique: A new technique for enhancing performance in full adder circuits. Procedia Technology, 6, 74–81.

Mewada, M., & Zaveri, M. (2016). An input test pattern for characterization of a full-adder and n-bit ripple carry adder. In 2016 International Conference on Advances in Computing, Communications and Informatics (ICACCI) (pp. 250–255). IEEE.

Funding

No funding.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Aggarwal, P., Garg, B. Energy Efficient Full Swing GDI Based Adder Architecture for Arithmetic Applications. Wireless Pers Commun 135, 1663–1678 (2024). https://doi.org/10.1007/s11277-024-11140-0

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-024-11140-0