Abstract

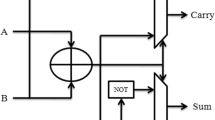

In this work, an efficient full-swing (FS)-gate diffusion input (GDI) logic style is used for implementing full adder (FA) and arithmetic logic unit (ALU) circuits. The performance of the ALU in delay time, power consumption, and area terms is strongly dependent on the performance efficiency of the FA circuits utilized in its construction. In this research paper, multi-efficient power and high-speed ALU circuits are proposed with outputs in full-swing form and improved area. The proposed circuit is evaluated and tested using the Cadence Virtuoso simulation package in the 65 nm CMOS process. The proposed ALUs reduce power consumption by 20.01% and 4% compared with the ALU implemented by the traditional CMOS technique and GDI-based unit, respectively. Also, four ALU designs utilizing four efficient FA circuits are presented. The proposed ALUs provide more than 74.4–23.3% improvement in the power-delay product (PDP) term compared with existing circuits. The simulation experiments reveal that with the proposed ALUs, the circuits achieve superior performance compared with previous and existing ALU designs, and the power efficiency of these units improves in a range of 18.7–20.1% over the CMOS-based units. Also, the various technology nodes and their impact are considered in this paper.

Similar content being viewed by others

Data Availability

The data associated with the paper and supporting the findings of this research work are available from the corresponding author upon reasonable request.

References

A.A. Abouelfadl, M.A.M. El-Bendary, F. Shawki, Enhancing transmission over wireless image sensor networks based on ZigBee network. Life Sci. J. 11(8), 342–354 (2011)

M. A. Ahmed, M. A. Mohamed El-Bendary, F. Z. Amer, S. M. Singy, “Delay Optimization of 4-Bit ALU Designed in FS-GDI Technique, in 2019 International Conference on Innovative Trends in Computer Engineering (ITCE‟2019), Aswan, Egypt, pp. 2–4 (2019)

O. A. AlBadry, M. A. M. El-Bendary, F. Z. Amer, S. M. Singy, Design of Efficient and low power 4-bit Multiplier based on Full Swing GDI techniqe, in 2019 International Conference on Innovative Trends in Computer Engineering (ITCE‟2019), vol. 1. no. 1, pp. 2–4 (2019)

M. Amini-Valashani, M. Ayat, S. Mirzakuchaki, Design and analysis of a novel low-power and energy-efficient 18T hybrid full adder. Microelectron. J. 74, 49–59 (2018)

M. Anis, M. Allam, M. Elmasry, Impact of technology scaling on CMOS logic styles. IEEE Trans. Circuits Syst. II Analog Digit Signal Process. 49(8), 577–588 (2002)

C. Arunabala, C. Jyothirmayi, D. N. S. V Sreeja, T. S. Burra, H. R. Udumula, I. R. Anusha Devi, Design of a 4 bit arithmetic and logical unit with low power and high speed, in International Journal of Innovative Technology and Exploring Engineering (IJITEE), vol. 10, no. 5, pp. 87–92 (2021)

P. Bhattacharyya, B. Kundu, S. Ghosh, V. Kumar, A. Dandapat, Performance analysis of a low-power high-speed hybrid 1-bit full adder circuit. IEEE Trans. Very Large Scale Integr. Syst. 23(10), 2001–2008 (2015)

T. Bhagyalaxmi, S. Rajendar, S. Srinivas, Power-aware alternative adder cell structure using swing restored complementary pass transistor logic at 45 nm technology, in Procedia Materials Science, 2015, vol. 10, pp. 789–792 (2014)

S. Bhojane, P. Chaudhari, M. More, D.S. Patil, A review on designing of 4 bit ALU using GDI technique at 45 nm, 32 nm, 22 nm. Int. Res. J. Eng. Technol. 03(10), 1238–1242 (2016)

A. Chauhan, K. K. Saini, R. Domah, Implementation of high performance 4-Bit ALU using dual mode pass transistor logic, in Computer Science, 2021 International Conference on Intelligent Technologies (CONIT), (2021)

C. C. Wang, N. Sulistiyanto, T. Y. Tsai, Y. H. Chen, Multifunctional in-memory computation architecture using single-ended disturb-Free 6T SRAM, in Advances in Electronics Engineering (Springer, 2020), pp 49–57

V. Dubey, R. Sairam, An arithmetic and logic unit optimized for area and power, in International Conference on Advanced Computing and Communication Technologies, ACCT, pp. 330–334 (2014)

A. Mohsen, M. El-Bendary, A. El-Azm, Complexity considerations: efficient image transmission over mobile communications channels. Multimed. Tools Appl. 78(12), 16633–16664 (2019)

M. A. M. El-Bendary, A. Haggag, Investigating performance analysis of a novel low-power efficient area carry-look ahead adder, in IEEE 2021 International Mobile, Intelligent, and Ubiquitous Computing, Conference (MIUCC), pp. 364–369 (2021)

M.A.M. El-Bendary, H. Kasban, A. Haggag, M.A.R. El-Tokhy, Investigating of nodes and personal authentications utilizing multimodal biometrics for medical application of WBANs security. Multimed. Tools Appl. 79(33), 24507–24535 (2020)

M. A. M. El-Bendary, Lower complexity of secured WSN networks, in Developing Security Tools of WSN and WBAN Networks Applications, pp. 97–151 (2015)

M. Fadaei, Designing ALU using GDI method, in International Journal of Reconfigurable and Embedded Systems (IJRES) vol. 8, no. 3, pp. 151–161 (2019)

M. Hasan, M.J. Hossein, M. Hossain, H.U. Zaman, S. Islam, Design of a scalable low-power 1-bit hybrid full adder for fast computation. IEEE Trans. Circuits Syst. II Express Briefs 67(8), 1464–1468 (2020)

M. Hasan, H.U. Zaman, M. Hossain, P. Biswas, S. Islam, Gate Diffusion Input technique based full swing and scalable 1-bit hybrid full adder for high performance applications. Eng. Sci. Technol. Int. J. 23(6), 1364–1373 (2020)

M. Hasan, U. K. Saha, A. Sorwar, M. A. Z. Dipto, M. S. Hossain, H. U. Zaman, A novel hybrid full adder based on gate diffusion input technique, transmission gate and static CMOS logic, in 2019 10th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Kanpur, India, pp. 1–6 (2019)

J. Kandpal, A. Tomar, M. Agarwal, K. K. Sharma, High-speed hybrid-logic full adder using high-performance 10-T XOR-XNOR cell, in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 6, pp. 1413–1422 (2020) https://ieeexplore.ieee.org/author/37087500561

E. J. Kishore, R. Manoj, P. R. Devarmani, Y. G. P. Kumar, M. Z. Kurian, Gate-Diffusion input based linear feedback shift register: a review, in IEEE, 2019 International Conference on Smart Systems and Inventive Technology (ICSSIT), https://doi.org/10.1109/ICSSIT46314.2019.8987975 (2019)

P. Kumar, R.K. Sharma, An energy efficient logic approach to implement CMOS full adder. J. Circuits Syst. Comput. 26(05), 175–184 (2017)

M. Kumar, M.A. Hussain, L.L.K. Singh, Design of a low power high speed ALU in 45 nm using GDI technique and its performance comparison. Commun. Comput. Inf. Sci. 142, 458–463 (2011)

F. Moradi, D. T. Wisland, H. Mahmoodi, S. Aunet, T. V Cao, A. Peiravi, Low power full adder topologies, in 2009 IEEE International Symposium on Circuits and Systems, pp. 3158–3161 (2009)

A. Morgenshtein, A. Fish, A. Wagner, Gate-diffusion input (GDI)-a novel power efficient method for digital circuits: a design methodology, in Proceedings 14th Annual IEEE International ASIC/SOC Conference (IEEE Cat. No.01TH8558), pp. 39–43 (2001)

A. Morgenshtein, A. Fish, I. A. Wagner, An efficient implementation of D-Flip-Flop using the GDI technique, in 2004 IEEE International Symposium on Circuits and Systems (IEEE Cat. No.04CH37512), vol. 2, pp. 665–673 (2004)

A. Morgenshtein, I. Shwartz, A. Fish, Gate Diffusion Input (GDI) logic in standard CMOS nanoscale process. 2010 IEEE 26th Conv. Electr. Electron. Eng. Isr. IEEEI 2010, 776–780 (2010)

M. Mukhedkar, W.B. Pandurang, A 180 nm efficient low power and optimized area ALU design using gate diffusion input technique. 2017 Int. Conf. Data Manag. Anal. Innov. ICDMAI 2017, 47–51 (2017)

H. Naseri, S. Timarchi, Low-Power and Fast Full Adder by Exploring New XOR and XNOR Gates, in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 8, pp. 1481–1493 (2018)

S. Rachana, N. Ramanjulu, P.K. Murthy, Design of area efficient and low power 4-bit multiplier based on TG. Int. J. Emerg. Technol. Innov. Res. 7(12), 83–88 (2020)

G. R. Murthy, C. Senthilpari, P. Velrajkumar, T. S. Lim, A new 6-Tmultiplexer based full-adder for low power and leakage current optimization, in IEICE Electronic Express, vol. 9, no. 17, pp. 1434–1441 (2012)

K. Rajyalakshmi, D.J. Nayudu, Novel architecture of 4-bit arithmetic logic unit (ALU) using full swing GDI technique. Int. J. Res. 7(XII), 1–6 (2018)

N. Ravindran, R. M. Lourde, An optimum VLSI design of a 16-BIT ALU, in International Conference on Information and Communication Technology Research ICTRC, pp. 52–55 (2015)

G.S. Reddy, K.V.K. Rao, 32-bit arithmetic and logic unit design with optimized area and less power consumption by using GDI technique. Int. J. Res. Comput. Appl. Robot. 3(4), 51–66 (2015)

R. Saxena, K. Sharma, Delay optimization and power optimization of 4-bit ALU designed in FS-GDI technique. Smart Moves J. IJOSci. 6(2), 1002 (2020)

A. Sadeghi, N. Shiri, M. Rafiee, High-efficient, ultra-low-power and high-speed 4:2 compressor with a new full adder cell for bioelectronics applications. Circuits Syst. Signal Process 39, 6247–6275 (2020). https://doi.org/10.1007/s00034-020-01459-x(2020)

M. Shoba, R. Nakkeeran, GDI based full adders for energy efficient arithmetic applications. Eng. Sci. Technol. Int. J. 19(1), 485–496 (2016)

R.L. Shukla, R. Mehra, Design analysis and simulation of 1 bit arithmetic logic unit on different foundaries. Int. J. Sci. Eng. 2, 28–29 (2014)

V.R. Tirumalasetty, M.R. Machupalli, Design and analysis of low power high-speed 1-bit full adder cells for VLSI applications. Int. J. Electron. 106(4), 521–536 (2019)

R. Uma, P. Dhavachelvan, Modified gate diffusion input technique: a new technique for enhancing performance in full adder circuits. Procedia Technol. 6, 74–81 (2012)

B.N. Vegha, V. Prakash, Design and implementation of 4-bit ALU for low-power using adiabatic logic based on FINFET. Int. J. Eng. Res. Technol. 9(07), 649–656 (2020)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

El-Bendary, M.A.M., Ayman, M. Efficient Multiple 4-Bit ALU Designs for Fast Computation and Reduced Area. Circuits Syst Signal Process 41, 4671–4691 (2022). https://doi.org/10.1007/s00034-022-02002-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02002-w