Abstract

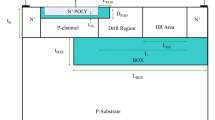

Silicon vertically double diffused metal oxide semiconductor field effect transistor (VDMOSFET) shows a great promise for low and medium power applications and is economical when compared to their compound semiconductor counterparts. A silicon power MOSFET can be optimized using a newly proposed drift layer design strategy to increase the breakdown performance. The main difference between existing standard design and the proposed design is that, the new design uses two drift layers instead of a single drift layer with a similar process complexity. Silicon VDMOSFETs are designed and optimized through process and device simulations. The performance advantages like breakdown voltage and on current have been estimated through a combination of device and process simulations. The proposed design resulted in a significant increase in breakdown voltage from 25 to 95 V. The improvement in the breakdown voltage is attributed to reduction in the intrinsic electric field due to dopant atom re-distribution. Complete process sequence for realization of the proposed design is described. Overall system advantages gained from the implementation of newly proposed structure and process sequence in Si power devices have also been demonstrated through simulations.

Similar content being viewed by others

References

V.K. Khanna, IGBT Theory and Design (Wiley, New York, 2003)

V. Bendaa, E.M.S. Narayanan, Microelectron. J. 35, 223 (2004)

G. Majumdar, in Proceedings of The International Workshop On Physics Of Semiconductor Devices 2007, Mumbai, India, pp. 787–792, 16–20 Dec 2007

S. Sandeep, R. Komaragiri, in Proceedings of the International Conference on Power Electronics (IICPE) 2010, New Delhi, India, pp. 1–5, 28–30 Jan 2011

F. Iannuzzo, C. Abbate, G. Busatto, IEEE Ind. Appl. Mag. 8, 28–39 (2014)

M.S. Shur, R. Gaska, A. Khan, G. Simin, in Proceedings of the Fourth IEEE International Caracas Conference on Devices, Circuits and Systems, 2002, Aruba, Dutch Caribbean, pp. D051-1, D051-8, 2002

F.W. Fuchs, in Proceedings of The 29th Annual Conference of The IEEE Industrial Electronics Society, 2003, Roanoke, Virginia, USA, pp. 1378–1385, 2–6 Nov 2003

S. Yang, A.T. Bryant, P.A. Mawby, D. Xiang, L. Ran, P. Tavner, IEEE Trans. Ind. Appl. 48(3), 1441–1451 (2011)

Y. Uemoto et al., IEEE Trans. Electron. Devices 54(12), 3393–3399 (2007)

Biela et al., IEEE Trans. Ind. Electron. 58(7), 2872–2882 (2011)

Jose Millan et al., IEEE Trans. Power Electron. 29(5), 2155–2163 (2014)

M. Ostling, R. Ghandi, C.-M. Zetterling, in IEEE 23rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2011, San Diego, California, USA, pp. 10, 15, 23–26 May 2011

ATHENA User’s Manual, SILVACO International, 4701 Patrick Henry Drive, Bldg. 1 October 2004

K.S. Oh, “MOSFET Basics: AN9010” Fairchild Semiconductor, July 2000

F. Frisina, Fabrication of VDMOS Structure with Reduced Parasitic Effects. U.S. Patent 6 391 723, 21 May 2002

J.D. Plummer, M. Deal, P.D. Griffin, Silicon VLSI Technology (Prentice Hall, Upper Saddle River, NJ, 2008)

A. Erbil, W. Weber, G.S. Cargill III, R.F. Boehme, Phys. Rev. B 34, 1392–1394 (1986)

ATLAS User’s Manual, SILVACO International, 4701 Patrick Henry Drive, Bldg. 1 Oct 2004

J.R. Brews, W. Fichtner, E.H. Nicollian, S.M. Sze, IEEE Electron. Device Lett. 1(1), 2–4 (1980)

Acknowledgments

R. K. thanks NIT Calicut for funding the project under FRG scheme.

Conflict of interest

This work is sponsored by National Institute of Technology Calicut (NITC) under faculty research grant (FRG). Other than this, the authors declare that they have no other conflict of interest.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sandeep, S., Komaragiri, R. Drift region optimization by double epitaxial layer in low and medium power rated silicon power MOSFETs. J Mater Sci: Mater Electron 26, 6692–6698 (2015). https://doi.org/10.1007/s10854-015-3271-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-015-3271-1