Abstract

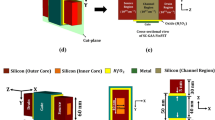

Gate dielectric materials play a key role in device development and study for various applications. We illustrate herein the impact of hetero (high-k/low-k) gate dielectric materials on the ON-current (\(I_{\mathrm{ON}}\)) and OFF-current (\(I_{\mathrm{OFF}}\)) of the heterogate junctionless tunnel field-effect transistor (FET). The heterogate concept enables a wide range of gate materials for device study. This concept is derived from the well-known continuity of the displacement vector at the interface between low- and high-k gate dielectric materials. Application of high-k gate dielectric material improves the internal electric field in the device, resulting in lower tunneling width with high \(I_{\mathrm{ON}}\) and low \(I_{\mathrm{OFF}}\) current. The impact of work function variations and doping on device performance is also comprehensively investigated.

Similar content being viewed by others

References

Khatami, Y., Banerjee, K.: Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Electron Devices 56(11), 2752–2761 (2009)

Kim, J.J., Roy, K.: Double gate-MOSFET subthreshold circuit for ultralow power applications. IEEE Trans. Electron Devices 51(9), 1468–1474 (2004)

Lu, H., Seabaugh, A.: Tunnel field-effect transistors: state-of-the-art. IEEE J. Electron Devices Soc. 2(4), 44–49 (2014)

Huang, Q., Huang, R., Chen, S., Wu, J., Zhan, Z., Qiu, Y., Wang, Y.: Device physics and design of T-gate Schottky barrier tunnel FET with adaptive operation mechanism. Semicond. Sci. Technol. 29(9), 095013 (2014)

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy-efficient. Nature 479, 329–337 (2011)

Knoch, J., Mantl, S., Appenzeller, J.: Impact of the dimensionality on the performance of tunneling FETs: bulk versus one-dimensional devices. Solid-State Electron. 51(4), 572–578 (2007)

Ilatikhameneh, H., Ameen, T.A., Klimeck, G., Appenzeller, J., Rahman, R.: Dielectric engineered tunnel field-effect transistor. IEEE Electron Device Lett. 36(10), 1097–1100 (2015)

Boucart, K., Ionescu, A.M.: A new definition of threshold voltage in tunnel FETs. Solid-State Electron. 52(9), 1318–1323 (2008)

Boucart, K., Ionescu, A.M.: Double gate tunnel FET with ultrathin silicon body and high-k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Jhaveri, R., Nagavarapu, V., Woo, J.C.: Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans. Electron Devices 58(1), 80–86 (2011)

Venkatagirish, N., Tura, A., Jhaveri, R., Chang, H. Y., Woo, J.: The tunnel source MOSFET: a novel asymmetric device solution for ultra-low power applications. In: 2009 IEEE International Conference on IC Design and Technology (pp. 155–159). IEEE, Piscataway (2009)

Zhang, Q., Zhao, W., Seabaugh, A.: Low-subthreshold-swing tunnel transistors. IEEE Electron Device Lett. 27(4), 297–300 (2006)

Kanungo, S., Rahaman, H., Gupta, P.S., Dasgupta, P.S.: A detail simulation study on extended source ultra-thin body double-gated tunnel FET. In: 2012 5th International Conference on Computers and Devices for Communication (CODEC, December) (pp. 1–4). IEEE, Piscataway (2012)

Wang, X.D., Xiong, Y., Tang, M.H., Peng, L., Xiao, Y.G., Xu, X.Y., He, J.H.: A Si tunnel field-effect transistor model with a high switching current ratio and steep sub-threshold swing. Semicond. Sci. Technol. 29(9), 095016 (2014)

Qiu, Y., Wang, R., Huang, Q., Huang, R.: A comparative study on the impacts of interface traps on tunneling FET and MOSFET. IEEE Trans. Electron Devices 61(5), 1284–1291 (2014)

Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94(5), 053511 (2009)

Lee, C.W., Ferain, I., Afzalian, A., Yan, R., Akhavan, N.D., Razavi, P., Colinge, J.P.: Performance estimation of junctionless multigate transistors. Solid-State Electron. 54(2), 97–103 (2010)

Colinge, J.P., Kranti, A., Yan, R., Lee, C.W., Ferain, I., Yu, R., Razavi, P.: Junctionless nanowire transistor (JNT): properties and design guidelines. Solid-State Electron. 65, 33–37 (2011)

Asthana, P.K., Ghosh, B., Rahi, S.B.M., Goswami, Y.: Optimal design for a high performance H-JLTFET using HfO\(_2\) as a gate dielectric for ultra low power applications. RSC Adv. 4(43), 22803–22807 (2014)

Rahi, S.B., Ghosh, B., Asthana, P.: A simulation-based proposed high-k heterostructure AlGaAs/Si junctionless n-type tunnel FET. J. Semicond. 35(11), 114005 (2014)

Rahi, S.B., Ghosh, B., Bishnoi, B.: Temperature effect on hetero structure junctionless tunnel FET. J. Semicond. 36(3), 034002 (2015)

Rahi, S.B., Ghosh, B.: High-k double gate junctionless tunnel FET with a tunable bandgap. RSC Adv. 5(67), 54544–54550 (2015)

Villani, F., Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: A quasi 2D semianalytical model for the potential profile in hetero and homojunction tunnel FETs. Solid-State Electron. 113, 86–91 (2015)

Silvaco, Version 5.15.32.R. (2015). http://www.silvaco.com (2015, Jul.) Atlas User’s Manual. http://www.silvaco.com

Robertson, J.: High dielectric constant oxides. Eur. Phys. J. Appl. Phys. 28(3), 265–291 (2004)

Holtij, T., Graef, M., Kloes, A., Iñíguez, B.: Modeling and performance study of nanoscale double gate junctionless and inversion mode MOSFETs including carrier quantization effects. Microelectron. J. 45(9), 1220–1225 (2014)

Graef, M., Holtij, T., Hain, F., Kloes, A., Iñíguez, B.: A 2D closed form model for the electrostatics in hetero-junction double-gate tunnel-FETs for calculation of band-to-band tunneling current. Microelectron. J. 45(9), 1144–1153 (2014)

Dutta, T., Kumar, S., Rastogi, P., Agarwal, A., Chauhan, Y.S.: Impact of channel thickness variation on bandstructure and source-to-drain tunneling in ultra-thin body III-V MOSFETs. IEEE J. Electron Devices Soc. 4(2), 66–71 (2016)

Yadav, C., Duarte, J.P., Khandelwal, S., Agarwal, A., Hu, C., Chauhan, Y.S.: Capacitance modeling in III-V FinFETs. IEEE Trans. Electron Devices 62(11), 3892–3897 (2015)

Patel, N., Ramesha, A., Mahapatra, S.: Drive current boosting of n-type tunnel FET with strained SiGe layer at source. Microelectron. J. 39(12), 1671–1677 (2008)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Rahi, S.B., Asthana, P. & Gupta, S. Heterogate junctionless tunnel field-effect transistor: future of low-power devices. J Comput Electron 16, 30–38 (2017). https://doi.org/10.1007/s10825-016-0936-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0936-9