Abstract

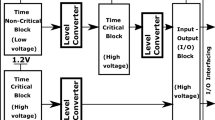

This paper presents a fast and power-efficient high voltage level shifter architecture capable of converting low level of input voltages into extremely high output voltage levels. The presented architecture uses single type of PMOS and NMOS transistors, operated at three times the safe operating area limit of transistors. The circuit is designed to take an input signal of 1V/0 and provides multiple output signals varying between 15, 10 and 5V/0 under the specified load condition. Circuit is designed and implemented in 110nm-BCD technology using 5V capable transistors. Post-layout simulation results demonstrate a total Energy Per Transition of 5.6pJ, a static current consumption of 180pA, and a propagation delay of 2nS for an input frequency of 100MHz.

Similar content being viewed by others

References

Liu, J., Ye, L., Deng, Z., Zhao, Jinshu., & Liao, H., 2010, “A 1.8V to 10V CMOS level shifter for RFID transponders,” 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, pp. 491-493

Otsuka, N., & Horowitz, M. A. (1997). Circuit techniques for 1.5-V power supply flash memory. IEEE Journal of Solid-State Circuits, 32(8), 1217–1230.

Moghe, Y., Lehmann, T., & Piessens, T. (2011). Nanosecond delay floating high voltage level shifters in a 0.35 \(mu\)m HV-CMOS technology. IEEE Journal of Solid-State Circuits, 46(2), 485–497.

Cha, H. K., Zhao, D., Cheong, J. H., Guo, B., Yu, H., & Je, M. (2013). A CMOS high-voltage transmitter IC for ultrasound medical imaging applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 60(6), 316–320.

Rana, V., & Sinha, R. (2018). Stress relaxed multiple output high-voltage level shifter. IEEE Transactions on Circuits and Systems II: Express Briefs, 65(2), 176–180.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rana, V., Vijayvergia, A. A 100MHz, 5.6pJ EPT, 1V to 15V full swing level shifter using low voltage transistors. Analog Integr Circ Sig Process 111, 243–250 (2022). https://doi.org/10.1007/s10470-021-01932-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01932-w