Abstract

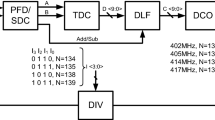

In order to suppress the spurious signal resulted from the reference leak and to decrease the oscillator jitter by using phase locked loop (PLL) loop band extension, a reference frequency multiplier that places a delay locked loop (DLL) in front of the PLL has been studied. However, a feedback circuit such as a DLL or an injection locked type voltage controlled oscillator must be used. In this paper, we propose a novel digital PLL capable of reference frequency multiplication without a feedback circuit. Simulink estimated the phase noise improved by − 17 dB at 1 MHz offset, and the spurious tones due to device variation reduced by − 12 dB with a dynamic element matching.

Similar content being viewed by others

References

Hayashi, I., Matsubara, T., Kumaki, S., Hasan Johari, A., Ishikuro, H., & Kuroda, T. (2010). A phase-to-digital converter for wide tuning range and PVT tolerant ADPLL operating Down TO 0.3 V. In Solid state circuits conference (A-SSCC), 2010 IEEE Asian (pp. 1–4).

Park, D., & Cho, S. H. (2012). A 14.2 mW 2.55-to-3 GHz cascaded PLL with reference injection and 800 MHz delta-sigma modulator in 0.13 μm CMOS. IEEE Journal of Solid-State Circuits, 47(12), 2989–2998.

Chien, G., & Gray, P. R. (2000). A 900-MHz local oscillator using a DLLbased frequency multiplier technique for PCS applications. IEEE Journal of Solid-State Circuits, 35(12), 1996–1999.

Ye, S., & Galton, I. (2004). Techniques for phase noise suppression in recirculating DLLs. IEEE Journal of Solid-State Circuits, 39(8), 1222–1230.

Kato, T., & Yasuda, A. (2018). A study of multiplied ΔΣ time to digital converter using Simulink model. In IEIEC system and circuit design (Vol. J101-A, no.6, pp. 1–8).

Miller, B., & Conley, B.(1990). A multiple modulator fractional divider. In IEEE international frequency control symposium (pp. 559–568).

Liao, D., Wang, H., Foster Dai, F., Xu, Y, & Berenguer, R. (2016). An 802.11 a/b/g/n digital fractional-N PLL with automatic TDC linearity calibration for spur cancellation. In IEEE radio frequency integrated circuits symposium (pp. 134–137).

Acknowledgements

This work is supported by VLSI Design and Education Center (VDEC), The University of Tokyo with the collaboration with Cadence Corporation.

Author information

Authors and Affiliations

Contributions

All authors approved the final version of the manuscript, and agree to be accountable for all aspects of the work in ensuring that questions related to the accuracy or integrity of any part of the work are appropriately investigated and resolved.

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kato, T., Yasuda, A. A study of phase noise suppression in reference multiple digital PLL without DLLs. Analog Integr Circ Sig Process 106, 441–447 (2021). https://doi.org/10.1007/s10470-020-01757-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01757-z