Abstract

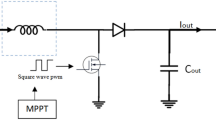

The performance of dc–dc power converters is critically dependent on the inductors at their core. Planar spiral inductors are compact constructions that can be scaled and integrated without the limitations of traditional wire-wound devices. Therefore, they are increasingly employed to meet the needs of modern low-power applications, especially where size, weight and manufacturing costs are deciding factors. As a planar inductor is designed to fit the parameters of an application, it is paramount to take into account the associated parasitic effects that have an impact on the converter performance. This paper analyzes how the conversion efficiency of boost and buck integrated power converters depends on the parasitics elements of planar inductors, and how it can be improved by optimizing the inductor layout. In particular, the paper provides the guidelines for maximizing the time constant of the inductor by considering the different geometrical features that define the inductor shape. The trade-offs that maximize the inductance time constant for different shapes are introduced, and an algorithm is developed to optimize the performance with no area overhead. Finally, three boost converters are designed, simulated, and compared in a 65-nm CMOS technology to demonstrate the validity of the proposed approach, and the corresponding conversion efficiency improvement is assessed.

Similar content being viewed by others

References

Mathúna, C. Ó., Wang, N., Kulkarni, S., & Roy, S. (2012). Review of integrated magnetics for power supply on chip (PwrSoC). IEEE Transactions on Power Electronics, 27(11), 4799–4816.

Rose, M., & Bergveld, H. J. (2016). Integration trends in monolithic power ICs: Application and technology challenges. IEEE Journal of Solid-State Circuits, 51(9), 1965–1974.

Li, J., Tseng, V. F., Xiao, Z., & Xie, H. (2017). A high-Q in-silicon power inductor designed for wafer-level integration of compact dc–dc converters. IEEE Transactions on Power Electronics, 32(5), 3858–3867.

Pardue, C. A., Bellaredj, M. L. F., Davis, A. K., Swaminathan, M., Kohl, P., Fujii, T., et al. (2018). Design and characterization of inductors for self-powered IoT edge devices. IEEE Transactions on Components, Packaging and Manufacturing Technology, 8(7), 1263–1271.

Richelli, A., Colalongo, L., Quarantelli, M., Carmina, M., & Kovács-Vajna, Z. M. (2004). A fully integrated inductor-based 1.8–6-V step-up converter. IEEE Journal of Solid-State Circuits, 39(1), 242–245.

Wibben, J., & Harjani, R. (2008). A high-efficiency dc–dc converter using 2 nH integrated inductors. IEEE Journal of Solid-State Circuits, 43(4), 844–854.

Wens, M., & Steyaert, M. S. J. (2011). A fully integrated CMOS 800-mW four-phase semiconstant on/off-time step-down converter. IEEE Transactions on Power Electronics, 26(2), 326–333.

Kudva, S. S., & Harjani, R. (2011). Fully-integrated on-chip dc–dc converter with a 450X output range. IEEE Journal of Solid-State Circuits, 46(8), 1940–1951.

Hernández, H., & Van Noije, W. (2015). Fully integrated boost converter for thermoelectric energy harvesting in 180 nm CMOS. Analog Integrated Circuits and Signal Processing, 82(1), 17–23.

Tang, N., Nguyen, B., Molavi, R., Mirabbasi, S., Tang, Y., Zhang, P., et al. (2017). Fully integrated buck converter with fourth-order low-pass filter. IEEE Transactions on Power Electronics, 32(5), 3700–3707.

Wens, M., & Steyaert, M. (2011). Design and implementation of fully-integrated dc–dc converters in standard CMOS. Dordrecht: Springer.

Shaltout, A. H., Lipski, M., & Gregori, S. (2018). Efficiency model of fully-integrated boost dc–dc converters. In Proceedings of the IEEE international symposium on circuits and systems (ISCAS) (pp. 1–5).

Aloisi, W., & Palumbo, G. (2005). Efficiency model of boost dc–dc PWM converters. International Journal of Circuit Theory and Applications, 33(5), 419–432.

Ahn, Y., Nam, H., & Roh, J. (2012). A 50-MHz fully integrated low-swing buck converter using packaging inductors. IEEE Transactions on Power Electronics, 27(10), 4347–4356.

Mohan, S. S., del Mar Hershenson, M., Boyd, S. P., & Lee, T. H. (1998). Simple accurate expressions for planar spiral inductances. IEEE Journal of Solid-State Circuits, 34(10), 1419–1424.

Lakdawala, H., Zhu, X., Luo, H., Santhanam, S., Carley, L. R., & Fedder, G. K. (2002). Micromachined high-Q inductors in a 0.18-\(\mu\)m copper interconnect low-k dielectric CMOS process. IEEE Journal of Solid-State Circuits, 37(3), 394–403.

Niknejad, A. M., & Meyer, R. G. (2000). Design, simulations, and applications of inductors and transformers for Si RF ICs. Norwell, MA: Kluwer.

Long, J. R., & Copeland, M. A. (1997). The modeling, characterization, and design of monolithic inductors for silicon RF IC’s. IEEE Journal of Solid-State Circuits, 32(3), 357–369.

Nieuwoudt, A., McCorquodale, M. S., Borno, R. T., & Massoud, Y. (2006). Accurate analytical spiral inductor modeling techniques for efficient design space exploration. IEEE Electron Device Letters, 27(12), 998–1001.

Ammouri, A., Ben-Salah, T., & Morel, H. (2018). A spiral planar inductor: An experimentally verified physically based model for frequency and time domains. International Journal of Numerical Modelling, 31(1), 1–13.

Bechir, M. H., Yaya, D. D., Kahlouche, F., Soultan, M., Youssouf, K., Capraro, S., et al. (2016). Planar inductor equivalent circuit model taking into account magnetic permeability, loss tangent, skin and proximity effects versus frequency. Analog Integrated Circuits and Signal Processing, 88(1), 105–113.

Crols, J., Kinget, P., Craninckx, J., & Steyaert, M. (1996). An analytical model of planar inductors on lowly doped silicon substrates for high frequency analog design up to 3 GHz. In Digest of technical papers of the symposium VLSI circuits (VLSI) (pp. 28–29).

Ronkainen, H., Kattelus, H., Tarvainen, E., Ruhisaari, T., Andersson, M., & Kuivalainen, P. (1997). IC compatible planar inductors on silicon. IEE Proceedings-Circuits, Devices and Systems, 144(1), 29–35.

Craninckx, J., & Steyaert, M. S. J. (1997). A 1.8-GHz low-phase-noise CMOS VCO using optimized hollow spiral inductors. IEEE Journal of Solid-State Circuits, 32(5), 736–744.

Wheeler, H. A. (1928). Simple inductance formulas for radio coils. Proceedings of the Institute of Radio Engineers, 16(10), 1398–1400.

Niknejad, A. M., & Meyer, R. G. (1998). Analysis, design, and optimization of spiral inductors and transformers for Si RF ICs. IEEE Journal of Solid-State Circuits, 33(10), 1470–1481.

del Mar Hershenson, M., Mohan, S. S., Boyd, S. P., & Lee, T. H. (1999). Optimization of inductor circuits via geometric programming. In Proceedings of the design automation conference (DAC) (pp. 994–998).

Shaltout, A. H., & Gregori, S. (2016). Conformal-mapping model for estimating the resistance of polygonal inductors. In Proceedings of the IEEE international symposium on circuits and systems (ISCAS) (pp. 1274–1277).

Haobijam, G., & Paily, R. (2007). Efficient optimization of integrated spiral inductor with bounding of layout design parameters. Analog Integrated Circuits and Signal Processing, 51(3), 131–140.

Shaltout, A. H., & Gregori, S. (2017). Design trade-offs of integrated polygonal inductors for dc–dc power converters. In Proceedings of the IEEE international symposium on circuits and systems (ISCAS) (pp. 1–4).

Post, J. E. (2000). Optimizing the design of spiral inductors on silicon. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 47(1), 15–17.

Nieuwoudt, A., & Massoud, Y. (2006). Variability-aware multilevel integrated spiral inductor synthesis. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 25(12), 2613–2625.

Acknowledgements

Funding was provided by the Natural Sciences and Engineering Research Council of Canada (Grant No. RGPIN-2017-06305).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shaltout, A.H., Gregori, S. Layout optimization of planar inductors for high-efficiency integrated power converters. Analog Integr Circ Sig Process 102, 155–167 (2020). https://doi.org/10.1007/s10470-019-01494-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01494-y