Abstract

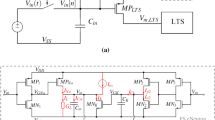

This paper presents a neural interface system-on-chip (SoC) featuring combined spike recording, electrical microstimulation, and real-time stimulus artifact rejection (SAR) for bidirectional interfacing with the nervous system. The SoC integrates a spike-recording front-end with input noise voltage of 3.42 μVrms (0.5 Hz–50 kHz), microstimulating back-end for delivering charge-balanced monophasic or asymmetric biphasic current pulses of <100 μA with passive discharge, and μW-level digital signal processing (DSP) unit for real-time SAR based on template subtraction. The DSP unit initializes its embedded 16b, 4 K static random-access memory with the first recorded stimulus artifact to reduce the operation time in generating an accurate artifact template signal for subtraction. Fabricated in AMS 0.35 μm 2P/4M CMOS, the 3.1 × 3.1-mm2 SoC has been characterized in benchtop tests and neurobiological experiments with isolated buccal ganglia of an Aplysia californica (a marine mollusk). The SoC can successfully remove mV-range stimulus artifacts with duration up to ~115 ms from the contaminated neural data in real time and recover µV-range extracellular neural spikes that occur on the tail end of the artifacts. The average root-mean-square (rms) value of the pre-processed stimulus artifact is reduced by a factor of ~24–30 post-processing, with DSP unit power consumption of <25 µW from 1.5 V.

Similar content being viewed by others

References

McGill, K. C., Cummins, K. L., Dorfman, L. J., Berlizot, B. B., Luetkmeyer, K., Nishimura, D. G., & Widrow, B. (1982). On the nature and elimination of stimulus artifact in nerve signals evoked and recorded using surface electrodes. IEEE Transactions on Biomedical Engineering, 29(2), 129–137.

Guggenmos, D. J., Azin, M., Barbay, S., Mahnken, J. D., Dunham, C., Mohseni, P., & Nudo, R. J. (2013). Restoration of function after brain damage using a neural prosthesis. Proceedings of the National Academy of Sciences of the USA (PNAS), 110(52), 21177–21182.

Azin, M., Guggenmos, D. J., Barbay, S., Nudo, R. J., & Mohseni, P. (2011). A battery-powered activity-dependent intracortical microstimulation IC for brain-machine-brain interface. IEEE Journal of Solid-State Circuits, 46(4), 731–745.

Shahrokhi, F., Abdelhalim, K., Serletis, D., Carlen, P. L., & Genov, R. (2010). The 128-channel fully differential digital integrated neural recording and stimulation interface. IEEE Transactions on Biomedical Circuits and Systems, 4(3), 149–161.

Sharma, V., McCreery, D. B., Han, M., & Pikov, V. (2010). Bidirectional telemetry controller for neuroprosthetic devices. IEEE Transactions on Neural Systems and Rehabilitation Engineering, 18(1), 67–74.

DeMichele, G., & Troyk, P. R. (2003). Stimulus-resistant neural recording amplifier. In Proceedings of the 25th Annual International IEEE Engineering in Medicine and Biology Conference (EMBC’03) (pp. 3329–3332).

Hines, A. E., Crago, P. E., Chapman, G. J., & Billian, C. (1996). Stimulus artifact removal in EMG from muscles adjacent to stimulated muscles. Journal of Neuroscience Methods, 64(1), 55–62.

Nikolic, Z. M., Popovic, D. B., Stein, R. B., & Kenwell, Z. (1994). Instrumentation for ENG and EMG recordings in FES systems. IEEE Transactions on Biomedical Engineering, 41(7), 703–706.

Jadvar, H., & Benson Jr., D. W. (1989). A stimulus artifact suppressor for esophageal pacing studies: Design and clinical testing. In Proceedings of the 11th Annual International IEEE Engineering Medicine Biology Conference (pp. 1401–1402).

Brown, E. A., Ross, J. D., Blum, R. A., Nam, Y., Wheeler, B. C., & DeWeerth, S. P. (2008). Stimulus-artifact elimination in a multielectrode system. IEEE Transactions on Biomedical Circuits and Systems, 2(1), 10–21.

Blum, R. A., Ross, J. D., Brown, E. A., & DeWeerth, S. P. (2007). An integrated system for simultaneous multichannel neuronal stimulation and recording. IEEE Transactions on Circuits and Systems: Part I, 54(12), 2608–2618.

Hanson, T. L., Omarsson, B., O’Doherty, J. E., Peikon, I. D., Lebedev, M. A., & Nicolelis, M. A. L. (2012). High-side digitally current-controlled biphasic bipolar microstimulator. IEEE Transactions on Neural Systems and Rehabilitation Engineering, 20(3), 331–340.

Wagenaar, D. A., & Potter, S. M. (2002). Real-time multichannel stimulus artifact suppression by local curve fitting. Journal of Neuroscience Methods, 120(2), 113–120.

Hashimoto, T., Elder, C. M., & Vitek, J. L. (2002). A template subtraction method for stimulus artifact removal in high-frequency deep brain stimulation. Journal of Neuroscience Methods, 113(2), 181–186.

Wichmann, T. (2000). A digital averaging method for removal of stimulus artifacts in neurophysiologic experiments. Journal of Neuroscience Methods, 98(1), 57–62.

Wichmann, T., & Devergnas, A. (2011). A novel device to suppress electrical stimulus artifacts in electrophysiological experiments. Journal of Neuroscience Methods, 201(1), 1–8.

Azin, M., Chiel, H. J., & Mohseni, P. (2007). Comparisons of FIR and IIR implementations of a subtraction-based stimulus artifact rejection algorithm. In Proceedings of the 29th Annual International IEEE Engineering Medicine Biology Conference (EMBC’07) (pp. 1437–1440).

Limnuson, K., Lu, H., Chiel, H. J., & Mohseni, P. (2014). Real-time stimulus artifact rejection via template subtraction. IEEE Transactions on Biomedical Circuits and Systems, 8(3), 391–400.

Limnuson, K., Lu, H., Chiel, H. J., & Mohseni, P. (2014). A bidirectional neural interface SoC with an integrated spike recorder, microstimulator, and low-power processor for real-time stimulus artifact rejection. In Proceedings of IEEE Custom Integrated Circuits Conference (CICC’14).

Hunter, J. S. (1986). The exponentially weighted moving average. The Journal of Quality Technology, 18(4), 203–210.

Oppenheim, A. V., & Schafer, R. W. (2010). Discrete-time signal processing. Upper Saddle River, NJ: Prentice-Hall.

Harrison, R. R., & Charles, C. (2003). A low-power low-noise CMOS amplifier for neural recording applications. IEEE Journal of Solid-State Circuits, 38(6), 958–965.

Jackson, A., Mavoori, J., & Fetz, E. E. (2006). Long-term motor cortex plasticity induced by an electronic neural implant. Nature, 444, 56–60.

Shahdoost, S., Frost, S., Van Acker, G., DeJong, S., Dunham, C., Barbay, S., Nudo, R., & Mohseni, P. (2014). Towards a miniaturized brain-machine-spinal cord interface (BMSI) for restoration of function after spinal cord injury. In Proceedings of the 36th Annual International IEEE Engineering Medicine Biology Conference (EMBC’14) (pp. 486–489).

Zimmermann, J. B., & Jackson, A. (2014). Closed-loop control of spinal cord stimulation to restore hand function after paralysis. Frontiers in Neuroscience, 8(87), 1–8.

Tsividis, Y. (1999). Operation and modeling of the MOS transistor (2nd ed.). New York, NY: Oxford University Press.

Demosthenous, A. (2014). Advances in microelectronics for implantable medical devices. Advances in Electronics. doi:10.1155/2014/981295.

Sooksood, K., Stieglitz, T., & Ortmanns, M. (2008). An experimental study on passive charge balancing. In Proceedings of the Annual Conference International Functional Electrical Stimulation Society (IFESS’08).

Ortmanns, M. (2007). Charge balancing in functional electrical stimulators: A comparative study. In Proceedings of the IEEE International Symposium Circuits and Systems (ISCAS’07) (pp. 573–576).

Arora, M. (2012). The art of hardware architecture: Design methods and techniques for digital circuits. New York, NY: Springer-Verlag.

Limnuson, K., Lu, H., Chiel, H. J., & Mohseni, P. (2011). FPGA implementation of an IIR temporal filtering technique for real-time stimulus artifact rejection. In Proceedings of the IEEE Biomedical Circuits and Systems Conference (BioCAS’11) (pp. 49–52).

McManus, J. M., Lu, H., & Chiel, H. J. (2012). An in vitro preparation for eliciting and recording feeding motor programs with physiological movements in Aplysia californica. Journal of Visualized Experiments, 70, e4320. doi:10.3791/4320.

Cullins, M. J., & Chiel, H. J. (2010). Electrode fabrication and implantation in Aplysia californica for multichannel neural and muscular recordings in intact, freely behaving animals. Journal of Visualized Experiments, 40, e1791. doi:10.3791/1791.

Acknowledgments

This work was supported by the Department of Defense Traumatic Brain Injury—Investigator-Initiated Research Award Program under Award W81XWH-10-1-0741 (to P. Mohseni) and National Institutes of Health grant NS047073 (to H. J. Chiel). The authors would like to thank J. McManus, Case Western Reserve University, Cleveland, OH, for his assistance in conducting the neurobiological experiments, as well as Dr. D. Guggenmos and Prof. R. Nudo, University of Kansas Medical Center, Kansas City, KS, for providing the prerecorded rat neural dataset. The authors would also like to thank Dr. M. Azin, QualComm, San Diego, CA, and Prof. M. Buchner, Case Western Reserve University, for helpful discussions that made this work possible.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Limnuson, K., Lu, H., Chiel, H.J. et al. A bidirectional neural interface SoC with an integrated spike recorder, microstimulator, and low-power processor for real-time stimulus artifact rejection. Analog Integr Circ Sig Process 82, 457–470 (2015). https://doi.org/10.1007/s10470-015-0489-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0489-z