Abstract

This paper introduces a highly efficient and low-power inverse class-F voltage doubler (VD) designed for radio frequency (RF) energy harvesting systems. Specifically tailored for mid-band 5G technology, the VD is designed for operation within the 1240–1300 MHz satellite band. The innovative design employs an inverse class-F architecture, incorporating a \(\lambda /8\) short-ended transmission line (TL) connected to the diode anode and a (\(\lambda /12\)) open-ended transmission line linked to the input of the voltage doubler. This configuration aims to reshape voltage and current waveforms, effectively reducing losses and series resistance in the diode. Dual-coupled transmission lines (CTLs) are utilized to provide passive voltage boosting at low-input power levels. The suggested voltage doubler is implemented using RO4003C substrate material with a dielectric relative permittivity (\({\upvarepsilon }_{r}\)) of 3.38 and a thickness of 0.81 mm. Measured results demonstrate a minimum input return loss of − 29.3 dB at 1.25 GHz, operating seamlessly within a frequency band from 1.18 to 1.32 GHz. The measured conversion efficiency is 45.2% at an input power (Pin) of − 4dBm. Furthermore, the peak RF–DC efficiency reaches 50% at an input power of 0dBm. Simulated results predict a remarkable conversion efficiency of 60% and 68.7% at − 4dBm and 0 dBm, respectively. In addition to its exceptional performance, the suggested voltage doubler exhibits an experimental DC output voltage of 0.53 V at \(P_{{{\text{in}}}} = - 10{\text{dBm}}\) and a saturated DC voltage of 3.4 V at an input power of 10dBm under a load terminal resistance of 8 KΩ. Finally, the dimensions of the proposed voltage doubler are \(25.3 \times 10.5 {\text{mm}}^{{2}}\).

Similar content being viewed by others

1 Introduction

Wireless power transfer (WPT) and radio frequency energy harvesting (RF-EH) have emerged as prominent focuses in microwave research. WPT is commonly utilized for long-distance and high-power transmission, while RF-EH concentrates on capturing low-power energy from diverse sources like Wi-Fi, GSM 900, and GSM 1800. The potential of RF-EH lies in its ability to power the Internet of Things (IoT), wireless sensor networks (WSNs), and medically implanted devices by converting otherwise wasted RF energy into usable DC output power. These energy harvesting circuits find applications in devices relying on limited power sources, such as batteries [2]. While the research on high-efficiency RF rectifiers has been extensive, there has been limited exploration of low-power rectifiers [6,7,8], 21.

Due to the complicated design of matching networks for larger bandwidths, only a limited number of broad-band rectifiers with high conversion efficiency have been reported [9]–11. On the other hand, multiband rectifiers are essential for sustaining device operation in the absence of energy sources [4, 10], 13. The nonlinear nature of diodes leads to variations in input impedance concerning frequency, DC load, and input power. To mitigate the variation in load impedance and rectifier nonlinearity, researchers have investigated resistance compression networks (RCNs), as discussed in [1]. Furthermore, multistage transmission line matching networks [19] and ladder LC networks [3] demonstrated effective matching over a wide range of frequencies.

In reference [13], a dual-band voltage doubler operating at frequencies of 0.85 and 1.4 GHz was developed utilizing double resonance circuits and a high Q-factor sine-shaped microstrip coil. This innovative design demonstrated an impressive maximum RF-to-DC efficiency of 50% at 0 dBm. Another noteworthy advancement is a wideband rectifier detailed in [14], showcasing an outstanding efficiency of 70% and yielding a DC voltage of 3.4 V at an input power of \(P_{{{\text{in}}}} = {\text{3dBm}}\). The investigation of wideband RF rectifiers has been a central focus of extensive research, with notable studies, such as those cited in [11], 12. For instance, the radio rectifier discussed in [11] employs microstrip transmission lines and (\(\lambda /4\)) short-circuit stubs designed for high-power systems, achieving peak RF-to-DC efficiency at a high-input power value (\(P_{{{\text{in}}}} = 15{\text{dBm}}\)). In [12], a wideband rectifier utilized dual L-sections for high-power applications. At an input power of \(P_{{{\text{in}}}} = 0{\text{dBm}}\), it obtained a maximum RF-to-DC efficiency of 30%, and the paper did not provide information on the DC output voltage.

Additionally, a balanced RF rectifier utilizing inverse class-F over a large PCB area of \(35{\text{ mm}} \times 36{\text{ mm}}\) achieved an exceptional efficiency of 74.9% at a high-input power of 19 dBm, making it unsuitable for low-power systems [17]. In [15], a class-F RF voltage doubler (VD) was presented, achieving an efficiency of 60.5% at an input power of 2 dBm using discrete lumped elements. However, a class-F with discrete lumped components is considered a high-level circuit due to its complicated network. Another approach in [23] designed a 2.38 GHz RF microwave rectifier based on a microstrip coupled transmission line, with a maximum efficiency of 62% at an input power of 0 dBm but with a relatively large board size of \(35{\text{ mm}} \times 35{\text{ mm}}\). Dual-coupled transmission lines in [22] were employed as a passive voltage boost, achieving a maximum RF-to-DC efficiency of 75.3% at an input power of 5.5 dBm and an efficiency of 58.5% at \(P_{{{\text{in}}}} = - 5{\text{dBm}}\), albeit with a large printed circuit board dimension of \(35{\text{ mm}} \times 34{\text{ mm}}\). In [24], a circuit configuration implementing an inverse class-F rectifier was realized under certain conditions, featuring a large PCB area of \(30{\text{ mm}} \times 19{\text{ mm}}\).

This paper introduces a novel approach a low-power and compact-size voltage doubler designed for energy harvesting applications. The proposed design employs an inverse class-F topology with dual microstrip coupled transmission lines (CTLs). This configuration minimizes diode losses by strategically manipulating current and voltage waveforms. The inverse class-F configuration employs a (\(\lambda /8\)) short-ended transmission line (TL) and a (\(\lambda /12\)) open-ended TL to minimize diode losses by reducing the overlap between current and voltage waveforms. In this configuration, the \((\lambda /8)\) short-ended TL and \((\lambda /12)\) open-ended TL actively shape the voltage and current waveforms, yielding a distinctive square wave for the current and a characteristic half-sinusoidal wave for the voltage. The achievement of inverse class-F operation relies on maintaining an out-of-phase relationship between the current and voltage, leading to a deliberate phase difference that significantly mitigates overlap. This intentional phase difference serves to reduce losses and enhance overall efficiency. To compact the printed circuit board (PCB) size, the \((\lambda /12) \) transmission line is intelligently divided into two parts, and the layout of the \((\lambda /8)\) short-ended TL takes the form of a U-shape. The design introduces a voltage boost at low-power levels through the incorporation of dual-coupled transmission lines (CTLs). The integration of the inverse class-F configuration with dual CTLs enables the voltage doubler to perform optimally, particularly in cases involving lower energy signals.

The voltage doubler achieves impressive measured and simulated conversion efficiencies of 50% and 68.7%, respectively, at 0 dBm. The design attains a measured RF–DC efficiency of 45.2% with a DC voltage of 1.24 V at \(P_{{{\text{in}}}} = - 4{\text{dBm}}\). Furthermore, it maintains a constant measured DC voltage of 3.4 V at an input power of 10 dBm. The efficiency bandwidth spans 140 MHz, and the printed circuit board (PCB) size is compact at \(0.19{\uplambda }_{{\text{g}}} \times 0.08{\uplambda }_{{\text{g}}} {\text{mm}}^{2}\).

The structure of the paper is organized as follows: Sect. 2 delves into the fundamentals of RF-to-DC rectifiers and introduces the basic concepts of inverse class-F. Section 3 provides an in-depth discussion on the design, analysis, fabrication, and experimental results of the proposed inverse class-F voltage doubler. Finally, Sect. 4 summarizes the work.

2 Fundamentals of RF-to-DC Rectifier

Diode-based voltage doubler circuits are more commonly used than CMOS circuits due to their low turn-on voltage [5]. Schottky barrier diodes with a low forward voltage drop are widely employed in RF energy harvesting applications, enhancing the conversion efficiency (\({\upeta }_{{{\text{RF}} - {\text{DC}}}}\)) at low-input power levels.

The conversion efficiency of the rectifier is primarily influenced by diode losses, impedance mismatch losses, printed circuit board (PCB) conductor losses, substrate losses, and radiation losses. Diode parameters such as series resistance (\(R_{S}\)), junction capacitance (\(C_{J}\)), built-in potential (\(V_{{{\text{bi}}}}\)), breakdown voltage (\(V_{{{\text{br}}}}\)), and higher-order harmonics generated by the diode contribute to diode losses. The loss in the low-input power region is attributed to the forward diode built-in potential (\(V_{{{\text{bi}}}}\)).

The loss in the high-input power region is attributed to the diode breakdown voltage (\(V_{{{\text{br}}}}\)), arising from the leakage current after the output voltage exceeds the breakdown voltage of the diode [16]. Losses resulting from power dissipation in the diode depend on the integral of the voltage waveform multiplied by the current waveform [6]. Reducing the integral outcome can be achieved by eliminating the overlap between the two waveforms, utilizing techniques such as class-F and inverse class-F.

The inverse class-F circuit is a harmonic elimination circuit consisting of \((\lambda /8)\) short-ended and (\(\lambda /12)\) open-ended transmission lines (TLs). The inverse class-F configuration is employed to create a high impedance at even harmonics and a low impedance at odd harmonics.

As a result, the voltage waveform is shaped to be a half-sinusoidal wave, while the current is formed as a square wave across the rectifying device, as illustrated in Fig. 1, according to Fourier series analysis [18]. This design reduces the overlap between the voltage and current waveforms, consequently minimizing power losses from the diode and enhancing efficiency.

3 Proposed Inverse Class-F Voltage Doubler

3.1 Design and Analysis

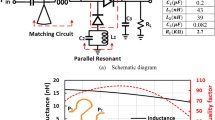

The schematic diagram of the suggested voltage doubler (VD), shown in Fig. 2, consists of a DC block capacitor (\(C_{b}\)), dual-coupled transmission lines (CTLs), an HSMS2852 zero-bias Schottky diode, a harmonic elimination circuit including a \(\lambda /8\) short-ended transmission line (TL), a \(\lambda /12\) open-ended TL, a DC filter (\(L_{1}\) and \(C_{1}\)), and load resistance (\(R_{L}\)).

The (\(\lambda /8\)) short-ended transmission line compensates for the capacitive input impedance of diode \(D_{1}\) by introducing an inductive reactance (\({\text{jZ}}_{01}\)) at the operating frequency \((f_{0} )\). Additionally, it functions as an open circuit at the second harmonic, thereby canceling the second current harmonic, as expressed in Eq. (1) [24].

where \(Z_{01}\) is the characteristic impedance for the (\(\lambda /8\)) transmission line, and \(f_{0}\) is the fundamental frequency at which the rectifier operates. The inductor \({\text{L}}_{1}\) eliminates the imaginary part of diode \(D_{2}\) and the output DC filter by setting the imaginary part, as specified in Eq. (2), equal to zero.

where \(Z_{D2}\) represents the input impedance of diode \((D_{2} )\). The (\(\lambda /12\)) open-ended transmission line is divided into two parts to compact the PCB size. It functions as a short circuit at the third harmonic, canceling the third voltage harmonic. Moreover, it acts as a parallel open stub, matching the input impedance of the diodes (\(Z_{D}\)) to the output impedance of the dual-coupled transmission lines (CTLs), denoted as (\(Z_{{{\text{out}}2}}\)), as expressed in Eq. (3) [24].

where Z02 is the characteristic impedance of the (\(\lambda /12\)) transmission line. The dual-coupled transmission lines (CTLs) are utilized to provide passive voltage gain at low-input power and to match the voltage doubler circuit to 50 Ω [22]. The voltage boost offered by the CTLs generates a sufficient input voltage higher than the forward built-in potential of the diode \(V_{{{\text{bi}}}}\), enabling the diodes to operate at lower input power levels than conventional configurations. The ABCD matrix for symmetric dual-coupled transmission lines can be expressed as follows [20].

where

where \({\uptheta }_{{{\text{l}}_{x} }}\) represents the electrical length of the xth CTL, while \(Z_{{{\text{ce }}x}}\) and \(Z_{{{\text{co }}x}}\) are the even-mode and odd-mode characteristic impedances of the xth CTL, respectively. The total passive boosting gain \((G_{t} )\) obtained by the dual CTLs can be derived as follows:

where \({\text{V}}_{1}\) and \({\text{V}}_{2}\) represent the input and output voltages of the dual-coupled transmission lines, respectively. \({\text{V}}_{{\text{x}}}\) is the voltage between the two coupled lines, and \({\text{Z}}_{{{\text{out}}{\kern 1pt} x}}\) is the output impedance of the xth CTL. Additionally, the relationship between the input impedance (\(Z_{i}\)) and the output impedance (\(Z_{{{\text{out}}}}\)) of each CTL can be expressed as follows:

To determine the values of the six parameters \(\left( {{\text{Z}}_{{\text{ce 1}}} ,{\text{ Z}}_{{\text{co 1}}} ,{\text{ Z}}_{{{\text{ce }}2}} ,{\text{ Z}}_{{{\text{co }}{\kern 1pt} {2}}} ,{ }\theta_{{\text{l 1}}} ,{\text{ and }}\theta_{{\text{l 2}}} } \right)\) that define the characteristics of the two CTLs, the following conditions should be satisfied:

-

(i)

The input impedance of the first CTL (\(Z_{{{\text{i}}1}}\)) should be matched to the port’s input impedance, which is 50 Ω.

$$ \begin{array}{*{20}c} {{\text{Z}}_{{{\text{i}}1}} = 50 \Omega } \\ \end{array} $$(7)

-

(ii)

The output impedance of the second CTL \((Z_{{{\text{out}}2}} )\) should match the input impedance of the voltage doubler (\(Z_{{{\text{in}}1}}\)), as shown in Eq. (8).

$$ \begin{array}{*{20}c} {Z_{{{\text{out}}2}} = Z_{{{\text{in}}1{ }}} } \\ \end{array} $$(8)The relationship between (\(Z_{{{\text{i}}1}}\)) and (\(Z_{{{\text{out}}2}}\)) of the dual CTLs can be expressed as follows:

$$ \begin{array}{*{20}c} {V_{1} = \left( {A_{1} A_{2} + B_{1} C_{2} } \right)V_{2} + \left( {A_{1} B_{2} + B_{1} D_{2} } \right)I_{2} } \\ {I_{1} = (C_{1} A_{2} + D_{1} C_{2} )V_{2} + (C_{1} B_{2} + D_{1} D_{2} )I_{2} } \\ {Z_{{{\text{i}}1}} = \frac{{V_{1} }}{{I_{1} }} = \frac{{\left( {A_{1} A_{2} + B_{1} C_{2} } \right) \times Z_{{{\text{out}}2}} + \left( {A_{1} B_{2} + B_{1} D_{2} } \right)}}{{(C_{1} A_{2} + D_{1} C_{2} ) \times Z_{{{\text{out}}2}} + (C_{1} B_{2} + D_{1} D_{2} )}}} \\ \end{array} $$(9)

-

(iii)

The total gain (\(G_{t}\)) of the dual CTLs should be greater than one, as derived from Eq. (4), as follows:

$$ \begin{array}{*{20}c} { V_{1} = (A_{1} A_{2} + B_{1} C_{2} )V_{{2{ }}} + \left( {A_{1} B_{2} + B_{1} D_{2} } \right)\frac{{V_{2} }}{{Z_{{{\text{out}}2}} }} } \\ {G_{t} = \frac{{V_{2} }}{{V_{1} }} = \frac{{Z_{{{\text{out}}2}} }}{{(A_{1} A_{2} + B_{1} C_{2} ) \times Z_{{{\text{out}}2}} + { }\left( {A_{1} B_{2} + B_{1} D_{2} } \right)}} > 1} \\ \end{array} { } $$(10)

-

(iv)

The gain of each CTL must exceed one.

$$ \begin{array}{*{20}c} {\left( {\frac{1}{{A_{1} + \frac{{B_{1} }}{{Z_{{\text{out 1}}} }}}}} \right) > 1 } \\ {\left( {\frac{1}{{A_{2} + \frac{{B_{2} }}{{Z_{{\text{out 2}}} }}}}} \right) > 1} \\ \end{array} $$(11)where the output impedance of the first CTL can be related to its input impedance using Eq. (6) as follows:

$$ \begin{array}{*{20}c} {Z_{{{\text{out}}1}} = - \frac{{50{ }D_{1} - B_{1} }}{{50{ }C_{1} - A_{1} }} } \\ \end{array} $$(12)The use of dual CTLs adds a significant degree of freedom to the system. With many parameters and few equations, there are infinitely many solutions to obtain the parameters \(\left( {Z_{{\text{ce 1}}} {, }Z_{{{\text{co1}}}} {, }Z_{{\text{ce 2}}} {, }Z_{{\text{co 2}}} {, }\theta_{{\text{l 1}}} {\text{, and}}\theta_{{\text{l 2}}} } \right)\) of dual CTLs. The constraints on selecting one of the solutions include values that yield the highest efficiency at low-input power, low conductor and radiation loss, and a compact size. The system equations from (4) to (12) are optimized using advanced design system (ADS).

3.2 Fabrication of RF Voltage Doubler

The layout for the suggested inverse class-F VD, depicted in Fig. 3(a), is implemented using RO4003C substrate material with a thickness of 0.81 mm and a dielectric relative permittivity (\({\upvarepsilon }_{r}\)) of 3.38. The dimensions are 25.3 mm × 10.5 mm. The manufacturing process employs photolithography with a mask resolution of approximately 4064 dpi (dots per inch). In the manufactured design, the minimum track width is 0.15 mm, and the minimum space between two tracks is also set to 0.15 mm. The design underwent simulation using the Advanced Design System program (ADS) and electromagnetic (EM) simulation for layout and physical verifications. Measurement tools include a signal generator with part number MG3697C, a vector network analyzer (VNA) identified as Rohde & Schwarz ZNA67, and a digital multimeter. Figure 3(b) and (c) displays the top and bottom views of the manufactured prototype photography. The bottom layer of the manufactured PCB serves as the ground layer, comprising a solid layer without any etching or DGS, as illustrated in Fig. 3(c).

For the Schottky diode, the model number HSMS2852 is selected, which has a low forward built-in potential voltage (\(V_{{{\text{bi}}}}\)) of 0.25 V, making it suitable for low-input power energy harvesting systems. However, it comes with a large series resistance (\(R_{s}\)) of 25 Ω. The issue of the series resistance is addressed by introducing the inverse class-F harmonic termination network, preventing the overlap of current and voltage across the diode with the series resistance. The values of discrete components used in the proposed design are given in Table 1, which includes the quality factor (Q), self-resonance frequency (SRF), and the manufacturer part number corresponding to each component.

The inductor \({\text{L}}_{1}\) is carefully selected to eliminate the imaginary part of Eq. (2) at the operating frequency (\(f_{0}\)), assuming a large value for the smoothing capacitor (\({\text{C}}_{1}\)). The smoothing capacitor (\({\text{C}}_{1}\)) serves the purpose of providing a smooth and ripple-free DC voltage at the circuit's output. While, the blocking capacitor (\(C_{b}\)) is employed to block the DC voltage generated by the rectifier. Its value is chosen to be sufficiently large to avoid affecting the input impedance. To ensure the inverse class-F operation, the voltage waveform is designed as a half-sinusoidal wave, while the current waveform adopts a square wave. Figure 4 provides a graphical representation of the voltage and current waveforms for the proposed inverse class-F voltage doubler, showcasing different input power levels (0 dBm, − 5 dBm, and − 10 dBm). In this illustration, the solid curves represent voltage waveforms, and the dashed curves elucidate current waveforms. The distinctive 180-degree phase shift between the current and voltage is evident, effectively minimizing their overlap and enhancing overall efficiency. Moving forward, Fig. 5 details the impedance contour of the proposed class-F−1 VD at an input power of -10 dBm. The configuration distinctly displays an open circuit at the second harmonic frequency of 2.47 GHz and a short circuit at the third harmonic frequency of 3.66 GHz.

The selection of the resistive load (\(R_{L}\)) is crucial, as it influences the DC voltage, the RF-to-DC efficiency (η), and the input power at which the peak efficiency (η) occurs. The output voltage is directly proportional to the load resistance, expressed as \(V_{{{\text{out}}}} = I_{{{\text{out}}}} \times { }R_{L}\), and the rectifier's conversion efficiency (η) decreases as the load \({\text{R}}_{{\text{L}}}\) increases, following the formula \({\upeta } = \frac{{P_{{{\text{out}}}} }}{{P_{{{\text{in}}}} }} = \frac{{V_{{{\text{out}}}}^{2} }}{{P_{{\text{in }}} \times { }R_{L} }}\). The peak efficiency occurs at an input power of \(P_{{{\text{in}}}} = \frac{{V_{{{\text{br}}}}^{2} }}{{4R_{L} }}\), where \(V_{{{\text{br}}}}\) is the breakdown voltage of the diode [16]. Thus, increasing the value of \(R_{L}\) shifts the maximum efficiency to lower input power levels. The impact of the load resistance (\(R_{L}\)) on the output DC voltage and efficiency is examined to determine the optimal value. Criteria for selecting \(R_{L}\) include finding the value that yields the highest output voltage and efficiency at low-input power levels. The optimal resistance value, RL, is determined through a careful trade-off between DC voltage (VDC) and RF–DC efficiency. The output voltage experiences an increase with the load resistance until it saturates at a high Pin. The behavior of efficiency in terms of \(R_{L}\) is complex, rising with the load resistor until it reaches a peak and then decreasing again as the load resistor increases. The influence of the load resistor (RL) on efficiency (η) is illustrated in Fig. 6. As observed, efficiency exhibits an inverse relationship with the value of RL and can be determined using the formula \(\eta = { }\frac{{V{\text{out}}^{2} }}{{R_{L} \times P_{{{\text{in}}}} { }}}\). Consequently, the selected RL = 8 kΩ results in the highest efficiency at an input power of − 10 dBm, whereas a 4 kΩ load resistor achieves a peak efficiency of 70% but shifts the peak efficiency to \(P_{{{\text{in}}}} = 3.5{\text{dBm}}\). The variation of DC output voltage with different load values is presented in Fig. 7. As cleared, any increase in the load resistor leads to a corresponding rise in the output DC voltage, as expressed by \(V_{{{\text{out}}}} = I_{{{\text{out}}}} \times R_{L}\).

3.3 Simulated and Measured Results

Figure 8 displays the simulated and measured DC output voltage against RF input power at a frequency of 1.25 GHz and a load of 8 kΩ. At an input power of -10 dBm, the measured DC output voltage equals 0.53 V and a saturated DC voltage of 3.4 V at \(P_{{{\text{in}}}} = 10{\text{dBm}}\). Additionally, the DC voltage is directly proportional to the RF input power, efficiency, and load resistance (\(R_{L}\)), as indicated by the efficiency equation (\(\eta = { }\frac{{V{\text{out}}^{2} }}{{R_{L} \times P_{{{\text{in}}}} { }}}\)), and the DC voltage saturates when the efficiency reaches its peak value.

The RF–DC conversion efficiency against input power for the suggested inverse class-F voltage doubler is shown in Fig. 9 at f0 = 1.25 GHz with a load resistance of 8 kΩ. As observed, the suggested voltage doubler achieves an extremely measured efficiency of 50% at \(P_{{{\text{in}}}} = 0{\text{dBm}}\) and a conversion efficiency of 45.2% at \(P_{{{\text{in}}}} = - 4{\text{dBm}}\). Furthermore, an efficiency of 35.3% at \(P_{{{\text{in}}}} = - 10{\text{dBm}}\) is achieved due to the use of dual CTLs, which increase the input voltage and reduce the built-in potential loss of the diode at low-input power. Figure 10 illustrates the simulated RF-to-DC efficiency versus the frequency for the suggested RF voltage doubler. Notably, a frequency bandwidth of 1 GHz to 1.52 GHz is achieved with an efficiency exceeding 40% at \(P_{{{\text{in}}}} = - 4{\text{dBm}}\). It is important to highlight that increasing the input power leads to higher RF–DC conversion efficiency, as the input impedance varies at different power levels, impacting the matching. Additionally, low-input power levels contribute to increased diode losses due to the required turn-on voltage of the diode. On the other hand, Fig. 11 depicts the measured and simulated efficiency (\(\eta\)) against frequency at \(P_{{{\text{in}}}} = - 4{\text{dBm}}\). The inverse class-F voltage doubler achieves a measured efficiency (\(\eta\)) of 45.2% at a frequency of 1.25 GHz. The difference between the measured and simulated results comes from the tolerance in discrete components, soldering effects, the influence of SMA connectors, PCB losses, parasitic impacts, and manufacturing errors. Figure 12 illustrates RF–DC conversion efficiency at \(f_{0}\) = 1.25 GHz for a lower input power range from − 30 to 0 dBm at \(R_{L}\) = 8 kΩ. The suggested voltage doubler achieves 25% efficiency at an input power of − 20 dBm and 37% at − 15 dBm.

Figure 13 shows large signal input return loss (\(|{\text{S}}_{11} |\)) at different input power levels. A satisfactory match with \(|{\text{S}}_{11} |\) below -10 dB is observed across the frequency band from 1200 to 1340 MHz. The diode's nonlinear nature causes its input impedance to vary with input power, requiring the matching circuit to be configured at a specific power level, in this case, − 10 dBm.

Figure 14(a) shows the measured input reflection coefficient \(\left| {{\text{S}}_{11} } \right|\) for the suggested inverse class-F VD, achieving an input return loss of − 29 dB at 1.25 GHz with a 100 MHz impedance bandwidth. While Fig. 14(b) displays a photograph of the voltage doubler's measurement system. Figure 14(c) illustrates the measured input reflection coefficient \(\left| {{\text{S}}_{11} } \right|\) at various input power levels of − 5 dBm, 0 dBm, 5 dBm, and 10 dBm. At an input power of 10 dBm, the proposed design exhibits a dual-band match at (1.1–1.35 GHz) and (1.5–1.72 GHz). However, at an input power of 5 dBm, the operating bandwidth narrows to (1.18–1.34 GHz) and (1.57–1.7 GHz), and so forth.

a Measured input reflection coefficient \(\left| {{\text{S}}_{11} } \right|\) for the suggested inverse class-F voltage doubler (VD), b photograph of the measurement system (VNA part number: Rohde & Schwarz ZNA67), and c measured input reflection coefficient \(\left| {{\text{S}}_{11} } \right|\) at several input power levels of − 5 dBm, 0 dBm, 5 dBm, and 10 dBm

The proposed inverse class-F design utilizes coupled transmission lines (CTLs) to boost the input voltage and enhance the conversion efficiency at low-power levels. Moreover, the CTLs affect the input reflection coefficient. The impact of CTLs on RF–DC conversion efficiency is illustrated in Fig. 15. Evidently, employing dual CTLs increases RF–DC conversion efficiency by over 5% at -10 dBm.

The impact of coupled transmission lines (CTLs) on the input return loss \(|{\text{S}}_{11} |\) versus frequency at a load resistance of 8 kΩ is illustrated in Fig. 16. It is evident that the use of dual CTLs improves input impedance matching, reducing the return loss at 1.3 GHz by introducing inductive reactance to the proposed voltage doubler. In Fig. 17, the DC output voltage exhibits a slight change with the incorporation of dual CTLs. While the impact of dual CTLs on DC voltage is marginal compared to using a single CTL, their use increases RF-to-DC efficiency by approximately 1.5% at − 10 dBm input power, as opposed to a single CTL. Notably, the dual CTL configuration significantly influences the input reflection coefficient \(\left| {{\text{S}}_{11} } \right|\), exhibiting an improvement of approximately − 3 dB compared to a single CTL, as shown in Fig. 16.

3.4 Comparison with the State of the Art

The suggested inverse class-F voltage doubler, which integrates dual microstrip coupled transmission lines, has been compared with recently reported RF rectifiers. The comparison encompasses working frequency, diode model, substrate material, conversion efficiency, load resistance, DC voltage, input reflection coefficient \(\left| {{\text{S}}_{11} } \right|\), and fabricated board size, as detailed in Table 2. The inverse class-F voltage doubler displays outstanding input matching, achieving − 29 dB, surpassing values in [11, 13, 14], and [24]. The proposed class-F−1 voltage doubler demonstrates an impressive conversion efficiency of approximately 35% at a low-input power of − 10 dBm, in contrast to the 58.5% reported at a higher input power of − 5 dBm in [22]. It is noteworthy that peak efficiency is attained at low-input power levels. Furthermore, the design accomplishes a high DC voltage of 0.53 V with a low-input power of − 10 dBm, surpassing the performance of references [14], 24. Finally, the design boasts a compact PCB area of (\(0.19\lambda_{g} \times 0.08\lambda_{g}\)), distinguishing it from state-of-the-art published works.

4 Conclusion

A low-power inverse class-F voltage doubler for energy harvesting (EH) systems has been comprehensively analyzed, designed, fabricated, and measured. The suggested voltage doubler (VD) configuration operates at a frequency of 1.25 GHz, aligning with the mid-band frequency range of 5G technology. The compact size of 2.66 cm2 is achieved using RO4003C substrate material with a dielectric relative permittivity (\({\upvarepsilon }_{r}\)) of 3.38 and a microstrip thickness of 0.81 mm. The inverse class-F configuration employs \(\lambda /8\) short-ended and \(\lambda /12\) open-ended transmission lines to minimize diode losses. Dual-coupled transmission lines are incorporated to enhance voltage at low-power levels. In prototype testing, the measured efficiency demonstrates an RF–DC conversion efficiency of 45.2% at \(P_{{{\text{in}}}} = - 4 {\text{dBm}}\), rendering it highly suitable for energy harvesting applications. The design achieves a peak efficiency of 50% at 0 dBm with an operating frequency of 1.25 GHz. This results in a DC output voltage of 0.53 V at -10 dBm and a saturated DC voltage of 3.4 V at an input power of 10 dBm. The proposed inverse class-F voltage doubler has been intricately designed to cater specifically to the needs of battery-powered implantable and wearable medical devices. This versatile design lends itself to a range of applications across various fields, including implantable wearable electronics, physiological operation monitoring, neural recording, and medical imaging. Its adaptability makes it a valuable asset in the realm of advanced medical technology.

Data Availability

The data that support the findings of this study are available from the corresponding author, [Marwa Mansour], upon reasonable request.

References

T.W. Barton, J.M. Gordonson, D.J. Perreault, Transmission line resistance compression networks and applications to wireless power transfer. IEEE J. Emerg. Sel. Top. Power Electron. 3(1), 252–260 (2015). https://doi.org/10.1109/JESTPE.2014.2319056

I.D. Bougas, M.S. Papadopoulou, A.D. Boursianis, K. Kokkinidis, S.K. Goudos, State-of-the-art techniques in RF energy harvesting circuits. Telecom 2(4), 369–389 (2021). https://doi.org/10.3390/telecom2040022

S. N. Daskalakis, A. Georgiadis, A. Collado, M. M. Tentzeris, An UHF rectifier with 100% bandwidth based on a ladder LC impedance matching network. European Microwave Week 2017: A Prime Year for a Prime Event. Conference Proceedings; 47th European Microwave Conference.1151–1154 (2017). https://doi.org/10.23919/EuMC.2017.8231052.

A.V.D.C. Dc, B. Converter, A. Richelli, L. Colalongo, S. Tonoli, Z.M. Kov, Triple-band single-layer rectenna for outdoor RF energy harvesting applications. Power 24(6), 1541–1546 (2009)

S.K. Divakaran, D.D. Krishna, Nasimuddin, RF energy harvesting systems: an overview and design issues. Int. J. RF Microw. Comput. Aided Eng. 29(1), 1–15 (2019). https://doi.org/10.1002/mmce.21633

J. Guo, H. Zhang, X. Zhu, Theoretical analysis of RF-DC conversion efficiency for class-F rectifiers. IEEE Trans. Microw. Theory Tech. 62(4), 977–985 (2014). https://doi.org/10.1109/TMTT.2014.2298368

X. Hua, R. Harjani, A 5μW-5mW input power range, 0–3.5V output voltage range RF energy harvester with power-estimator-enhanced MPPT controller. IEEE Cust. Integr. Circuits Conf. (2018). https://doi.org/10.1109/CICC.2018.8357083

H. Jabbar, Y.S. Song, T.T. Jeong, RF energy harvesting system and circuits for charging of mobile devices. IEEE Trans. Consum. Electron. 56(1), 247–253 (2010). https://doi.org/10.1109/TCE.2010.5439152

C. Jin, J. Wang, D.Y. Cheng, K.F. Cui, M.Q. Li, A novel wideband rectifier with two-level impedance matching network for ambient wireless energy harvesting. J. Phys. Conf. Ser. (2019). https://doi.org/10.1088/1742-6596/1168/2/022020

D. Lee, J. Oh, Broad dual-band rectifier with wide input power ranges for wireless power transfer and energy harvesting. IEEE Microwave Wirel. Compon. Lett. 32(6), 599–602 (2022). https://doi.org/10.1109/LMWC.2022.3145879

W. Liu, K. Huang, T. Wang, Z. Zhang, J. Hou, A broadband high-efficiency rf rectifier for ambient RF energy harvesting. IEEE Microwave Wirel. Compon. Lett. 30(12), 1185–1188 (2020). https://doi.org/10.1109/LMWC.2020.3028607

M.M. Mansour, H. Kanaya, Compact and broadband RF rectifier with 1.5 octave bandwidth based on a simple pair of L-section matching network. IEEE Microw. Wireless Comp. Letters. 28(4), 335–337 (2018)

M. Mansour, I. Mansour, Compact high-efficiency energy harvesting positive and negative DC supplies voltage for battery-less CMOS receiver. Sci. Rep. 13, 14180 (2023). https://doi.org/10.1038/s41598-023-41236-9

I. Mansour, M. Mansour, M. Aboualalaa, Compact and efficient wideband rectifier based on π network with wide input power range for energy harvesting. AEU—Int. J. Electron. Commun. 160, 154516 (2023). https://doi.org/10.1016/j.aeue.2022.154516

M. Mansour, I. Mansour, A. Zekry, A reconfigurable class-F radio frequency voltage doubler from 650 MHz to 900 MHz for energy harvesting applications. Alex. Eng. J. 61(10), 8277–8287 (2022). https://doi.org/10.1016/j.aej.2022.01.045

C.R. Valenta, G.D. Durgin, Harvesting wireless power: Survey of energy-harvester conversion efficiency in far-field, wireless power transfer systems. IEEE Microw. Mag. 15(4), 108–120 (2014). https://doi.org/10.1109/MMM.2014.2309499

M.D. Wei, Y.T. Chang, D. Wang, C.H. Tseng, R. Negra, Balanced RF rectifier for energy recovery with minimized input impedance variation. IEEE Trans. Microw. Theory Tech. 65(5), 1598–1604 (2017). https://doi.org/10.1109/TMTT.2016.2642959

Y.Y. Woo, Y. Yang, B. Kim, Analysis and experiments for high-efficiency class-F and inverse class-F power amplifiers. IEEE Trans. Microw. Theory Tech. 54(5), 1969–1974 (2006). https://doi.org/10.1109/TMTT.2006.872805

P. Wu et al., Compact high-efficiency broadband rectifier with multi-stage-transmission-line matching. IEEE Trans. Circuits Syst. II Express Br. 66(8), 1316–1320 (2019). https://doi.org/10.1109/TCSII.2018.2886432

Y. Wu, W. Sun, S.W. Leung, Y. Diao, K.H. Chan, A novel compact dual-frequency coupledline transformer with simple analytical design equations for frequency-dependent complex load impedance. Prog. Electromagn. Res. 134, 47–62 (2012). https://doi.org/10.2528/PIER12101906

T.W. Yoo, K. Chang, Theoretical and Experimental Development of 10 and 35 GHz Rectennas. IEEE Trans. Microw. Theory Tech. 40(6), 1259–1266 (1992). https://doi.org/10.1109/22.141359

F. Zhao, D. Inserra, G. Gao, Y. Huang, J. Li, G. Wen, High-efficiency microwave rectifier with coupled transmission line for low-power energy harvesting and wireless power transmission. IEEE Trans. Microw. Theory Tech. 69(1), 916–925 (2021). https://doi.org/10.1109/TMTT.2020.3027011

F. Zhao, D. Inserra, G. Wen, Compact and high-efficiency rectifier design based on microstrip coupled transmission line for energy harvesting. IEEE MTT-S Int. Microw. Symp. Digest. 2020, 1063–1065 (2020). https://doi.org/10.1109/IMS30576.2020.9224117

F. Zhao, D. Inserra, G. Wen, J. Li, Y. Huang, A High-Efficiency Inverse Class-F Microwave Rectifier for Wireless Power Transmission. IEEE Microw. Wirel. Compon. Lett. 29(11), 725–728 (2019). https://doi.org/10.1109/LMWC.2019.2944525

Funding

Open access funding provided by The Science, Technology & Innovation Funding Authority (STDF) in cooperation with The Egyptian Knowledge Bank (EKB).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

The author declares that she has no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Mansour, M. Low-Power Energy Harvesting Voltage Doubler Using CTLs Based on Inverse Class-F Configuration Compatible with Fifth Generation. Circuits Syst Signal Process (2024). https://doi.org/10.1007/s00034-024-02660-y

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00034-024-02660-y