Abstract

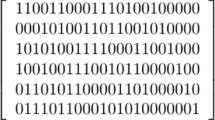

The most familiar way to minimize the influence of soft error in the memories is the employment of suitable error correcting codes (ECCs). The codes like single error correction (SEC) and single error correction-double error detection (SEC-DED) have been enormously employed for the detection and correction of double and single errors, respectively, in the memory systems. Single error correction-double error detection-double adjacent error correction (SEC-DED-DAEC) codes are the simplest form of adjacent ECCs which are proficient of correcting adjacent double errors along with the SEC-DED capability. An assortment of SEC-DED-DAEC codes have already been presented in this regard. But the major limitations of these codes are higher decoding complexities and mis-correction rate. In this paper, an efficient decoding technique has been presented to minimize the area and delay requirement of SEC-DED-DAEC codes with odd-column-weight H-matrix.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

R. C. Baumann, Soft errors in advanced computer systems. IEEE Des. Test. Comput. 22(3), 258266 (2005)

Chen, C.L., Hsiao, M.Y.: Error-correcting codes for semiconductor memory applications: a state-of-the-art review. IBM J. Res. Develop. 28(2), 124134 (1984)

Hsiao, M.Y.: A class of optimal minimum odd-weight-column SEC-DED codes. IBM J. Res. Develop. 14(4), 301395 (1970)

J. Samanta, Kewet, A.: Compact and high speed hsiao based SEC-DED code for cache memory. J. Circ. Syst. Comput. (World Sci.) 31(01), 1793–6454 (2021)

Tripathi, S., Maity, R.K., Jana, J., Samanta, J., Bhaumik, J.: FPGA based low area multi-bit adjacent error correcting codec for SRAM application. Radioelectro. Commun. Syst. J. 63(10), 543–552 (2020). Dec

Tripathi, S., Jana, J., Samanta, J., Anand, A., Kumar, C., Raj, G.: FPGA and ASIC implementation of SEC-DED-DAEC codes for SRAM application. In: Proceedings of the 2nd International Conference on Communication, Devices and Computing. Lecture Notes in Electrical Engineering, pp. 237–248, vol. 602. Springer, Singapore (2019)

Neale, A., Sachdev, M.: A new SEC-DED error correction code subclass for adjacent MBU tolerance in embedded memory. IEEE Trans. Device Mater. Rel. 13(1), 223230 (2013)

Neale, A.: Design and Analysis of an Adjacent Multi-bit Error Correcting Code for Nanoscale SRAMs. Ph.D. Thesis (2014)

Dutta, A., Touba, N.A.: Multiple bit upset tolerant memory using a selective cycle avoidance based SEC-DED-DAEC code. In: Proceedings of 25th IEEE VLSI Test Symposium 2007, pp. 349–354

Reviriego, P., Martnez, J., Pontarelli, S., Maestro, J.A.: A method to design SEC-DED-DAEC codes with optimized decoding. IEEE Trans. Dev. Mater. Reliab. 14(3), 884–889 (2014)

Maity, R.K., Samanta, J., Bhaumik, J.: New compact SEC-DED-DAEC code for memory applications. In: Proceedings of the 2nd International Conference on Communication, Devices and Computing, pp. 321–329. Springer, Singapore (2020)

Maity, R.K., Tripathi, S., Samanta, J., Bhaumik, J.: Lower complexity error location detection block of adjacent error correcting decoder for SRAMs. IET Comput. Dig. Techn. 14(5), 210–216 (2020)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Maity, R.K., Samanta, J., Bhaumik, J. (2022). An Efficient Decoding of SEC-DED-DAEC Code with Odd-Column-Weight H-matrix. In: Sikdar, B., Prasad Maity, S., Samanta, J., Roy, A. (eds) Proceedings of the 3rd International Conference on Communication, Devices and Computing. ICCDC 2021. Lecture Notes in Electrical Engineering, vol 851. Springer, Singapore. https://doi.org/10.1007/978-981-16-9154-6_63

Download citation

DOI: https://doi.org/10.1007/978-981-16-9154-6_63

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-16-9153-9

Online ISBN: 978-981-16-9154-6

eBook Packages: EngineeringEngineering (R0)