Abstract

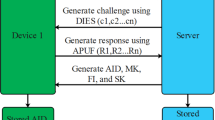

SoC FPGA are shrinking is size with advancement in the technologies. Miniaturization alone may not be sufficient to meet user requirements and hence security challenges remain unsolved. Existing approaches have their own limitations in terms of area and power. A model for two factor authentication is proposed with low- power, area and highly automative. It consists of a hybrid Physical unclonable functions (PUFs), which is used to abstract the unique ID of a chip and finite state machine (FSM) to verify that the Intellectual property (IP) is authentic or not. Recent hardware security applications such as IP protection, IC metering, hardware signature and obfuscation are mostly using PUF. Though most of these applications require a database to store the random outputs and complex security algorithms. This in turn increases the area, power, cost and energy consumption. A lightweight hybrid PUF model consisting of arbitrary and butterfly PUF along with the two-level FSM is projected for such security breaches which can be used for many IOT applications. Experimental results show that the area and power consumed is 5% and 9% respectively, for authenticating 26 IP in 13.25 s which is less than that of the conventional design.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Wang, D., et al.: Anonymous two-factor authentication in distributed systems: certain goals are beyond attainment. IEEE Trans. Dependable Secure Comput. 12(4), 428–442 (2015)

Baklouti, M., et al.: FPGA-based many-core System-on-Chip design. Microprocess. Microsyst. 39(4), 302–312 (2015)

Trimberger, S.M., Moore, J.J.: FPGA security: motivations, features, and applications. Proc. IEEE 102(8), 1248–1265 (2014)

Yan, W., Tehranipoor, F., Chandy, J.A.: A novel way to authenticate untrusted integrated circuits, pp. 89–94 (2014)

Zhang, J., et al.: A PUF-FSM binding scheme for FPGA IP protection and pay-per-device licensing. IEEE Trans. Inf. Forensics Secur. 10(6), 1137–1150 (2015)

Narasimhan, S., Chakraborty, R.S., Chakraborty, S.: Hardware IP protection during evaluation using embedded sequential trojan. IEEE Des. Test Comput. 29(3), 70–79 (2012)

Aysu, A., Schaumont, P.: Hardware/software co-design of physical unclonable function based authentications on FPGAs. Microprocess. Microsyst. 39(7), 589–597 (2015)

Zaker Shahrak, M.: Secure and lightweight hardware authentication using isolated physical unclonable function (2016)

Herder, C., et al.: Physical unclonable functions and applications: a tutorial. Proc. IEEE 102(8), 1126–1141 (2014)

Kumar, S.S., et al.: The butterfly PUF protecting IP on every FPGA. In: IEEE International Workshop on Hardware-Oriented Security and Trust, HOST 2008. IEEE (2014)

Zhang, J., et al.: Design and implementation of a delay-based PUF for FPGA IP protection. In: 2013 International Conference on Computer-Aided Design and Computer Graphics (CAD/Graphics). IEEE (2013)

Kokila, J., Ramasubramanian, N., Indrajeet, S.: A survey of hardware and software co-design issues for system on chip design. In: Choudhary, R.K., Mandal, J.K., Auluck, N., Nagarajaram, H.A. (eds.) Advanced Computing and Communication Technologies. AISC, vol. 452, pp. 41–49. Springer, Singapore (2016). https://doi.org/10.1007/978-981-10-1023-1_4

Frikken, K.B., Blanton, M., Atallah, M.J.: Robust authentication using physically unclonable functions. In: Samarati, P., Yung, M., Martinelli, F., Ardagna, C.A. (eds.) ISC 2009. LNCS, vol. 5735, pp. 262–277. Springer, Heidelberg (2009). https://doi.org/10.1007/978-3-642-04474-8_22

Lao, Y., et al.: Reliable PUF-based local authentication with self-correction. IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst. 36(2) 201–213 (2017)

Suh, G.E., Devadas, S.: Physical unclonable functions for device authentication and secret key generation. In: Proceedings of the 44th Annual Design Automation Conference. ACM (2007)

Shahrak, M., et al.: Two-way real time multimedia stream authentication using physical unclonable functions. In: IEEE 18th International Workshop on Multimedia Signal Processing (MMSP). IEEE (2016)

Johnson, A.P., Chakraborty, R.S., Mukhopadhyay, D.: A PUF-enabled secure architecture for FPGA-based IoT applications. IEEE Trans. Multi-Scale Comput. Syst. 1(2), 110–122 (2015)

Aysu, A., Schaumont, P.: PASC: physically authenticated stable-clocked SoC platform on low-cost FPGAs. In: 2013 International Conference on Reconfigurable Computing and FPGAs (ReConFig). IEEE (2013)

Sutar, S., Raha, A., Raghunathan, V.: D-PUF: an intrinsically reconfigurable DRAM PUF for device authentication in embedded systems. In: 2016 International Conference on Compliers, Architectures, and Sythesis of Embedded Systems (CASES). IEEE (2016)

Wang, X., et al.: IIPS: Infrastructure IP for secure SoC design. IEEE Trans. Comput. 64(8), 2226–2238 (2015)

Maiti, A., Gunreddy, V., Schaumont, P.: A systematic method to evaluate and compare the performance of physical unclonable functions. In: Athanas, P., Pnevmatikatos, D., Sklavos, N. (eds.) Embedded Systems Design with FPGAs, pp. 245–267. Springer, New York (2013). https://doi.org/10.1007/978-1-4614-1362-2_11

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Kokila, J., Baby Chellam, M., Murali Das, A., Ramasubramanian, N. (2018). Light Weight Two-Factor Authentication Using Hybrid PUF and FSM for SOC FPGA. In: Bhattacharyya, P., Sastry, H., Marriboyina, V., Sharma, R. (eds) Smart and Innovative Trends in Next Generation Computing Technologies. NGCT 2017. Communications in Computer and Information Science, vol 828. Springer, Singapore. https://doi.org/10.1007/978-981-10-8660-1_29

Download citation

DOI: https://doi.org/10.1007/978-981-10-8660-1_29

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-8659-5

Online ISBN: 978-981-10-8660-1

eBook Packages: Computer ScienceComputer Science (R0)