Abstract

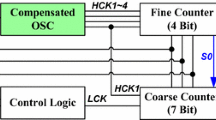

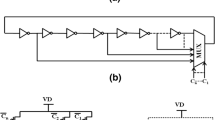

This paper presents a design of 4-channel Time-to-Digital Convertor (TDC) ASIC based on vernier ring oscillator technique. This technique implements two ring oscillators with very slight difference in time periods, which defines the resolution of TDC. The slight difference in time period is generated by using different fan-out load of the delay cell used to make respective ring oscillators. An on-chip calibration circuit provides the oscillator time period accurately for corrections, thereby reducing PVT (process, voltage, and temperature) variations. The TDC has been implemented using standard cell library of 0.35 μm commercial CMOS technology, achieving a resolution of 114 ps with a dynamic range of 1.8 μs and power consumption of 23 mW/channel.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Deng Z et al (2002) Design of new front end electronics for animal PET. In: nuclear science symposium and conference, vol 3, pp 1543–1546

Callewaert L et al (1989) Front end and signal processing electronics for detectors at high luminosity collider. IEEE Trans Nucl Sci 36:446–457

Kalisz J (2004) Review of time interval measurement techniques with picoseconds resolution. Metrologia 41(1):17

King ME, Barton RD (1971) Two vernier time-interval-digitizer. IEEE Trans Nucl Instrum Methods 359–370

Chen P et al (2007) PVT sensitive vernier based time-to-digital converter with extended input range and high accuracy. IEEE Trans Nucl Sci 54:294

Hari Prasad K, Chandratre VB, Saxena P, Pithawa CK (2011) FPGA based time-to-digital converter. DAE Symp Nucl Phys G-7

Acknowledgments

Authors would like to thank Shri Sekhar Basu, Director BARC; Dr. T.S. Ananthakrishnan, Head, Electronics Division, BARC; Dr. V. M. Datar, Head, Nuclear Physics Division, BARC and Prof. N.K. Mondal of TIFR for their support and encouragement.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer India

About this paper

Cite this paper

Hari Prasad, K., Sukhwani, M., Saxena, P., Pithawa, C.K., Chandratre, V.B. (2013). A CMOS Standard Cell-Based Time-to-Digital Converter. In: Chakravarthi, V., Shirur, Y., Prasad, R. (eds) Proceedings of International Conference on VLSI, Communication, Advanced Devices, Signals & Systems and Networking (VCASAN-2013). Lecture Notes in Electrical Engineering, vol 258. Springer, India. https://doi.org/10.1007/978-81-322-1524-0_13

Download citation

DOI: https://doi.org/10.1007/978-81-322-1524-0_13

Published:

Publisher Name: Springer, India

Print ISBN: 978-81-322-1523-3

Online ISBN: 978-81-322-1524-0

eBook Packages: EngineeringEngineering (R0)