Abstract

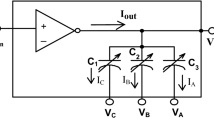

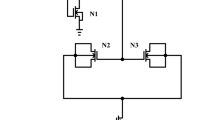

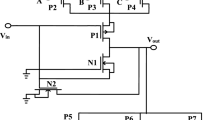

With the shift from traditional analog circuit designs to an all-digital intensive approach, the all-digital Phase-locked loops (ADPLLs) have become more attractive in digital communication systems. Digitally controlled oscillators (DCO) are the key components of the ADPLL circuits. In this paper, a new low power DCO structure is proposed with NMOS transistor as the switching network and utilizing the NMOS varactor as shunt-capacitive loads for the delay cells. The new DCO is capable of producing much higher output frequencies and comprises of components that are fully digital. The proposed DCO structure is designed for three, five and seven stages in CMOS 0.18 µm technology. Variable capacitance is achieved by the use of control word which is applied through NMOS switches conditionally selecting combinations of capacitance and hence determining the delay of the circuit. A 3-stages digitally controlled oscillator shows output frequency variation from 1.986 to 3.526 GHz with a power consumption of 1.484 mW. In the 5-stages DCO, the output frequency varies from 1.154 to 2.210 GHz with a power consumption of 2.762 mW. For 7-stages DCO, the output oscillation frequency is in the range from 0.835 to 1.658 GHz with a power consumption of 4.04 mW. A 3-stages DCO shows a phase noise of − 100.06 dBc/Hz with the offset of 1 MHz with the corresponding figure of merit (FoM) of 165.37 dBc/Hz. Five and seven-stages DCO show phase noise of − 102.08 dBc/Hz and − 105.52 dBc/Hz at 1 MHz respectively. The figure of merit (FoM) for 5 and 7-stages is 160.92 dBc/Hz and 159.07 dBc/Hz respectively. The digital tuning range for 3, 5, and 7-stages DCO is 55.96%, 62.78%, and 66.05% respectively. Further, the results show that the designed DCO has a maximum supply voltage tuning range of 101.45% with the variation of VDD from 1 to 1.8 V. Comparison with earlier reported circuits has been made based on output frequency, power consumption, and phase noise.

Similar content being viewed by others

References

Hwang, I., Lee, S., Lee, S., & Kim, S. (2000). A digitally controlled phase-locked loop with fast locking scheme for clock synthesis application. In Proceedings of the 47th Annual IEEE International Solid-State Circuits Conference (ISSCC’00) (pp. 168–169), San Francisco, Calif, USA, February 2000.

Boerstler, D. W. (1999). A low-jitter PLL clock generator for microprocessors with lock range of 340–612MHz. IEEE Journal of Solid-State Circuits, 34(4), 513–519. https://doi.org/10.1109/4.753684.

Staszewski, R. B., & Balsara, P. (2005). Phase-domain all-digital phase-locked loop. IEEE Transactions on Circuits and Systems-II: Express Briefs, 52(3), 159–163.

Larsson, P. (1999). A 2–166 MHz 1.2–2.5 V CMOS clock-recovery PLL with feedback phase-selection and averaging phase interpolation for jitter reduction. In Proceedings of IEEE International Solid-State Circuits Conference (ISSCC’99) (pp. 356–357), San Francisco, Calif, USA, February 1999.

Staszewski, B., Hung, C.-M., Maggio, K., Wallberg, J., Leipold, D., & Balsara, P. (2004). All-digital phase-domain TX frequency synthesizer for Bluetooth radios in 0.13-_m CMOS. In Proceedings of the IEEE Solid-State Circuits Conference (vol. 527, sec. 15.3, pp. 272–273).

Dunning, J., Garcia, G., Lundberg, J., & Nuckolls, E. (1995). An all-digital phase-locked loop with 50-cycle lock time suitable for high-performance microprocessors. IEEE Journal of Solid-State Circuits, 30(4), 412–422. https://doi.org/10.1109/4.375961.

Olsson, T., & Nilsson, P. (2004). A digitally controlled PLL for SoC applications. IEEE Journal of Solid-State Circuits, 39(5), 751–760. https://doi.org/10.1109/JSSC.2004.826333.

Chiang, Jen-Shiun, & Chen, Kuang-Yuan. (1999). The design of an all-digital phase-locked loop with small DCO hardware and fast phase lock. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 46(7), 945–950. https://doi.org/10.1109/82.775392.

Zhao, J., & Kim, Y. (2010). A low-power digitally controlled oscillator for all digital phase-locked loops VLSI design. Hindawi Publishing Corporation, vol. 2010, pp. 1–11.

Raha, P., Randall, S., Jennings, R., Helmick, B., Amerasekera, A., Haroun, B. (2002). A robust digital delay line architecture in a 0.13 μm CMOS technology node for reduced design and process sensitivities. In Proceedings international symposium on quality electronic design (pp. 148–153).

Tomar, A., Pokharel, R., Nizhnik, O., Kanaya, H., & Yoshida, K. (2007). Design of 1.1 GHz highly linear digitally-controlled ring oscillator with wide tuning range. In IEEE international workshop on radio-frequency integration technology (pp. 82–85).

Wu, C.-T., Wang, W., Wey, I.-C., & Wu, A.-Y. (2005). A scalable DCO design for portable ADPLL designs. In 2005 IEEE international symposium on circuits and systems, Kobe, 2005 (Vol. 6, pp. 5449–5452). https://doi.org/10.1109/iscas.2005.1465869.

Sheng, D., Chung, C. C., & Lee, C. Y. (2006). An all-digital phase-locked loop with high-resolution for SoC applications. In Proceedings of the international symposium on VLSI design, automation and test 2006 (pp. 1–4).

Sheng, D., Chung, C., & Lee, C. (2007). An ultra-low-power and portable digitally controlled oscillator for SoC applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 54(11), 954–958. https://doi.org/10.1109/TCSII.2007.903782.

Hsu, S., Yu, J., & Lee, C. (2010). A sub-10-μW digitally controlled oscillator based on hysteresis delay cell topologies for WBAN applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 57(12), 951–955. https://doi.org/10.1109/TCSII.2010.2087991.

Saint-Laurent, M., & Muyshondt, G. (2001). A digitally controlled oscillator constructed using adjustable resistors. In 2001 Southwest Symposium on Mixed-Signal Design (pp. 80-82).

Staszewski, R. B., Leipold, D., Muhammad, K., & Balsara, P. T. (2003). Digitally controlled oscillator (DCO)-based architecture for RF frequency synthesis in a deep-submicrometer CMOS Process. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 50(11), 815–828. https://doi.org/10.1109/TCSII.2003.819128.

Staszewski, R. B., Hung, C.-M., Leipold, D., & Balsara, P. T. (2003). A first multigigahertz digitally controlled oscillator for wireless applications. IEEE Transactions on Microwave Theory and Techniques, 51(11), 2154–2164. https://doi.org/10.1109/tmtt.2003.818579.

Chen, Pao-Lung, Chung, Ching-Che, & Lee, Chen-Yi. (2005). A portable digitally controlled oscillator using novel varactors. IEEE Transactions on Circuits and Systems II: Express Briefs, 52(5), 233–237. https://doi.org/10.1109/TCSII.2005.846307.

Maymandi-Nejad, M., & Sachdev, M. (2003). A digitally programmable delay element: Design and analysis. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 11(5), 871–878. https://doi.org/10.1109/tvlsi.2003.810787.

Saint-Laurent, M., & Swaminathan, M. (2001). A digitally adjustable resistor for path delay characterization in high-frequency microprocessors. In Southwest symposium on mixed-signal design (pp. 61–64).

Elrabaa, M. E. S. (2014). A portable high-frequency digitally controlled oscillator (DCO). Integration, the VLSI Journal, 47, 339–346.

Kumar, Manoj, & Dwivedi, Dileep. (2018). A low power CMOS-based VCO design with I-MOS varactor tuning control. Journal of Circuits, Systems and Computers, 27(10), 1–14. https://doi.org/10.1142/S0218126618501608.

Gonzalez-Diaz, V. R., Sanchez-Gaspariano, L. A., Muñiz-Montero, C., & AlvaradoPulido, J. J. (2016). Improving linearity in MOS varactor based VCOs by means of the output quiescent bias point. Integration, the VLSI Journal, 55, 274–280.

Kumar, M. (2013). A low power voltage controlled oscillator design. ISRN Electronics, vol. 2013, Article ID 987179, 6 pages.

Razavi, B. (1998). RF Microelectronics. New Jesey: Prentice Hall.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dabas, S., Kumar, M. A CMOS based low power digitally controlled oscillator design with MOS varactor. Analog Integr Circ Sig Process 100, 565–575 (2019). https://doi.org/10.1007/s10470-019-01476-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01476-0