Abstract

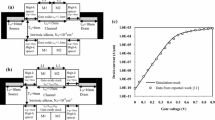

In this paper, we present a simulation study of analog circuit performance parameters of a dual material double-layer gate stack (high-k/SiO2) (DM-DGS) symmetric double-gate junctionless transistor (DGJLT). The characteristics are demonstrated and compared with dual material gate (DMG) DGJLT and single material (conventional) gate (SMG) DGJLT. DMG DGJLT present superior transconductance (Gm), early voltage (VEA) and intrinsic gain (GmRO) compared to SMG DGJLT. These parameters are further improved for DM-DGS DGJLT and it can be attributed to their better gate control on the channel region.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Colinge, J.P., Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.M., McCarthy, B., Murphy, R.: Nanowire Transistors Without Junctions. Nature Nanotechnology 5, 225–229 (2010)

Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.P.: Junctionless Multigate Field - Effect Transistor. Applied Physics Letters 94, 053 511-1–053 511-2 (2009)

Lee, C.W., Afzalian, A., Akhavan, R., Ferain, N.D., Yan, I., Razavi, P.R., Doria, R.T., Colinge, J.P.: Low Subthreshold Slope in Junctionless Multigate Transistor. Applied Physics Letters 96, 102106 (2010)

Lee, C.W., Ferain, I., Afzalian, A., Yan, R., Akhavan, N.D., Razavi, P., Colinge, J.P.: Performance estimation of junctionless multigate transistors. Solid-State Electronics 54, 97–103 (2010)

Doria, R.T., Pavanello, M.A., Trevisoli, R.D., de Souza, M., Lee, C.W., Ferain, I., Akhavan, N.D., Yan, R., Razavi, P., Yu, R., Kranti, A., Colinge, J.P.: Junctionless Multiple - Gate Transistors for Analog Applications. IEEE Trans. Electron Devices 58, 2511–2519 (2011)

Cho, S., Kim, K.R., Park, B.G., Kang, I.M.: RF performance and small signal parameter extraction of junctionless silicon nanowire MOSFET. IEEE Trans. Electron Devices 58(5) (2011)

Lou, H., Zhang, L., Zhu, Y., Lin, X., Yang, S., He, J., Chan, M.: A Junctionless Nanowire Transistor with a Dual-Material Gate. IEEE Trans. Electron Devices 59(7), 1829 (2012)

Razavi, P., Orouji, A.A.: Dual Material Gate Oxide Stack Symmetric Double Gate MOSFET: Improving Short Channel Effects of Nanoscale Double Gate MOSFET. In: Int. Biennial Baltic Electronics Conference (2008)

Long, W., Ou, H., Kuo, J.-M., Chin, K.K.: Dual - Material Gate (DMG) Field Effect Transistor. IEEE Trans. Electron Devices 46(5), 1829 (1999)

Ghosh, P., Haldar, S.R., Gupta, S., Gupta, M.: Analytical Modeling and Simulation for Dual Metal Gate Stack Architecture (DMGSA) Cylindrical/Surrounded Gate MOSFET. J. of Semiconductor Technology and Science 12(4) (2012)

Kasturi, P., Saxena, M., Gupta, M., Gupta, R.S.: Dual Material Double - Layer Gate Stack SON MOSFET: A Novel Architecture for Enhanced Analog Performance—Part I: Impact of Gate Metal Workfunction Engineering. IEEE Trans. Electron Devices 55(1), 372–381 (2008)

Kasturi, P., Saxena, M., Gupta, M., Gupta, R.S.: Dual Material Double-Layer Gate Stack SON MOSFET: A Novel Architecture for Enhanced Analog Performance—Part II: Impact of Gate - Dielectric Material Engineering. IEEE Trans. Electron Devices 55(1), 382–387 (2008)

Park, J.C., Lee, H.N.: Improvement of the Performance and Stability of Oxide Semiconductor Thin - Film Transistors Using Double-Stacked Active Layers. IEEE Trans. Electron Devices 33(6), 818–820 (2012)

Kumar, M., Chaudhry, A.: Two – dimensional analytical modelling of fully depleted DMG SOI MOSFET and evidence for diminished SCEs. IEEE Trans. Electron Devices 51(4), 569–574 (2004)

Chakraborty, S., Mallik, A., Sarkar, C.: Subthreshold performance of dual-material gate CMOS devices and circuits for ultralow power analog/mixed-signal applications. IEEE Trans. Electron Devices 55(3), 827–832 (2008)

Duarte, J.P., Choi, S.J., Moon, D.I., Choi, Y.K.: Simple Analytical Bulk Current Model for Long - Channel Double – Gate Junctionless Transistors. IEEE Electron Device Letter 32(6) (2011)

Sallese, J.M., Chevillon, N., Lallement, C., Iñiguez, B., Prégaldiny, F.: Charge-Based Modeling of Junctionless Double - Gate Field - Effect Transistors. IEEE Transactions on Electron Devices 58(8) (2011)

Atlas User’s Manual: Device Simulation Software (2008)

Tsividis, Y.: Operation and Modeling of the MOS Transistor, 2nd edn. Oxford Univ. Press, New York (1999)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Baruah, R.K., Paily, R.P. (2013). A Dual Material Double-Layer Gate Stack Junctionless Transistor for Enhanced Analog Performance. In: Gaur, M.S., Zwolinski, M., Laxmi, V., Boolchandani, D., Sing, V., Sing, A.D. (eds) VLSI Design and Test. Communications in Computer and Information Science, vol 382. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-42024-5_15

Download citation

DOI: https://doi.org/10.1007/978-3-642-42024-5_15

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-42023-8

Online ISBN: 978-3-642-42024-5

eBook Packages: Computer ScienceComputer Science (R0)