Abstract

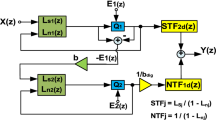

Translation of the amplitude axis to the time axis can be a promising approach to alleviate the analog-to-digital converter’s resolution problems in low-voltage CMOS circuits. From this point of view, a noise-coupled time-based continuous-time sigma-delta modulator (TCSDM) based on the asynchronous pulse width modulator (APWM) and the time-to-digital converter (TDC) is presented. Noise-coupling is realized by extracting the time quantization error of the TDC and injecting its delayed version to the input of the APWM. By using a novel implementation of the noise-coupling technique in the proposed TCSDM, the modulator’s noise-shaping order is improved by one. Unlike the conventional noise-coupled sigma-delta modulators, in the proposed structure, the need of an extra subtractor at the quantizer input is resolved through merging the excess loop delay compensation path with the proposed noise-coupling branch. Comparative analytical calculations and behavioral simulation results are presented to verify the performance of the proposed time-based modulator. To confirm the validity of the proposed structure, the effects of main circuit non-idealities in the modulator’s performance are taken into consideration and the related simulation results are investigated. A digital-friendly implementation of the quantizer in the proposed modulator makes it suitable for low-voltage nanometer CMOS technologies.

Similar content being viewed by others

References

Mitteregger, G., Ebner, C., Mechnig, S., Blon, T., Holuigue, C., & Romani, E. (2006). A 20-mW 640-MHz CMOS continuous-time ADC with 20-MHz signal bandwidth, 80-dB dynamic range and 12-bit ENOB. IEEE Journal of Solid-State Circuits, 41(12), 2641–2649.

Fei, Y. (2014). Design techniques for time-mode noise-shaping analog-to-digital converters: a state-of-the-art review. Analog Integrated Circuits and Signal Processing, 79, 191–206.

Straayer, M., & Perrott, M. H. (2009). A multi-path gated ring oscillator TDC with first-order noise shaping. IEEE Journal of Solid-State Circuits, 44(4), 1089–1098.

Pakniat, H., & Yavari, M. (2013). A time-domain noise-coupling technique for continuous-time sigma-delta modulators. Analog Integrated Circuits and Signal Processing, 78, 439–452.

Iwata, A. (1999). The architecture of delta sigma analog-to-digital converters using a VCO as a multi bit quantizer. IEEE Transactions on Circuits and Systems-II: Express Briefs, 46(8), 941–945.

Li, G., Tousi, Y., Hassibi, A., & Afshari, E. (1999). Delay-line-based analog-to-digital converters. IEEE Transactions on Circuits and Systems-II: Express Briefs, 56(6), 464–468.

Straayer, M. Z., & Perrott, M. H. (2008). A 12-bit, 10-MHz bandwidth, continuous-time ΔΣ ADC with a 5-bit, 950-MS/s VCO-based quantizer. IEEE Journal of Solid-State Circuits, 43(4), 805–814.

Dhanasekaran, V., Gambhir, M., Elsayed, M. M., Sanchez-Sinencio, E., Silva-Martinez, J., Mishra, C., et al. (2011). A continuous-time multi-bit ΔΣ ADC using time domain quantizer and feedback element. IEEE Journal of Solid-State Circuits, 46(3), 639–650.

Lee, K., Bonu, M., & Temes, G. C. (2006). Noise-coupled delta-sigma ADCs. Elect. Letters, 42(3), 1381–1382.

Wang, Y., & Temes, G. C. (2009). Noise-Coupled continuous-time delta-sigma ADCs. Electronics Letters, 45(6), 302–303.

Roza, E. (1997). Analog-to-digital conversion via duty-cycle modulation. IEEE Transactions on Circuits and Systems-II: Express Briefs, 44(11), 907–914.

Daniels, J., Dehaene, W., Steyaert, M., & Wiesbauer, A. (2010). A/D conversion using asynchronous ΣΔ modulation and time-to digital conversion. IEEE Transactions on Circuits and Systems-I: Regular Papers, 57(9), 2404–2412.

Weibo, L., Orino, Y., Shinnosuke, H., & Minoru, K. K. (2013). Design of a self-oscillating PWM signal generator with a double integration loop. IEEE Transactions on Circuits and Systems-I: Regular Papers, 60(8), 2064–2073.

Gelb, A., & Velde, W. V. (1968). Multiple-input describing functions and non-linear system design. New York: McGraw-Hill.

Wang, Z. (1991). CMOS adjustable Schmitt trigger. IEEE Transactions on Instrumentation Measurement, 40(3), 601–605.

Katyal, V., Geiger, R., & Chen, D., (2014). Adjustable hysteresis CMOS Schmitt trigger. In Proceedings of the IEEE International Symposium Circuits Systems (pp. 1938–1941).

Jingxue, L., & Ranjit, G. (2011). Design and Analysis of a self-oscillating class D audio amplifier employing a hysteretic comparator. IEEE J Solid-State Circuits, 46(10), 2336–2349.

Cherry, J. A., & Snelgrove, W. M. (1999). Continuous-time delta-sigma modulators for high-speed A/D conversion. Dordrecht: Kluwer Academic Publisher.

Vuyst, B. D., & Rombouts, P. (2011). A 5-MHz 11-bit self oscillating ΣΔ modulator with a delay-based phase shifter in 0.025 mm2. IEEE J Solid-State Circuits, 46(8), 1919–1927.

Hernandez, L., & Prefasi, E. (2008). Analog to digital conversion using noise shaping and time encoding. IEEE Transactions on Circuits Systems I, Regular Papers, 55(8), 2026–2037.

Lin, Y., & Ismail, M. (2012). Time-based all-digital sigma-delta modulators for nanometer low voltage CMOS data converters. Analog Integrated Circuits and Signal Processing, 73, 801–808.

Roberts, G. W., & Ali-Bakhshian, M. (2010). A brief introduction to time-to-digital and digital-to-time converters. IEEE Transactions on Circuits and Systems-II: Express Briefs, 57(3), 153–157.

Ortmanns, M., & Gerfers, F. (2005). Continuous-time sigma-delta A/D conversion. Berlin/Heidelberg: Springer.

Schreier, R., & Temes, G. C. (2005). Understanding delta-sigma data converters. Wiley/IEEE Press: Piscataway.

Hamoui, A., & Martin, K. W. (2004). High-order multi-bit modulators and pseudo data-weighted-averaging in low-oversampling ΣΔ ADCs for broad-band applications. IEEE Transactions on Circuits and Systems-I: Regular Papers, 51(1), 72–85.

Malcovati, P., Brigati, S., Francesconi, F., Maloberti, F., Cusinato, P., & Baschirotto, A. (2003). Behavioral modeling of switched-capacitor sigma-delta modulators. IEEE Transactions on Circuits and Systems-I: Regular Papers, 50(3), 352–364.

Ashry, A., & Aboushady, H. (2009). Fast and accurate jitter simulation technique for continuous-time Σ∆ modulators. Electronics Letters, 45(24), 1218–1219.

Baird, R. B., & Fiez, T. S. (1995). Linearity enhancement of multi-bit ΔΣ A/D and D/A converters using data weighted averaging. IEEE Transactions on Circuits and Systems-II: Express Briefs, 42(12), 753–762.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Tamaddon, M., Yavari, M. An NTF-enhanced time-based continuous-time sigma-delta modulator. Analog Integr Circ Sig Process 85, 283–297 (2015). https://doi.org/10.1007/s10470-015-0562-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0562-7