Abstract

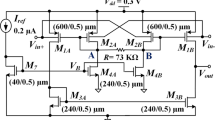

Simple and symmetrical ultra low-voltage current mode analog circuits and autozeroing amplifiers are presented. The low-voltage analog circuits are based on low-voltage inverters resembling precharge digital logic. Ultra low-voltage analog circuits can be operated at supply voltages down to 250 mV with rail-to-rail input and output swing. The output current of the ultra low-voltage symmetrical transconductance amplifier can be quite large due to a current boost technique. Ultra low-voltage analog circuits can be operated at supply voltages down to 250 mV with rail- to-rail input and output swing. The current headroom is 3 μA and the supply voltage is 300 mV. For supply voltages down to 300 mV simulated data shows that the maximum clock frequency is approximately 600 MHz.

Similar content being viewed by others

References

Galton, I. (2009). Low-voltage analog and mixed-signal CMOS circuit design. In IEEE International solid-state conference (ISSCC), p. 502.

Ramirez-Amgulo, J., Gonzalez-Carvajal, R., Lopez-Martin, A., & Torralba, A. (2004). Some techniques for low-voltage continuous-time analog circuit operation. In Proceedings of the 2004 IEEE Dallas/CAS Workshop (DCAS-04), pp. 87–112.

Binkley, D.M. (2008). Tradeoffs and optimization in analog CMOS design, 1st ed. New York: Wiley-Interscience.

Michel, F., & Steyaert, M. S. J. (2012). 250 mV 7.5 W 61 dB SNDR SC modulator using near-threshold-voltage-biased inverter amplifiers in 130 nm CMOS. IEEE Journal of solid-state circuits, 47(3), 709–721.

Fayomi, C. J. B., Roberts, G. W., & Sawan, M. (2005). Low-voltage CMOS analog bootstrapped switch for sample-and-hold circuit: Design and chip characterization. In IEEE International symposium on circuits and systems (ISCAS), Vol. 3, pp. 2000–2003.

Carvajal, R. G., Ramrez-Angulo, J., Lopez-Martin, A. J., Torralba, A., Galan, J. A. G., Carlosena, A., & Chavero, F. M. (2005). The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Transactions on Circuits and Systems I: Regular Papers, 52(7), 1276–1291.

Kuo, C.-H., Kuo, T.-H., & Wen, K.-L. (2010). Bias-and-input interchanging technique for cyclic/pipelined ADCs With opamp sharing. IEEE Transactions on Circuits and Systems II: Express Briefs, 57(3), 168–172.

Berg, Y., Wisland, D.T. & Lande, T.S. (1999). Ultra low-voltage/low-power digital floating-gate circuits. IEEE Transactions on Circuits and Systems II, 46(7), 930–936.

Kotani, K., Shibata, T., Imai, M., & Ohmi, T. (1995). Clocked-Neuron-MOS logic circuits employing auto-threshold-adjustment. In IEEE International solid-state circuits conference (ISSCC), pp. 320–321, 388.

Lashevsky, R., Takaara, K., & Souma, M. (1998). Neuron MOSFET as a way to design a threshold gates with the threshold and input weights alterable in real time. In IEEE TT13.11-1.4, pp. 263–266.

Shibata, T., & Ohmi, T. (1992). A functional MOS transistor featuring gate-level weighted sum and threshold operations. IEEE Transactions on Electron Devices, 39, 1444–1455.

Miguel, J. M. A., Lopez-Martin, A. J., Acosta, L., Ramrez-Angulo, J., & Carvajal, R. G. (2011) Using floating gate and quasi-floating gate techniques for rail-to-rail tunable CMOS transconductor design. IEEE Transactions on Circuits and Systems I: Regular Papers, 58(7), 1604–1614.

Berg, Y., Tor S. Lande, & Næss, Ø. (2001). Programming floating-gate circuits with UV-activated conductances. IEEE Transactions on Circuits and Systems -II: Analog and Digital Signal Processing, 48(1), 12–19.

Berg, Y., Aunet, S., Mirmotahari, O., & Høvin, M. (2003). Novel recharge semi-floating-gate CMOS logic for multiple-valued systems. In IEEE International symposium on circuits and systems (ISCAS), Bangkok.

Berg, Y., & Mirmotahari, O. (2011). Ultra low-voltage CMOS current mirrors. Analog Integrated Circuits and Signal Processing, 68(2), 219–232.

Berg, Y. (2011). Novel clocked semi-floating-gate differential transconductance amplifer for ultra-low voltage analog design. In IEEE 9th International NEWCAS conference, Bordeaux, pp. 285–288.

Berg, Y. (2010). Novel ultra low voltage transconductance amplifier. In IEEE International symposium on circuits and systems (ISCAS), Paris, France, pp. 1244–1247.

Berg, Y. (2010). Novel ultra low voltage semi floating-gate passband transconductance amplifier. In 15th IEEE Mediterranean electrotechnical conference (MELECON), Malta, pp. 286–289.

Enz, C. C., & Temes, G. C. (1996). Circuit techniques for reducing the effects of Op-Amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proceedings of the IEEE, 84(11), 1584–1614.

More, S., Fulde, M., Chouard, F., & Schmitt-Landsiedel, D. (2011). Reducing impact of degradation on analog circuits by chopper stabilization and autozeroing. 12th International symposium on quality electronics design, pp. 1–6.

Machowski, W., & Jasielski, J. (2011). Low voltage, low power analog multipliers based on CMOS inverters, MIXDES 2011. In 18th International conference mixed design of integrated circuits and systems, Gliwice, Poland, pp. 352–357.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Berg, Y. Ultra low-voltage CMOS transconductance amplifiers. Analog Integr Circ Sig Process 73, 683–692 (2012). https://doi.org/10.1007/s10470-012-9924-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-012-9924-6