Abstract

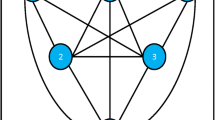

Interconnection topology inside chip multiprocessor acts as fundamental role in communication locality. Considering compiler optimization data locality has been an inmost hypothesis in the high performance computing. Conversely, data locality sphere has several troubles when its degree of dimension is two or higher. In mesh network of two dimensions, each core is connected with its four neighbors. The data locality can potentially be exploited in two dimensions considering the specified processor’s perspective. A Triplet-Based Hierarchical Interconnection Network (TBHIN) has straightforward topology and fractal attribute for chip multiprocessor. In this paper, a static (no contention) performance analysis of TBHIN and 2-D mesh is presented, based on the premise of locality in communication. The dynamic (contention) software simulation of TBHIN shows that the stronger the locality in communication, the lower the delay of the communication.

Chapter PDF

Similar content being viewed by others

References

Codrescu, L., Wills, D.S.: Architecture of the Atlas chip-multiprocessor: dynamically parallelizing irregular applications. In: International Conference on Computer Design, ICCD 1999 (2002), 10.1109/ICCD.1999.808577

Kumar, R., Zyuban, V., Tullsen, D.M.: Interconnections in Multi-Core Architectures: Understanding Mechanisms, Overheads and Scaling. In: International Symposium on Computer Architecture, ISCA, pp. 408–419 (2005), doi:10.1109/ISCA.2005.34

Ahmed, A., Jones, A.K., Rami, M.: Codesign of NoC and Cache Organization for Reducing Access Latency in Chip Multiprocessors. IEEE Transactions on Parallel and Distributed Systems 23 (2012)

Dally, W.J., Towles, B.: Route Packets, Not Wires: On-Chip Interconnection Networks. In: Proceedings of the 38th Design Automation Conference, pp. 681–689 (2001)

Ching, D., Schaumont, P., Verbauwhede, I.: Integrated Modeling and Generation of a Configurable network-on-chip. In: Proceedings 18th International Parallel and Distributed Processing Symposium, p. 139 (2004)

Kumar, S., Jantsch, A., Soininen, J.-P., Forsell, M., Millberg, M., Oberg, J., Tiensyrja, K., Hemani, A.: A network on chip architecture and design methodology. In: Proc. Symposium on VLSI, pp. 117–124 (April 2002)

Feng, S., Weixing, J., Baojun, Q., Bin, L., Haroon, R.: A Triplet Based Computer Architecture Supporting Parallel Object Computing. In: Proceedings of the Eighteenth International Conference on ASAP, pp. 192–197 (July 2007)

Baojun, Q., Feng, S., Weixing, J.: A New Routing Algorithm in Triple-based Hierarchical Interconnection Network. In: The First International Conference on Innovative Computing, Information and Control, pp. 725–728. IEEE, Beijing (2006)

Bin, L., Zhi-Chen, T., Yu-Jin, G.: Triplet-based architecture and its process migration mechanism. In: 2009 International Conference on Machine Learning and Cybernetics, vol. 5 (2009), 10.1109/ICMLC.2009.5212644

Dong, Y., Wang, D., Zheng, W.: Exact Computation Of The Mean Minimal Path Length of N-MESH and N-TORUS. Journal of Software 20(4) (1997)

Weixing, J., Feng, S., Baojun, Q., Liu, B.: Study on an interconnection network for complex embedded systems. Chinese High Technology Letters 17(9), 886–890 (2007)

Dandamudi, S., Eager, D.: Hierarchical Interconnection Networks for Multicomputer Systems. IEEE Transactions on Computers 39(6), 786–797 (1990)

Min Kyu, J., Doe Hyun, Y., Dam, S., Mike, S., Ikhwan, L., Mattan, E.: Balancing DRAM Locality and Parallelism in Shared Memory CMP Systems. In: 2012 IEEE 18th International Symposium on High Performance Computer Architecture, HPCA (2012)

Kandemir, M.: Data locality enhancement for CMPs. In: Proc. ICCAD (2007)

Bikshandi, G., Jia, G., Daniel, H.: Programming for parallelism and locality with hierarchically tiled arrays. In: Proc. PPOPP (2006)

Xavier, V., Nerina, B., Josep, L., Antonio, G.: A fast and accurate framework to analyze and optimize cache memory behavior. In: TOPLAS 2004 (2004)

Abhinav, B., Laxmikant, V.K.: Benefits of Topology Aware Mapping For Mesh Interconnects. Parallel Processing Letters (April 16, 2010)

Abhinav, B., Eric, B., Laxmikant, V.K.: Optimizing communication for Charm++ applications by reducing network contention. Concurrency and Computation: Practice and Experience (2009); 00-17 Prepared using cpeauth.cls (Version: 2002/09/19 v2.02)

Zhang, C., Yutao, Z., Youfeng, W.: A hierarchical model of data locality. In: Proc. POPL (2006)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2012 IFIP International Federation for Information Processing

About this paper

Cite this paper

Talpur, S., Shi, F., Wang, Y. (2012). Communication Locality Analysis of Triplet-Based Hierarchical Interconnection Network in Chip Multiprocessor. In: Park, J.J., Zomaya, A., Yeo, SS., Sahni, S. (eds) Network and Parallel Computing. NPC 2012. Lecture Notes in Computer Science, vol 7513. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-35606-3_4

Download citation

DOI: https://doi.org/10.1007/978-3-642-35606-3_4

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-35605-6

Online ISBN: 978-3-642-35606-3

eBook Packages: Computer ScienceComputer Science (R0)