Abstract

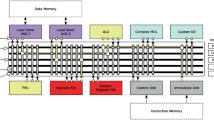

This paper documents the development, implementation, and verification of a RISC microprocessor using the functional hardware description language Lava. Basic methods to describe hardware in Lava are introduced and extended towards implementation of instruction set and pipeline structure. Synthesis results for Cyclone II FPGA are presented and compared against a traditional VHDL-based design flow. A loosely coupled coprocessor interface used to accelerate application-specific code is introduced. To authors’ best knowledge it is the first attempt to describe a complete von Neumann machine in Lava. Project experiences as well as directions for further improvement of Lava are summarized.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Sheeran, M.: μFP, an algebraic VLSI Design Language, PhD thesis, Oxford (1983)

Jones, G., Sheeran, M.: Circuit Design in Ruby. In: Formal Methods for VLSI Design, pp. 13–70. Elsevier Science Publishers, Amsterdam (1994)

Grundy, J., Melham, T., O’Leary, J.: A Reflective Functional Language for Hardware Design and Theorem Proving. J. of Functional Programming 16(2), 157–196 (2006)

Sheeran, M.: Hardware Design and Functional Programming: a Perfect Match. J. of Universal Computer Science 11(7), 1135–1158 (2005)

Singh, S., James-Roxby, P.: Lava and JBits: From HDL to Bitstream in Seconds. In: Proc. of FCCM, pp. 91–100 (2001)

Naylor, M., Runcimann, C.: The Reduceron Research Project, 2008–2010, http://www.cs.york.ac.uk/fp/reduceron/

Naylor, M.: Hardware-Assisted and Target-Directed Evaluation of Functional Programs, PhD thesis, University of York (2008)

Bjeese, P., Claessen, K., Sheeran, M., Singh, S.: Lava: Hardware Design in Haskell. In: Proc. of ICFP, ACM SIGPLAN (1998)

Claessen, K.: An Embedded Language Approach to Hardware Description and Verification, Lic. thesis, Chalmers University of Technology (August 2000)

Claessen, K., Sands, D.: Observable Sharing for Functional Circuit Description. In: Thiagarajan, P.S., Yap, R.H.C. (eds.) ASIAN 1999. LNCS, vol. 1742, pp. 62–73. Springer, Heidelberg (1999)

Rhoads, S.: Plasma — most MIPS I(TM) opcodes, 2001–2010, http://plasmacpu.no-ip.org

Schulze, S.: Design, Implementation and Verification of a Processor with a Functional Hardware Description Language, Diplomarbeit, FH Wedel (March 2010)

Athanas, P., Silverman, H.: Processor Reconfiguration through Instruction-Set Metamorphosis. IEEE Computer 26(3), 11–18 (1993)

Razdan, R.: PRISC: Programmable Reduced Instruction Set Computers, PhD thesis, Harvard University, Cambridge, Massachusetts (May 1994)

Hauser, J., Wawrzynek, J.: Garp: A MIPS Processor with a Reconfigurable Coprocessor. In: Proc. of FCCM, pp. 24–33 (1997)

Moscu Panainte, E., Bertels, K.L.M., Vassiliadis, S.: The Molen Compiler for Reconfigurable Processors. ACM TECS 6(1) (February 2007)

Singh, S.: Xilinx Lava Hardware Description Language 1 (October 2009), http://www.raintown.org/lava

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2011 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Schulze, S., Sawitzki, S. (2011). Design, Implementation, and Verification of an Adaptable Processor in Lava HDL. In: Koch, A., Krishnamurthy, R., McAllister, J., Woods, R., El-Ghazawi, T. (eds) Reconfigurable Computing: Architectures, Tools and Applications. ARC 2011. Lecture Notes in Computer Science, vol 6578. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-19475-7_17

Download citation

DOI: https://doi.org/10.1007/978-3-642-19475-7_17

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-19474-0

Online ISBN: 978-3-642-19475-7

eBook Packages: Computer ScienceComputer Science (R0)