Abstract

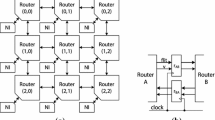

Shrinking process technology poses a challenge to network-on-chip design for high performance and energy efficient router architecture to interconnect multiple cores on a chip. Because of its importance, several router micro-architectures are proposed in the literature. In this paper, we propose a novel router architecture, congestion aware switchable cycle adaptive deflection (CASCADE) router, which dynamically reconfigures itself from single-cycle buffer-less router to two-cycle minimally-buffered router, and vice-versa, based on the router congestion level. The CASCADE router employs congestion aware cycle switching and power-gating to achieve both power and performance efficiency under varying network loads. Experimental results show that, when compared to SLIDER, the state of the art minimally buffered deflection router, the CASCADE router achieves on average 19 % power reduction and 26 % flit latency reduction with marginal area overhead.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Jose, J., et al.: DeBAR: deflection based adaptive router with minimal buffering. In: DATE 2013, pp. 1583–1588 (2013)

Nayak, B., et al.: SLIDER: smart late injection DEflection router for mesh NoCs. In: ICCD 2013, pp. 377–383 (2013)

Jonna, G.R., et al.: MinBSD: minimally buffered single-cycle deflection router. In: DATE 2014, pp. 1–4 (2014)

Dally, W., Towles, B.: Principles and Practices of Interconnection Networks. Morgan Kaufmann Publishers Inc., San Francisco (2003)

Dally, W.: Virtual-channel flow control. IEEE Trans. Parallel Distrib. Syst. 3, 194–205 (1992)

Hoskote, Y., et al.: A 5-GHz mesh interconnect for a teraflops processor. IEEE Micro 27(5), 51–61 (2007)

Taylor, M.B., et al.: Evaluation of the raw microprocessor: an exposed-wire-delay architecture for ILP and streams. In: ISCA (2004)

Gomez, C., et al.: An efficient switching technique for NoCs with reduced buffer requirements. In: ICPADS, pp. 713–720 (2008)

Hayenga, M., et al.: SCARAB: a single cycle adaptive routing and bufferless network. In: MICRO, pp. 244–254 (2009)

Chen, C.-H.O., et al.: SMART: a single-cycle reconfigurable NoC for SoC applications. In: DATE 2013, pp. 338–343 (2013)

Moscibroda, T., Mutlu, O.: A case for bufferless routing in on-chip networks. In: ISCA, pp. 196–207 (2009)

Fallin, C., et al.: CHIPPER: a low complexity bufferless deflection router. In: HPCA, pp. 144–155 (2011)

Fallin, C., et al.: MinBD: minimally-buffered deflection routing for energy-efficient interconnect. In: NOCS, pp. 1–10 (2012)

Ubal, R., et al.: Multi2sim: a simulation framework to evaluate multicore-multithreaded processors. In: SBAC-PAD, pp. 62–68 (2007)

SPEC2006 CPU benchmark suite. http://www.spec.org

Woo, S.C., et al.: The splash-2 programs: characterization and methodological considerations. In: ISCA, pp. 24–36 (1995)

Bienia, C., et al.: The parsec benchmark suite: characterization and architectural implications. In: PACT, pp. 72–81 (2008)

Nguyen, S.T., et al.: A low cost single-cycle router based on virtual output queuing for on-chip networks. In: DSD, pp. 60–67 (2010)

Kumar, A., et al.: A 4.6 Tbits/s 3.6 GHz single-cycle NoC router with a novel switch allocator in 65 nm CMOS. In: ICCD, pp. 63–70 (2007)

Nilsson, E., et al.: Load distribution with the proximity congestion awareness in a network-on-chip. In: DATE, pp. 1126–1127 (2003)

Hassan, S.M., et al.: Centralized buffer router: a low latency, low power router for high radix NOCs. In: NOCS, pp. 1–6 (2013)

Jafri, S.A.R., et al.: Adaptive flow control for robust performance and energy. In: MICRO, pp. 433–444 (2010)

Kim, G., et al.: Flexibuffer: reducing leakage power in on-chip network routers. In: DAC, pp. 936–941 (2011)

Chen, L., et al.: Power punch: towards non-blocking power-gating of noc routers. In: HPCA, pp. 378–389 (2015)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2016 Springer International Publishing Switzerland

About this paper

Cite this paper

Jonna, G.R., Thuniki, V.M., Mutyam, M. (2016). CASCADE: Congestion Aware Switchable Cycle Adaptive Deflection Router. In: Hannig, F., Cardoso, J.M.P., Pionteck, T., Fey, D., Schröder-Preikschat, W., Teich, J. (eds) Architecture of Computing Systems – ARCS 2016. ARCS 2016. Lecture Notes in Computer Science(), vol 9637. Springer, Cham. https://doi.org/10.1007/978-3-319-30695-7_3

Download citation

DOI: https://doi.org/10.1007/978-3-319-30695-7_3

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-30694-0

Online ISBN: 978-3-319-30695-7

eBook Packages: Computer ScienceComputer Science (R0)