Abstract

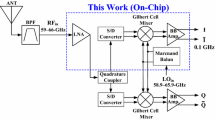

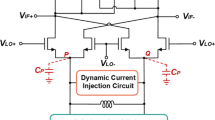

We present the design of a folded down-conversion mixer which is incorporated at the final down-conversion stage of a 60 GHz receiver. The mixer employs an ac-coupled current reuse transconductance stage. It performs well under low supply voltages, and is less sensitive to temperature variations and process spread. The mixer operates at an input radio frequency (RF) band ranging from 10.25 to 13.75 GHz, with a fixed local oscillator (LO) frequency of 12 GHz, which down-converts the RF band to an intermediate frequency (IF) band ranging from dc to 1.75 GHz. The mixer is designed in a 65 nm low power (LP) CMOS process with an active chip area of only 0.0179 mm2. At a nominal supply voltage of 1.2 V and an IF of 10 MHz, a maximum voltage conversion gain (VCG) of 9.8 dB, a double sideband noise figure (DSB-NF) of 11.6 dB, and a linearity in terms of input 1 dB compression point (P in,1dB) of −13 dBm are measured. The mixer draws a current of 5 mA from a 1.2 V supply dissipating a power of only 6 mW.

Similar content being viewed by others

References

Afshar, B., Wang, Y., Niknejad, A.M., 2008. A robust 24 mW 60 GHz receiver in 90 nm standard CMOS. IEEE Int. Conf. on Solid-State Circuits, p.182–605. [doi:10.1109/ISSCC.2008.4523117]

Amin, N.M., Wang, Z., Kuan, B., et al., 2012. 1.2 V folded down-conversion wideband mixer in 65 nm CMOS. IEEE Int. Conf. on Electron Devices and Solid-State Circuits, p.1–4. [doi:10.1109/EDSSC.2012.6482774]

Cai, D., Yang, S., Hao, Y., et al., 2013. Design of ultralow-power 60 GHz direct-conversion receivers in 65 nm CMOS. IEEE Trans. Microw. Theory Techn., 61(9):3360–3372. [doi:10.1109/TMTT.2013.2268738]

Chiou, H.K., Lin, K.C., Chen W.H., et al., 2012. A 1 V 5 GHz self-bias folded-switch mixer in 90 nm CMOS for WLAN receiver. IEEE Trans. Circ. Syst. I, 59(6):1215–1227. [doi:10.1109/TCSI.2011.2173399]

Choi, K., Shin, D.H., Yue, C.P., 2007. A 1.2 V, 5.8 mW, ultra-wideband folded mixer in 0.13 μm CMOS. IEEE Int. Symp. on Radio Frequency Integrated Circuits, p.489–492. [doi:10.1109/RFIC.2007.380930]

Darabi, H., Abidi, A.A., 2000. Noise in RF-CMOS mixers: a simple physical model. IEEE J. Solid-State Circ., 35(1):15–25. [doi:10.1109/4.818916]

Doan, C.H., Emami, S., Niknejad, A.M., et al., 2005. Millimeter-wave CMOS design. IEEE J. Solid-State Circ., 40(1):144–155. [doi:10.1109/JSSC.2004.837251]

Furuta, Y., Heima, T., Sato, H., et al., 2007. A low flickernoise direct conversion mixer in 0.13 μm CMOS with dual-mode DC offset cancellation circuits. IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, p.265–268. [doi:10.1109/SMIC.2007.322809]

Hampel, S.K., Schmitz, O., Tiebout, M., et al., 2010. Inductorless low-voltage and low-power wideband mixer for multistandard receivers. IEEE Trans. Microw. Theory Techn., 58(5):1384–1390. [doi:10.1109/TMTT.2010.2042894]

Hermann, C., Tiebout, M., Klar, H., 2005. A 0.6 V, 1.6 mW transformer based 2.5 GHz down-conversion mixer with +5.4 dB gain and −2.8 dBm IIP3 in 0.13 μm CMOS. IEEE Trans. Microw. Theory Techn., 53(2):488–495. [doi:10. 1109/TMTT.2004.840762]

Klumperink, E.A.M., Louwsma, S.M., Wienk, G.J.M., et al., 2004. A CMOS switched transconductor mixer. IEEE J. Solid-State Circ., 39(8):1231–1240. [doi:10.1109/JSSC.2004.831797]

Marcu, C., Chowdhury, D., Thakkar, C., et al., 2009. A 90 nm CMOS low-power 60 GHz transceiver with integrated baseband circuitry. IEEE J. Solid-State Circ., 44(12): 3434–3447. [doi:10.1109/JSSC.2009.2032584]

Poobuapheun, N., Chen, W.H., Boos, Z., et al., 2007. A 1.5 V 0.7–2.5 GHz CMOS quadrature demodulator for multiband direct-conversion receivers. IEEE J. Solid-State Circ., 42(8):1669–1677. [doi:10.1109/JSSC.2007.900294]

Razavi, B., 1988. RF Microelectronics. Prentice Hall, New Jersey, USA, p.17–22.

Razavi, B., 2009. Design of millimeter-wave CMOS radios: a tutorial. IEEE Trans. Circ. Syst. I, 56(1):4–16. [doi:10.1109/TCSI.2008.931648]

Safarian, A.Q., Yazdi, A., Heydari, P., 2005. Design and analysis of an ultrawide-band distributed CMOS mixer. IEEE Trans. VLSI Syst., 13(5):618–629. [doi:10.1109/TVLSI.2005.844288]

Tomkins, A., Aroca, R.A., Yamamoto, T., et al., 2009. A zero-IF 60 GHz 65 nm CMOS transceiver with direct BPSK modulation demonstrating up to 6 Gb/s data rates over a 2 m wireless link. IEEE J. Solid-State Circ., 44(8):2085–2099. [doi:10.1109/JSSC.2009.2022918]

Vecchi, F., Bozzola, S., Temporiti, E., et al., 2011. A wideband receiver for multi-Gbit/s communications in 65 nm CMOS. IEEE J. Solid-State Circ., 46(3):551–561. [doi:10.1109/JSSC.2010.2100251]

Vidojkovic, V., van der Tang, J., Leeuwenburgh, A., et al., 2005. A low voltage folded-switching mixer in 0.18 μm CMOS. IEEE J. Solid-State Circ., 40(6):1259–1264. [doi:10.1109/JSSC.2005.848034]

Wang, C., Wan, Q., 2011. A 0.18 μm CMOS low noise amplifier using a current reuse technique for 3.1–10.6 GHz UWB receivers. J. Semicond., 32(8):085002. [doi:10.1088/1674-4926/32/8/085002]

Author information

Authors and Affiliations

Corresponding author

Additional information

Project supported by the National High-Tech R&D Program (863) of China (No. 2011AA010200)

ORCID: Najam Muhammad AMIN, http://orcid.org/0000-0002-9419-0380; Zhi-gong WANG, http://orcid.org/0000-0002-9203-4683

Rights and permissions

About this article

Cite this article

Amin, N.M., Wang, Zg. & Li, Zq. Folded down-conversion mixer for a 60 GHz receiver architecture in 65-nm CMOS technology. J. Zhejiang Univ. - Sci. C 15, 1190–1199 (2014). https://doi.org/10.1631/jzus.C1400087

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/jzus.C1400087