Abstract

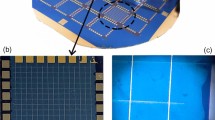

Resistive Random Access Memory (RRAM) is a novel form of non-volatile memory that is expected to play a major role in future computing and memory solutions. It has been shown that the resistance of RRAM devices can be precisely tuned by modulating switching voltages, by limiting peak current, and by adjusting the switching pulse duration. This enables the realization of novel applications such as memristive neuromorphic computing and neural network computing. The RRAM devices described in this work utilize an inert tungsten bottom electrode, hafnium oxide based active switching layer, a titanium oxygen exchange layer, and an inert titanium nitride top electrode. Linear sweep and controlled pulse (down to 10 ns) based electrical characterization of RRAM devices was performed in a 1 transistor 1 RRAM (1T1R) configuration to determine endurance, reliability, retention and threshold voltage parameters. We demonstrated endurance values above 108 cycles with an average on/off ratio of 15 and pulse voltages for set/reset operation of ±1.5V. The on-chip 1T1R structures show an excellent controllability with respect to the low and high resistive state by manipulating the peak current from 75 up to 350µA we were able to achieve 10 discrete resistive states. Our results demonstrate that the set operation (which shifts the RRAM device from the high to the low resistance state) is only dependent on the voltage of the switching pulse and the peak current limit. The reset operation, however, occurs in an analog fashion and appears to be dependent on the total energy of the applied switching pulse. Pulse energy was modulated by varying the peak voltage which resulted in a larger relative change of the RRAM device resistance.

Similar content being viewed by others

References

Y.-B. Kim, S. R. Lee, D. Lee, C. B. Lee, M. Chang, J. H. Hur, M.-J. Lee, G.-S. Park, C. J. Kim, U. Chung, I.-K. Yoo, and K. Kim, “Bi-layered RRAM with unlimited endurance and extremely uniform switching,” in VLSI Technology (VLSIT), 2011 Symposium on, 2011, pp. 52–53.

K. Beckmann, J. S. Holt, J. Capulong, Z. Alamgir, S. Lombardo, J. E. Van Nostrand, and N. C. Cady, “Endurance and Reliability of Hybrid CMOS / ReRAM for Data Storage and Encryption Applications,” 40st Annu. GOMACTech Conf., pp. 1–4, 2015.

K. Beckmann, J. Holt, J. Capulong, S. Lombardo, and N. C. Cady, “Reliability of fully-integrated nanoscale ReRAM / CMOS combinations as a function of on-wafer current control,” Integr. Reliab. Work. Final Rep. (IIRW), 2014 IEEE Int., pp. 159–162, 2014.

S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, “Nanoscale memristor device as synapse in neuromorphic systems.,”Nano Lett., vol. 10, no. 4, pp. 1297–301, Apr. 2010.

M. Hu, H. Li, Y. Chen, Q. Wu, G. S. Rose, and R. W. Linderman, “Memristor crossbar-based neuromorphic computing system: a case study.,”IEEE Trans. neural networks Learn. Syst., vol. 25, no. 10, pp. 1864–78, Oct. 2014.

G. Indiveri, B. Linares-Barranco, R. Legenstein, G. Deligeorgis, and T. Prodromakis, “Integration of nanoscale memristor synapses in neuromorphic computing architectures.,”Nanotechnology, vol. 24, no. 38, p. 384010, Sep. 2013.

H. Manem, K. Beckmann, M. Xu, R. Carroll, R. Geer, and N. C. Cady, “An extendable multi-purpose 3D neuromorphic fabric using nanoscale memristors,” in 2015 IEEE Symposium on Computational Intelligence for Security and Defense Applications (CISDA), 2015, pp. 1–8.

H. Y. Lee, Y. S. Chen, P. S. Chen, P. Y. Gu, Y. Y. Hsu, S. M. Wang, W. H. Liu, C. H. Tsai, S. S. Sheu, P. C. Chiang, W. P. Lin, C. H. Lin, W. S. Chen, F. T. Chen, C. H. Lien, and M.-J. Tsai, “Evidence and solution of over-RESET problem for HfOx based resistive memory with sub-ns switching speed and high endurance,” in 2010 International Electron Devices Meeting, 2010, pp. 19.7.1–19.7.4.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Beckmann, K., Holt, J., Manem, H. et al. Nanoscale Hafnium Oxide RRAM Devices Exhibit Pulse Dependent Behavior and Multi-level Resistance Capability. MRS Advances 1, 3355–3360 (2016). https://doi.org/10.1557/adv.2016.377

Published:

Issue Date:

DOI: https://doi.org/10.1557/adv.2016.377