Abstract

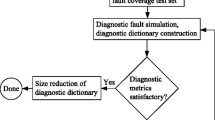

This paper suggests three techniques on non-scan DFT of sequential circuits. The proposed techniques guarantee 100% fault efficiency by using combinational ATPG tool. In all the techniques, an additional circuit called CRIS is proposed to reach unreachable states on the state register of a machine. The second and third techniques use an additional hardware DL to uniquely identify a state appearing in a state register. The design of DL is universal. Test length and hardware overhead outperform the similar approaches.

Similar content being viewed by others

References

S.T. Chakradhar, A. Balkrishnan, and V.D. Agrawal, “An Exact Algorithm for Selecting Partial Scan Flip Flops,” in Proc. of Design Automation Conference, 1994, pp. 81-86.

V. Chickermane, E.M. Rudnick, P. Banerjee, and J.H. Patel, “Non-Scan Design-for-Testability Techniques for Sequential Circuits,” in Proc. of Design Automation Conference, 1993, pp. 236-241.

D.K. Das and B.B. Bhattacharya, “Testable Design of Non-Scan Sequential Circuits Using Extra Logic,” Proc. of Asian Test Symposium, 1995, pp. 176-182.

S. Devadas and K. Keutzer, “A Unified Approach to the Synthesis of Fully Testable Sequential Machines,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 10, pp. 39-50, 1991.

H. Fujiwara, Logic Testing and Design for Testability, The MIT Press, 1985.

S. Ohtake, T. Masuzawa, and H. Fujiwara, “A Non-Scan Approach to DFT for Controllers Achieving 100% Fault Efficiency,” Journal of Electronic Testing: Theory and Applications, pp. 553-566, 2000.

I. Pomeranz and S.M. Reddy, “Static Test Compaction for Full-Scan Circuits Based on Combinational Test Sets and Non-scan Sequential Test Sequences,” in Proc. of Int'l Conf. on VLSI Design, 2003, pp. 335-340.

D. Xiang, S. Gu, and H. Fujiwara, “Non-Scan Design for Testability Based on Fault Oriented Conflict Analysis,” Proc. of Asian Test Symposium, 2002, pp. 86-91.

S. Yang, “Logic Synthesis and Optimization Benchmarks User Guide,” Technical Report 1991-IWLS-UG Saeyang, Microelectronics Center of North Carolina.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Das, D.K., Ohtake, S. & Fujiwara, H. New Non-Scan DFT Techniques to Achieve 100% Fault Efficiency. Journal of Electronic Testing 20, 315–323 (2004). https://doi.org/10.1023/B:JETT.0000029464.22206.0c

Issue Date:

DOI: https://doi.org/10.1023/B:JETT.0000029464.22206.0c