Abstract

Influences of source and drain recess structures on SiGe epitaxy growth, SiGe step height, facet formation, ID,sat and resistance performance are investigated. Growth rate of SiGe height increases with decreased recess width at a fixed depth of 62 nm. Under a fixed recess width of 96.3 nm, the deeper the recess, the higher the growth rate of SiGe height. An increase in the depth/width ratio of the recessed Si geometry may promote SiGe {001} growth. Upon the recess, SiGe step height is influenced by the initial SiGe orientation. A longer {001} facet of SiGe initial orientation causes a higher growth rate of SiGe step height. Higher IDsat and lower resistance can be achieved by increasing SiGe volume with wider recess width, deeper recess depth, and higher SiGe step height.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

In order to enhance the performance of device speed, selective epitaxial growth (SEG) of SiGe was implanted in the recessed source and drain to provide lateral compressive strain and to increase carrier mobility [2].The lateral compressive strain is due to the lattice mismatch between silicon and germanium atoms, which provides an approximately 2 GPa compressive stress near the interface when germanium content is about 20% [2]. Compressive strain increases with increasing SiGe volume by silicon recess depth, width, and SiGe step height. Higher SiGe volume results in higher strain fields, and thus higher drive current [3,4,5]. A major challenge to the embedded source and drain SiGe stressor is the pattern dependent deposition [6,7,8]. According to the kinetic gas model, different recess environment or structures may lead to dramatic influence that species are attracted by dangling bonds and cause different SEG growth rate [8]. The SiGe volume is influenced by the facets driven by growth rate anisotropy in different orientations and sidewall material [9]. The relationship between the growth rates of different SiGe facets and sidewall material are R001 > R112 > R119 > R018 > R113 > R110 > R111 and Rsi > Rnitride > Roxide, respectively [10,11,12].

In this paper, the effects of silicon recess geometry and SiGe step height on SiGe epitaxy growth, SiGe facet formation and device performance in a SiGe process-induced strained silicon device are investigated. This result indicates that different depth/width (D/W) ratio in U-sharp recess can result in different levels of influence in device performance. This paper could provide useful information when embedded SiGe in recessed source and drain area is used for enhancing MOSFET performance.

Experiment

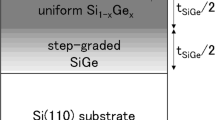

A commercially available reduced-pressure chemical vapor deposition tool was used for the selective epitaxial growth (SEG) of Si80Ge20 on the U-shape Si recessed source and drain regions prepared by using reactive-ion etching (RIE) with (100) silicon wafers. As shown in Fig. 1, various recess width and depth samples are prepared for this study. The reactor system has upper and lower lamp-heating modules with optical pyrometer temperature sensors. SiCl2H2 and diluted GeH4 (20%) are the source gases for the SiGe epitaxial growth and H2 is used as the carrier gas. The deposition temperature ranges from 600 to 800 °C at a deposition pressure of 10–20 Torr using 20 sccm SiCl2H2, 10 sccm GeH4, and 300 sccm H2 flow.

In order to observe the facet formation, a 3-s silicon marker deposition is inserted after a 27-s SiGe deposition. Under the above described deposition conditions, thickness (or height) of the SiGe layer is measured from the cross-sectional image taken from a transmission electron microscopy (TEM). Secondary ion mass spectrometry and high resolution X-ray diffractometer (HRXRD) are used to measure the germanium atomic content while the stain of SiGe layer is measured using nanobeam electron diffraction (NBD) technique. Finally, the device parameters are tested to analyze the electrical response of the different conditions.

Results and discussion

Under a fixed depth of 62 nm, smaller width leads to decreased volume of the recess region. Figure 2 shows that SiGe height (measured after four deposition cycles) increases with decreased recess width. And the deeper the recess, the higher the SiGe height for a fixed recess width of 96.3 nm as is shown in Fig. 3.

For better understanding, SiGe height is plotted against the recess depth/width (D/W) ratio as shown in Fig. 4. It indicates that SiGe height increases with recess D/W ratio. The growth rate (R) of SiGe height at different geometry can be explained by the facet. Figure 5 shows the cross-sectional TEM images of the morphology of the SiGe layers deposited in between Si sidewalls with various recess D/W ratios. The relationship between SiGe growth rates on different Si facets is R111 < R113 < R001.

In Fig. 5a, the D/W ratio is 0.61 and SiGe height is 48.1 nm, the length of the {111} and {113} facets are 20.5 and 20.5 nm, respectively. In Fig. 5b, the D/W ratio is 0.64 and SiGe height is 50.4 nm, the length of the {111} and {113} facets are 15.8 and 15.4 nm, respectively. As a result, a high D/W ratio has lower influence on {111} and {113} facets, which is beneficial to the SiGe height {001} facet growth.

Unlike silicon sidewalls, the top sidewalls of the recess are nitride films which cannot grow SiGe film. The growth rate of SiGe step height is influenced by initial {001} SiGe facet length (measured the fifth Si marker). In Fig. 6, the step height of cycle five to six (above the recess) increases with longer initial {001} SiGe facet length. Figure 7 shows the cross-sectional TEM images of the morphology of the SiGe step height deposited in between nitride sidewalls with long and short initial {001} SiGe facet length. In Fig. 7a, the initial {001} SiGe facet length is 66 nm and the step height of cycle 5 to cycle 6 is 11.4 nm. In Fig. 7b, the initial {001} SiGe facet length is 39 nm and the step height of cycle 5 to cycle 6 is 7.8 nm. The initial {001} SiGe facet length influence the growth rate of step height.

Figure 8 shows the TEM image of SiGe film grown on a blanket wafer without a faceting effect. The one cycle of SiGe step height is 12.3 nm, which is higher than the recessed source and drain regions.

The strain, measured by NBD technique, on silicon walls caused by the SiGe film deposited in the recess region (D/W ratio 0.63) is shown in Fig. 9. The strain on silicon walls is – 0.5% while the average strain of the SiGe film itself is + 1.0%. It indicates that the SiGe film provides 1.5% compress strain to the silicon channel.

The impacts of the recess width and recess depth on the drive current and resistance are given in Figs. 10, 11, 12, 13. In Figs. 10 and 11, a wider recess width has a higher drive current and lower resistance under a fixed depth of 62 nm. According to the result of strain simulation about advanced sigma-shape recessed structures, there are two key structure factors affect device’s performance. One is the distance between the sigma-shape recess and its channel region; another is tip depth [13]. In simple U-shape recess structure, only the distance between the U-sharp recess and its channel region is significant in structure’s influence. Larger SiGe volume (wider U-sharp recess width) and shorter channel to recess distance both lead to higher strain in the channel region and better device performance. In Figs. 12 and 13, a deeper recess has a higher drive current and lower resistance under a fixed recess width of 96.3 nm. They suggest that larger SiGe volume in the recessed source and drain regions could provide higher compressive stress and lower resistance to the transistor channel and result in higher IDsat.

Conclusions

The influences of recess width, recess depth, and orientation effects on the step height of SiGe epitaxy are investigated. Based on these results, recess depth/width (D/W) ratio plays an important role in facet formation. It also influences the SiGe growth in the silicon recessed region. Higher D/W ratio has a higher SiGe step height. SiGe step height depends on the initial {001} SiGe facet length above the recess, in which a longer initial length has a higher SiGe sf SiGe epitaxy in the recessed source and drain regions provides higher compressive strain to the channel and increases the carrier mobility for enhancing transistor performance. Hence drive current increases and resistance decreases with increased recess width, recess depth, and SiGe step height.

References

Ang, K., Chui, K.: Lattice strain analysis of transistor structures with silicon-germanium and silicon-carbon source/drain stressors. Appl. Phys. Lett. 86, 093102 (2005)

Moroz, V., Eneman, G., Verheyen, P., Nouri, F., Washington, L., Smith, L, Jurczak, M., Pramanik, D., Xu, X.: The impact of layout on stress-enhanced transistor performance. SISPAD, pp. 143–146 (2005)

Flachowsky, S., Iiigen, R., Hermann, T., Klix, W., Stenzel, R.: Detailed simulation study of embedded SiGe and Si: C source/drain stressors in nanoscaled silicon on insulator metal oxide semiconductor field effect transistors. J. Vac. Sci. Technol. B 28(1), C1G12 (2010)

Donaton, R.A., Chidambarrao, D., Johnsion, J., Chang, P., Liu, Y., Henson, W.K., Holt, J., Li, X., Li, J., Domenicucci, A., Madan, A., Rim, K., Wann, C.: Design and fabrication of MOSFETs with a reverse embedded SiGe (Rev. e-SiGe) structure. IEDM Tech. Dig., pp. 1–4 (2006)

Rim, K.: Scaling of strain-induced mobility enhancements in advanced CMOS technology. ICSICT 2008, pp. 105–108 (2008)

Hållstedta, J., Kolahdouz, M., Ghandi, R., Radamson, H.H.: Pattern dependency in selective epitaxy of B-doped SiGe layers for advanced metal oxide semiconductor field effect transistors. J. Appl. Phys. 103, 054907 (2008)

Kolahdouz, M., Hållstedt, J., Khatibi, A., Östling, M., Wise, R., Riley, D.J., Radamson, H.: Comprehensive evaluation and study of pattern dependency behavior in selective epitaxial growth of B-doped SiGe layers. IEEE Trans. Nanotechnol. 8(3), 291–297 (2009)

Wang, G.L., Moeen, M., Abedin, A., Kolahdouz, M., Luo, J., Qin, C.L., Zhu, H.L., Yan, J., Yin, H.Z., Li, J.F., Zhao, C., Radamson, H.H.: Optimization of SiGe selective epitaxy for source/drain engineering in 22 nm node complementary metal-oxide semiconductor (CMOS). J. Appl. Phys. 114, 123511 (2013)

Dutartre, D., Talbot, A., Loubet, N.: Facet propagation in Si and SiGe epitaxy or etching. ECS Trans. 3(7), 473–487 (2006)

Vescan, L., Grimin, K., Dieker, C.: Facet investigation in selective epitaxial growth of Si ans SiGe on (001) Si for optoelectronic device. J. Vac. Sci. Technol. B 16(3), 1549–1554 (1998)

Drowley, C.I., Reid, G.A., Hull, R.: Model for facet and sidewall defect formation during selective epitaxial growth of (001) silicon. Appl. Phys. Lett. 52, 546–549 (1988)

Xiang, Q., Li, S., Wang, D., Sakamoto, K., Wang, K.L., U’Ren, G., Goorskye, M.: Sidewall faceting and inter-facet mass transport in selectively grown epitaxial layers on SiO2-masked Si(1 1 0) substrates. J. Cryst. Growth 175, 469–472 (1997)

Qin, C., Yin, H., Wang, G., Hong, P., Ma, X., Cui, H., Yihong, L., Meng, L., Yin, H., Zhong, H., Yan, J., Zhu, H., Qiuxia, X., Li, J., Zhao, C., Radamson, H.H.: Study of sigma-shaped source/drain recesses for embedded-SiGe pMOSFETs. Microelectron. Eng. 181, 22–28 (2017)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Hong, MH., Perng, DC. Effects on selective epitaxial growth of strained-SiGe p-MOSFETs on various (001) Si recess structures. J Theor Appl Phys 11, 313–317 (2017). https://doi.org/10.1007/s40094-018-0272-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40094-018-0272-5