Abstract

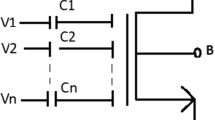

Great attention is paid to develop the nanotechnology fabrication techniques, but few attempts were done to develop special design techniques for the emerging nanotechnologies. In this paper, a new design approach for the multi-input XOR suitable for nanotechnologies is presented. This approach uses the multi-input majority function as a building block. The proposed method causes significant improvement in the gate level. The proposed design approach is deployed to CNFET 5-input and 7-input XOR circuit. The results show good improvements in the speed and number of devices.

Similar content being viewed by others

References

Lin, K.-J.; Wu, C.-W.: A low-cost realization of multiple-input exclusive-OR gates. In: ASIC Conference and Exhibit, 1995, Proceedings of the Eighth Annual IEEE International, pp. 307–310 (18–22 Sept 1995). doi:10.1109/ASIC.1995.580737

Hsiao, S.-F.; Wen, C.-S.; Tsai, M.-Y.; Chen, M.-C.: Automatic generation of high-performance multiple-input XOR/XNOR circuits and its application in Advanced Encryption Standard (AES). In: 2010 International Symposium on Next-Generation Electronics (ISNE), pp. 77–80 (18–19 Nov. 2010). doi:10.1109/ISNE.2010.5669194

Navi K., Farazkish R., Sayedsalehi S., Rahimi M.: A new quantum-dot cellular automata full-adder. Elsevier Microelectron. J. 41, 820–826 (2010). doi:10.1016/j.mejo.2010.07.003

Rahimi, M.; Kavehei, O.; Navi, K.: A novel design for quantum-dot cellular automata cells and full-adders. J. Appl. Sci. 7, 3460–3468 (2007). arXiv:1204.2048

Sayedsalehi S., Moaiyeri M.H., Navi K.: Novel efficient adder circuits for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 8, 1769–1775 (2011). doi:10.1166/jctn.2011.1881

Sahafi, A.; Moaiyeri, M.H.; Navi, K.; Hashemipour, O.: Efficient single-electron transistor inverter-based logic circuits and memory elements. J. Comput. Theor. Nanosci. 10 (2013). doi:10.1166/jctn.2013.2824

Rehan, S.E.: An ANN majority logic gate (MLG) using single electron nano-devices. In: 2010 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp.983–986 (6–9 Dec. 2010). doi:10.1109/APCCAS.2010.5774904

Muroga S.: Threshold Logic & Its Applications. Wiley, NewYork (1971)

Feinstein, D.Y.; Thornton, M.A.: ESOP transformation to majority gates for quantum-dot cellular automata logic synthesis. In: Proceedings of the workshop on Applications of the Reed–Muller Expansion in Circuit Design and Representations and Methodology of Future Computing Technology (RMW), pp. 43-50 (May 16, 2007)

Ebbesen T.W., Ajayan P.M.: Large-scale synthesis of carbon nanotubes. Nature 358, 220–222 (1992). doi:10.1038/358220a0

Martel R., Schmidt T., Shea H.R., Hertel T., Avouris Ph.: Single- and multi-wall carbon nanotube field-effect transistors. Appl. Phys. Lett. 73(17), 2447–2449 (1998). doi:10.1063/1.122477

Martel R., Derycke V., Lavoie C., Appenzeller J., Chan K.K., Tersoff J., Avouris Ph.: Ambipolar electrical transport in semiconducting single-wall carbon nanotubes. Phys. Rev. Lett. 87, 256805 (2001). doi:10.1103/PhysRevLett.87.256805

Bradley K., Gabriel J.-C.P., Grüner G.: Flexible nanotube transistors. Nano Lett. 3, 1353–1355 (2003). doi:10.1021/nl0344864

Burghard M., Klauk H., Kern K.: Carbon-based field-effect transistors for nanoelectronics. Adv. Mater. 21, 2586–2600 (2009). doi:10.1002/adma.200803582

Sun D.-M., Liu C., Ren W.-C., Cheng H.-M.: A review of carbon nanotube- and graphene-based flexible thin-film transistors. Small 9, 1188–1205 (2013). doi:10.1002/smll.201203154

Deng J., Wong H.-S.P.: A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part I: model of the intrinsic channel region. IEEE Trans. Electron Devices 54(12), 3186–3194 (2007). doi:10.1109/TED.2007.909030

Deng J., Wong H.-S.P.: A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part II: full device model and circuit Performance Benchmarking. IEEE Trans. Electron Devices 54(12), 3195–3205 (2007). doi:10.1109/TED.2007.909043

Lin S., Kim Y.-B., Lombardi F.: Design of a ternary memory cell using CNTFETs. IEEE Trans. Nanotechnol. 11(5), 1019–1025 (2012). doi:10.1109/TNANO.2012.2211614

Moaiyeri M.H., Doostaregan A., Navi K.: Design of energy-efficient and robust ternary circuits for nanotechnology. Circuits Devices Syst. IET 5(4), 285–296 (2011). doi:10.1049/iet-cds.2010.0340

Navi, K.; Sharifi, F.; Momeni, A.; Keshavarzian, P.: Ultra High Speed CNFET Full-Adder Cell Based on Majority Gates. IEICE Transactions on Electronics, (2010). DOI:10.1587/transele.E93.C.932

Alkaldy E., Navi K., Sharifi F., Moaiyeri M.H.: An ultra high-speed (4;2) compressor with a new design approach for nanotechnology based on the multi-input majority function. J. Comput. Theor. Nanosci. 11, 1691–1696 (2014)

Kim, Y.B.; Kim, Y.-B.; Lombardi, F.: A novel design methodology to optimize the speed and power of the CNTFET circuits. In: 52nd IEEE International Midwest Symposium on Circuits and Systems, 2009 (MWSCAS ’09), pp. 1130–1133 (2–5 Aug. 2009). doi:10.1109/MWSCAS.2009.5235967

Zarhoun R., Moaiyeri M.H., Farahani S.S., Navi K.: An efficient 5-input exclusive-OR circuit based on carbon nanotube FETs. ETRI J. 36(1), 89–98 (2014)

Paul, B.C.; Fujita, S.; Okajima, M.; Lee, T.H.; Wong, H.-S.P.; Nishi, Y.: Impact of a process variation on nanowire and nanotube device performance. IEEE Tran. Electron Devices 54(9), 2369–2376 (2007)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Alkaldy, E., Navi, K. & Sharifi, F. A Novel Design Approach for Multi-input XOR Gate Using Multi-input Majority Function. Arab J Sci Eng 39, 7923–7932 (2014). https://doi.org/10.1007/s13369-014-1387-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-014-1387-x