Abstract

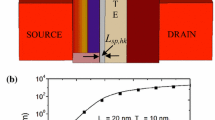

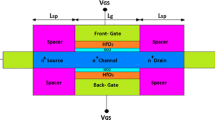

This paper shows the potential benefits of using the trigate junctionless transistor (JLT) with dual-k sidewall spacers to enhance analog/radio-frequency (RF) performance at 20-nm gate length. Simulation study shows that the source-side-only dual-k spacer (dual-kS) JLT can improve all analog/RF figures of merit (FOMs) compared with the conventional JLT structure. The dual-kS JLT shows improvement in intrinsic voltage gain (\(A_{V0}\)) by \(\sim \)44.58 %, unity-gain cutoff frequency (\(f_\mathrm{T}\)) by \(\sim \)7.67 %, and maximum oscillation frequency (\(f_\mathrm{MAX}\)) by \(\sim \)6.4 % at drain current \((I_\mathrm{ds}) = 10\,\upmu \hbox {A}/\upmu \hbox {m}\) compared with the conventional JLT structure. To justify the improvement in all analog/RF FOMs, it is also found that the dual-kS structure shows high electron velocity near the source region because of the presence of an additional electric field peak near the source region, resulting in increased electron transport efficiency and hence improved transconductance (\(g_\mathrm{m}\)). Furthermore, the dual-kS JLT shows a reduction in the electric field value near the drain end, thereby improving short-channel effects.

Similar content being viewed by others

References

Colinge, J.P., Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.M., McCarthy, B., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Colinge, J.P., Ferain, I., Kranti, A., Lee, C.W., Akhavan, N.D., Razavi, P., Yan, R., Yu, R.: Junctionless nanowire transistor: complementary metal-oxide-semiconductor without junctions. Sci. Adv. Mater. 3(3), 477–482 (2011)

Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94(5), 053511–053511-2 (2009)

Colinge, J.P., Kranti, A., Yan, R., Lee, C.W., Ferain, I., Yu, R., Dehdashti, N., Razavi, Akhavan P.: Junctionless nanowire transistor (JNT): properties and design guidelines. Solid-State Electron. 65–66, 33–37 (2011)

Colinge, J.P., Lee, C.W., Ferain, I., Akhavan, N.D., Yan, R., Razavi, P., Yu, R., Nazarov, A.N., Doria, R.T.: Reduced electric field in junctionless transistors. Appl. Phys. Lett. 96, 073510 (2010)

Rudenko, T., Nazarov, A., Yu, R., Barraud, S., Cherkaoui, K., Razavi, P., Fagas, G.: Electron mobility in heavily doped junctionless nanowire SOI MOSFETs. Microelectron. Eng. 109, 326–329 (2013)

Li, X., Han, W., Wang, H., Ma, L., Zhang, Y., et al.: Low-temperature electron mobility in heavily n-doped junctionless nanowire transistor. Appl. Phys. Lett. 102, 223507 (2013)

Parihar, M.S., Kranti, A.: Revisiting the doping requirement for low power junctionless MOSFETs. Semicond. Sci. Technol. 29, 075006 (2014)

Parihar, M.S., Ghosh, D., Kranti, A.: Ultra low power junctionless MOSFETs for subthreshold logic applications. IEEE Trans. Electron Devices 60(5), 1540–1546 (2013)

Ghosh, D., Parihar, M.S., Armstrong, G.A., Kranti, A.: High performance junctionless MOSFETs for ultra low power analog/RF applications. IEEE Electron Device Lett. 33(10), 1477–1479 (2012)

Doria, R.T., Pavanello, M.A., Trevisoli, R.D., de Souza, M., Lee, C.-W., Ferain, I., Akhavan, N.D., Yan, R., Razavi, P., Yu, R., Kranti, A., Colinge, J.P.: Junctionless multi-gate transistors for analog application. IEEE Trans. Electron Devices 58(8), 2511–2519 (2011)

Gundapaneni, S., Ganguly, S., Kottantharayil, A.: Enhanced electrostatic lntegrity of short-channel junctionless transistor with high-k spacers. IEEE Electron Device Lett. 32(10), 1325–1327 (2011)

Baruah, R.K., Paily, R.P.: Impact of high-k spacer on device performance of a junctionless transistor. J. Comput. Electronics 12, 14–19 (2012)

Baruah, R.K., Paily, R.P.: A dual-material gate junctionless transistor with high-k spacer for enhanced analog performance. IEEE Trans. Electron Devices 61(1), 123–128 (2014)

Vega, R.A., Liu, K., Liu, T.J.K.: Dopant segregated schottky source/drain double gate MOSFET design in the direct source-to-drain tunneling regime. IEEE Trans. Electron Devices 56(9), 2016–2026 (2009)

Virani, H.G., Adari, R.B.R., Kottantharayil, A.: Dual-k spacer device architecture for the improvement of performance of silicon n-channel tunnel FETs. IEEE Trans. Electron Devices 57(10), 2410–2417 (2010)

Nandi, A., Saxena, A.K., Dasgupta, S.: Design and analysis of analog performance of Dual-k spacer underlap N/P-FinFET at 12 nm gate length. IEEE Trans. Electron Devices 60(5), 1529–1535 (2013)

Pal, P.K., Kaushik, B.K., Dasgupta, S.: High-performance and robust SRAM cell based on asymmetric dual-k spacer FinFETs. IEEE Trans. Electron Devices 60(10), 3371–3377 (2013)

Saini, G., Choudhary, S.: Asymmetric dual-k spacer trigate FinFET for enhanced analog/RF performance. J. Comput. Electronics 15, 84–93 (2015)

Synopsys sentaurus design suite. (2013) [Online]. http://www.synopsys.com

Dixit, A., Kottantharayil, A., Collaert, N., Goodwin, M., Jurczak, M., Meyer, K.D.: Analysis of the parasitic S/D resistance in multiple-gate FETs. IEEE Trans. Electron Devices 52(6), 1132–1140 (2005)

Nuttinck, S., Parvais, B., Curatola, G., Mercha, A.: Double-gate Fin-FETs as a CMOS technology downscaling option: an RF perspective. IEEE Trans. Electron Devices 54(2), 279–283 (2007)

Von Arnim, K. et. al.: A low-power multi-gate FET CMOS technology with 13.9 ps inverter delay, large-scale integrated high performance digital circuits and SRAM, In: Proceeding IEEE Symposium VLSI Technology, pp. 106–107, June 2007

Lou, H., Zhang, L., Zhu, Y., Lin, X., Yang, S., He, J., et al.: A junctionless nanowire transistor with a dual-material gate. IEEE Trans. Electron Devices 59(7), 1829–1836 (2012)

Wei Long, HOu, Kuo, J.M., Chin, K.K.: Dual-material gate (DMG) field effect transistor. IEEE Trans. Electron Devices 46(5), 865–870 (1999)

Kranti, A., Armstrong, G.A.: Design and optimization of FinFETs for ultra-low-voltage analog applications. IEEE Trans. Electron Devices 54(12), 3308–3316 (2007)

Hook, T.B.: Fully depleted devices for designers: FDSOI and FinFETs. In: Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, pp. 1–7, San Jose (2012)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Saini, G., Choudhary, S. Investigation of trigate JLT with dual-k sidewall spacers for enhanced analog/RF FOMs. J Comput Electron 15, 865–873 (2016). https://doi.org/10.1007/s10825-016-0866-6

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0866-6