Abstract

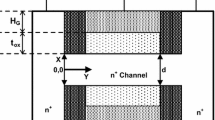

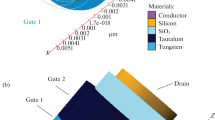

In this paper, we have analyzed the electrical characteristics of Strained Junctionless Double-Gate MOSFET (Strained JL DG MOSFET). A quantum mechanical transport approach based on non-equilibrium Green’s function (NEGF) method with the use of uncoupled mode space approach has been employed for this analysis. We have investigated the effects of high-\(\kappa \) materials as gate and spacer dielectrics on the device performance. Low OFF-state current, low DIBL, and low subthreshold slope have been obtained with increase in the gate and spacer dielectric constants. The electrical characteristics of strained JL DG MOSFET have also been compared with conventional JL DG MOSFET and Inversion Mode (IM) DG MOSFET. The results indicated that the Strained JL DG MOSFET outperforms the conventional JL and IM DG MOSFETs, yielding higher values of drain current.

Similar content being viewed by others

References

Ray, B., Mahapatra, S.: Modeling of channel potential and subthreshold slope of symmetric double-gate transistor. IEEE Trans. Electron Dev. 56, 260–266 (2009)

Kolberg, S., Borli, H., Fjeldly, T.: Modeling, verification and comparison of short-channel double gate and gate-all-around MOSFETs. Math. Comput. Simul. 79, 1107–1115 (2008)

Hosseini, R., Teimuorzadeh, N.: Simulation study of circuit performance of GAA silicon nanowire transistor and DG MOSFET. Phys. Rev. Res. Int. 3, 568–576 (2013)

Vimala, P., Balamurugan, N.: New analytical model for nanoscale tri-gate SOI MOSFETs including quantum effects. IEEE J. Electron Dev. Soc. 2, 1–7 (2014)

Kurniawan, O., FaiNg, M., Koh, W., YiLeong, Z., Li, E.: Simplified model for ballistic current-voltage characteristic in cylindrical nanowires. Microelectron. J. 41, 155–161 (2010)

Karimi, F., Fathipour, M., Hosseini, R.: A quantum mechanical transport approach to simulation of quadruple gate silicon nanowire transistor. J. Nanosci. Nanotechnol. 11, 10476–10479 (2011)

Hosseini, R., Fathipour, M., Faez, R.: Quantum simulation study of gate-all-around (GAA) silicon nanowire transistor and double gate metal oxide semiconductor field effect transistor (DG MOSFET). Int. J. Phys. Sci. 7, 5054–5061 (2012)

Koukab, A., Jazaeri, F., Sallese, J.: On performance scaling and speed of junctionless transistors. Solid-State Electron. 79, 18–21 (2013)

Jazaeri, F., Barbut, L., Sallese, J.: Modeling and design space of junctionless symmetric D MOSFETs with long channel. IEEE Trans. Electron Dev. 60, 2120–2127 (2013)

Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94, 053511–053511 (2009)

Lee, S., Kim, J., Yu, C., Park, J.: A comparative study on hot carrier effects in inversion-mode and junctionless MuGFETs. Solid-State Electron. 79, 253–257 (2013)

Ghosh, D., Parihar, M., Armstrong, G., Kranti, A.: High-performance junctionless MOSFETs for ultralow-power analog/RF applications. IEEE Trans. Electron Dev. 33, 1477–1479 (2012)

Liu, X., Wu, M., Jin, Chuai, R., Lee, J.: Simulation study on deep nanoscale short channel junctionless SOI FinFETs with triple-gate or double-gate structures. J. Comput. Electron. 13, 509–514 (2014)

Baruah, R., Paily, R.: The effect of high-k gate dielectrics on device and circuit performances of a junctionless transistor. J. Comput. Electron. 14, 492–499 (2015)

Rios, R., Cappellani, A., Armstrong, M., Budrevich, A., Gomez, H., Pai, R., Rahhalorabi, N., Kuhn, K.: Comparison of junctionless and conventional trigate transistors with Lg down to 26 nm. IEEE Trans. Electron Dev. 32, 1170–1172 (2011)

Saurabh, S., Kumar, M.: Impact of strain on drain current and threshold voltage of nanoscale double gate tunnel field effect transistor (TFET): theoretical investigation and analysis. Jpn. J. Appl. Phys. 48, 064503 (2009)

Hosseini, R., Fathipour, M., Faez, R.: Performance evaluation of source heterojunction strained channel GAA nanowire transistor. Mod. Phys. Lett. B. 26, 1250076 (2012)

Alatise, O., Kelvin, S., Olsen, S., O’Neill, A.: Improved analog performance in strained-Si MOSFETs using the thickness of the silicon-germanium strain-relaxed buffer as a design parameter. IEEE Trans. Electron Dev. 56, 3041–3048 (2009)

Kurniawan, O., Bai, P., Li, E.: Ballistic calculation of nonequilibrium Green’s function in nanoscale devices using finite element method. J. Phys. D: Appl. Phys. 42, 105109 (2009)

Luisier, M., Schenk, A., Fichtner, W.: Quantum transport in two-and three-dimensional nanoscale transistors: coupled mode effects in the nonequilibrium Green’s function formalism. J. Appl. Phys. 100, 043713 (2006)

Silvaco Int.: ATLAS Users Manual, Device simulation Software, Silvaco International, Santa Clara (2014)

Baruah, R., Paily, R.: A dual-material gate junctionless transistor with high-\(k\) spacer for enhanced analog performance. IEEE Trans. Electron Dev. 61, 123–128 (2014)

Bal, P., Ghosh, B., Mondal, P., Akram, M., Tripathi, B.M.M.: Dual material gate junctionless tunnel field effect transistor. J. Comput. Electron. 13, 230–234 (2014)

Hosseini, R., Fathipour, M., Faez, R.: A comparative study of NEGF and DDMS models in the GAA silicon nanowire transistor. Int. J. Electron. 99, 1299–1307 (2012)

Sabry, Y., Abdolkader, T., Farouk, W.F.: Uncoupled mode-space simulation validity for double gate MOSFETs. In: Proceeding of international conference on microelectronics 2007, ICM, pp. 351–354 (2007)

Alam, K., Abdullah, M.: Effects of dielectric constant on the performance of a gate all around InAs nanowire transistor. IEEE Trans. Nanotechnol. 11, 82–87 (2012)

Dastjerdy, E., Ghayour, R., Sarvari, H.: 3D quantum mechanical simulation of square nanowire MOSFETs by using NEGF method. Cent. Eur. J. Phys. 9, 472–481 (2011)

Chang, ShT: Nanoscale strained Si/SiGe heterojunction trigate field effect transistors. Jpn. J. Appl. Phys. 44, 5304 (2005)

Hosseini, R., Teimourzadeh, N., Fathipour, M.: A new source heterojunction strained channel structure for ballistic gate all around nanowire transistor. J. Comput. Electron. 13, 170–179 (2014)

Wang, J., Polizzi, E., Lundstrom, M.: A three-dimensional quantum simulation of silicon nanowire transistors with the effective mass approximation. J. Appl. Phys. 96, 2192 (2004)

Hobbs, C., Fonseca, L., Dhandapani, V., Samavedam, S., Taylor, B., Grant, J., Dip, L., Triyoso, D., Hegde, R., Gilmer, D., Garcia, R., Roan, D., Lovejoy, L., Rai, R., Hebert, L., Tseng, H., White, B., Tobin, P.: Fermi level pinning at the polySi/metal oxide interface, In: Proceeding of symposium on VLSI technology, pp. 9–10 (2003)

Baruah, R., Paily, R.: Impact of high-\(k\) spacer on device performance of a junctionless transistor. J. Comput. Electron. 12, 14–19 (2013)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Hosseini, R. Uncoupled mode space approach for analysis of nanoscale strained junctionless double-gate MOSFET. J Comput Electron 15, 787–794 (2016). https://doi.org/10.1007/s10825-016-0826-1

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0826-1